## Algorithmen im Chip-Entwurf 2

Kompaktierung, Schaltungsdarstellungen und Timing-Analyse

> Andreas Koch FG Eingebettete Systeme und ihre Anwendungen TU Darmstadt

#### Organisatorisches

- Vorgehensweise

- Anmeldebögen

- Wichtige Spalten ganz rechts: Ankreuzen

- IV 4 SWS

- Sie wollen nur das ganze Programm

- ◆ Falls Sie keinen Platz bekommen, vertagen Sie sich

- IV 4 SWS / Fallback VL 2 SWS

- ◆ Sie versuchen einen Platz zu bekommen

- ◆ Falls Sie keinen kriegen, hören Sie nur die VL

- VL 2 SWS

- Sie wollen ohnehin nur die VL hören

- Gar nix

- Sie setzen in diesem Durchgang aus

#### Übersicht

- Grundlagen von VLSI-Chips

- Kompaktierung

- Längste Pfade

- Datenstrukturen für Schaltungen

- Timing-Analyse

- Zusammenfassung

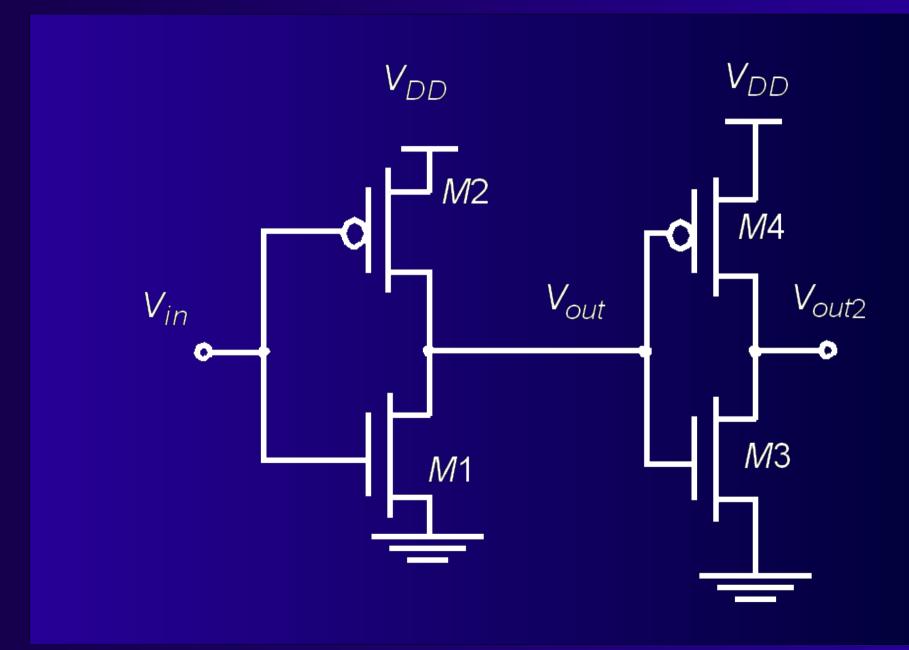

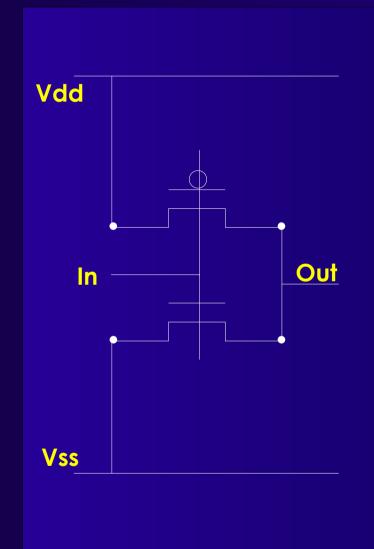

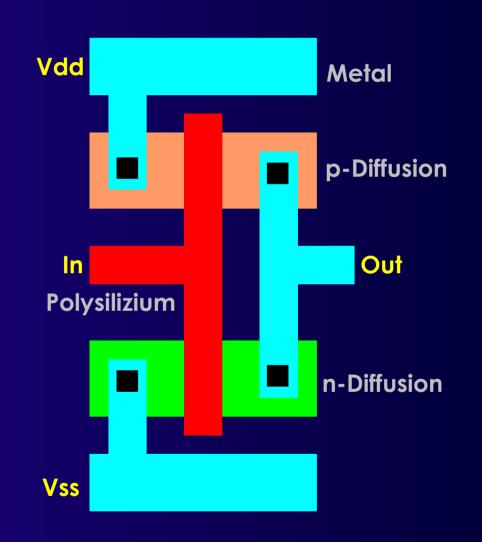

# Transistorschaltungen

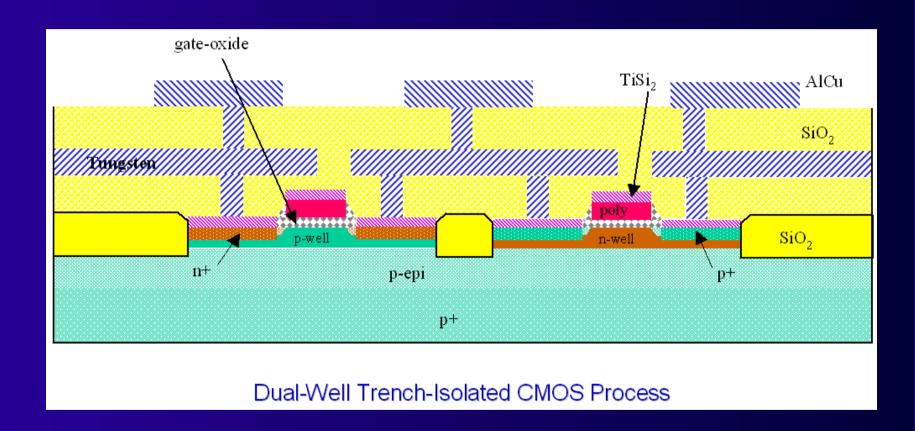

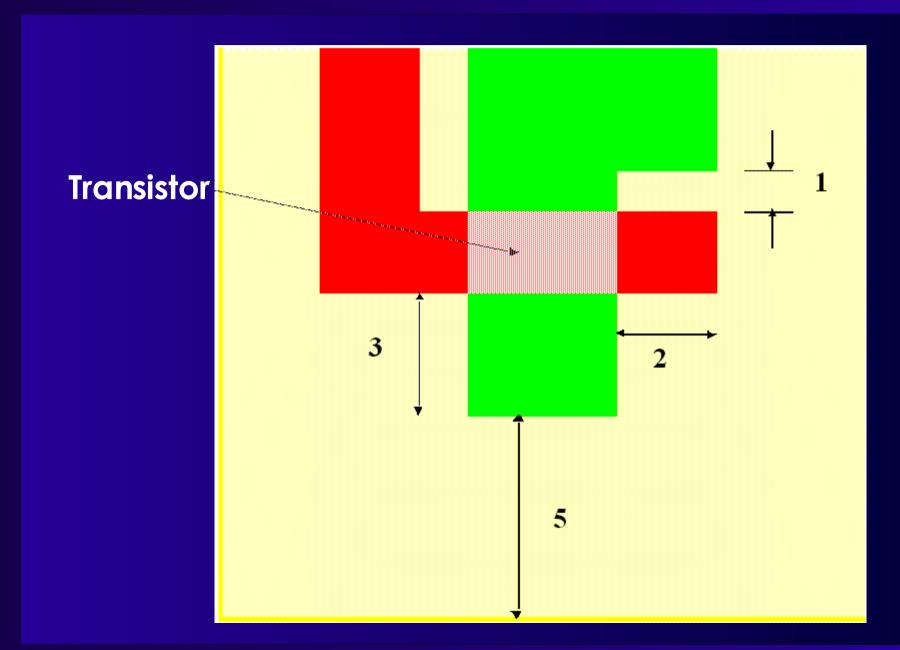

#### Seitenansicht durch Chip

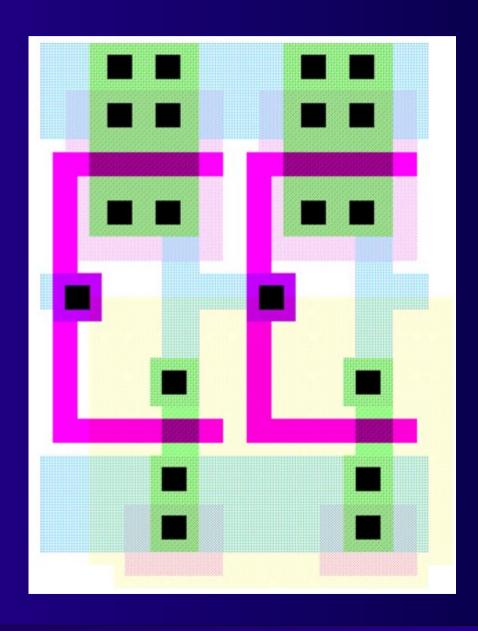

# Layout-Sicht

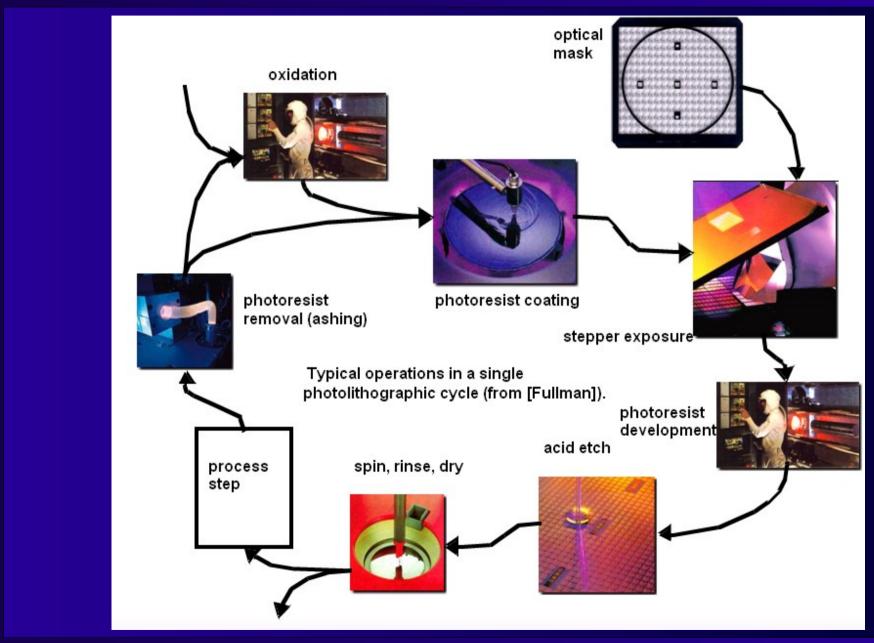

#### **Fertigung**

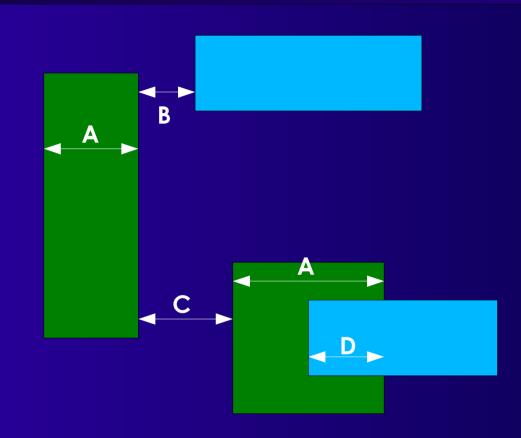

# Entwurfsregeln 1

#### Entwurfsregeln 2

- A minimale Breite

- B minimaler Abstand (L1-L2)

- C minimaler Abstand (L1-L1)

- D minimale Überlappung

- Bei ASIC-Layouts

- Grundlage f

ür erfolgreiche Fertigbarkeit

- Von "Technologen" erarbeitet

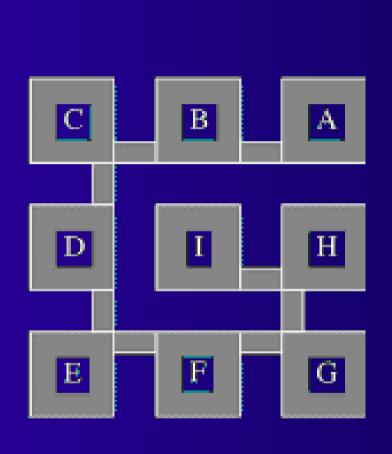

#### Symbolisches Layout

- Kein vollständiges Layout

- Keine absoluten geometrischen Angaben

- Stattdessen

- Symbole für Elemente

- ◆ Transistoren, Kontakte

- Für Elemente noch variabel

- ◆ Länge, Breite, Layer

- Einige Angaben fehlen vollständig

- n- und p-Wells (irrelevant für Funktionalität)

- Automatisch berechenbar

# Symbolisches Layout

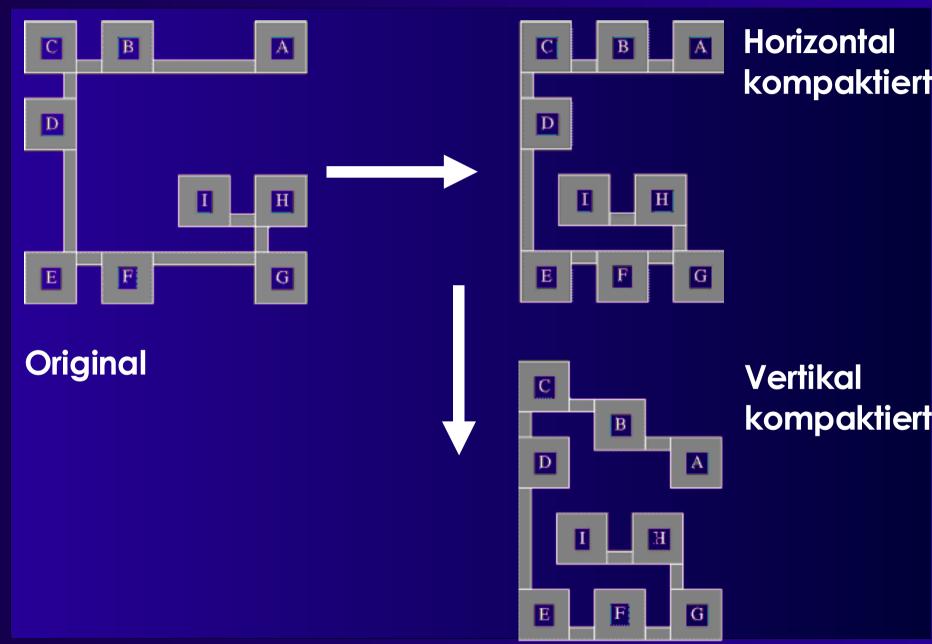

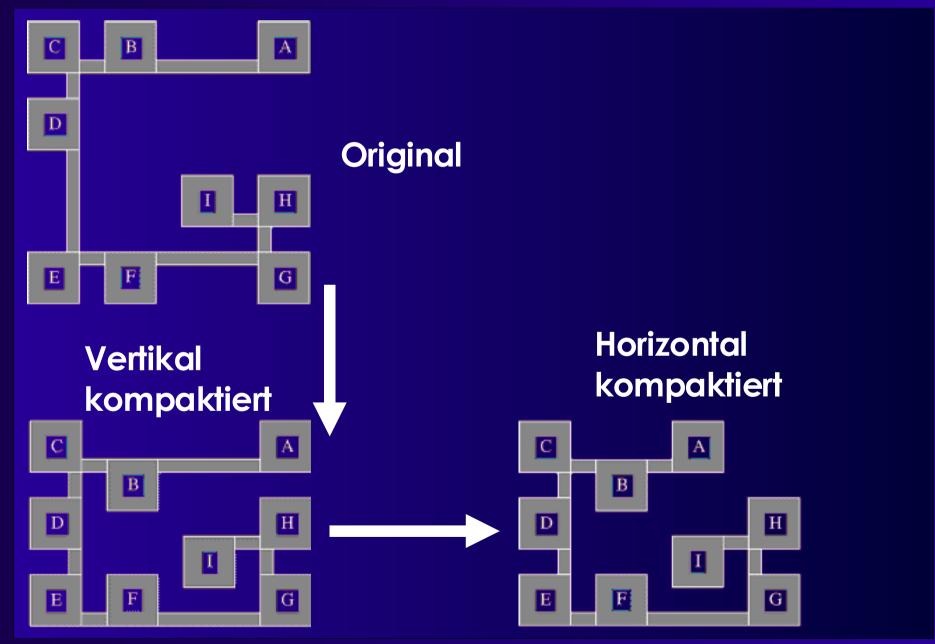

- Komprimieren/Expandieren von Layouts

- Unter Beachtung der Design-Rules

- Anwendungsgebiete

- Layout-Compilierung

- Von symbolischen in geometrische Layouts

- Flächenminimierung

- Von bestehenden Layouts

- Korrektur

- ◆ Entfernung von Entwurfsregelverletzungen

- Skalierung

- Portierung eines Layouts auf andere Technologie

#### Vorgehensweise

- Eindimensional (1D)

- Nur eine Richtung bearbeitet

- ◆ Operationen: Bewegen, Stauchen

- Oft abwechselnd in X, Y Richtungen

- Zweidimensional (2D)

- Beide Richtungen simultan bearbeiten

- Problem

- 1D ist effizient machbar, aber suboptimal

- 2D liefert optimale Lösung, ist aber NP-hart

- 2D Kompaktierung

- Optimal

- NP-vollständig

- Vorgehensweise

- Mehrfache 1D-K

- Wechselnd in H, V

- Aber: nicht optimal

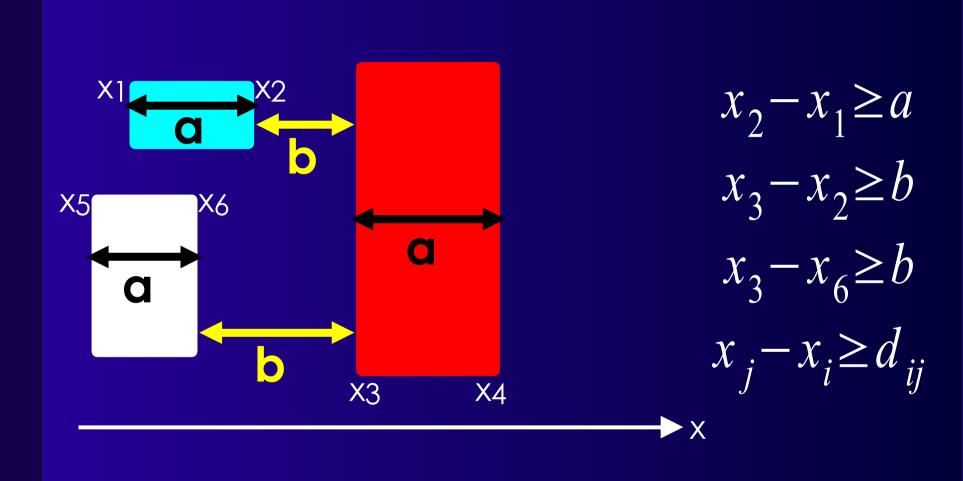

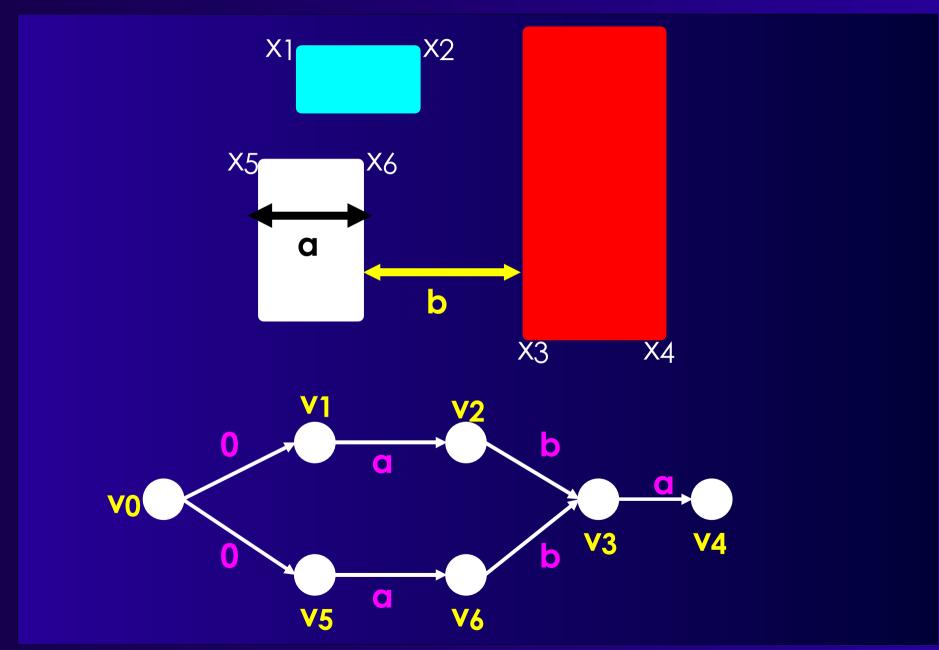

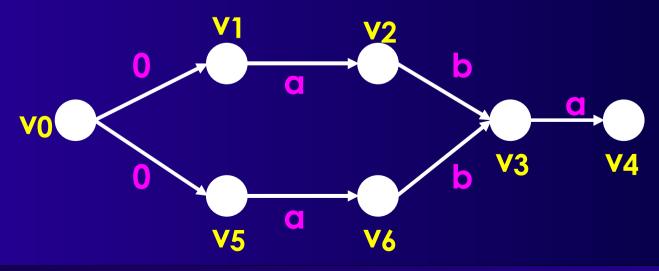

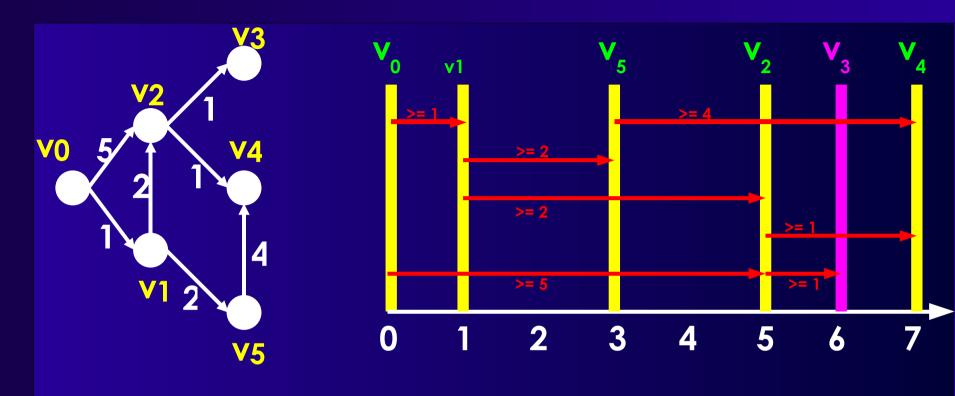

- Einschränkungsgraph G(V, E)

- Gerichtet von (vi, vj)

- Zyklenfrei

- Längster Pfad von vo zu vi

- → Minimale Koordinate von xi

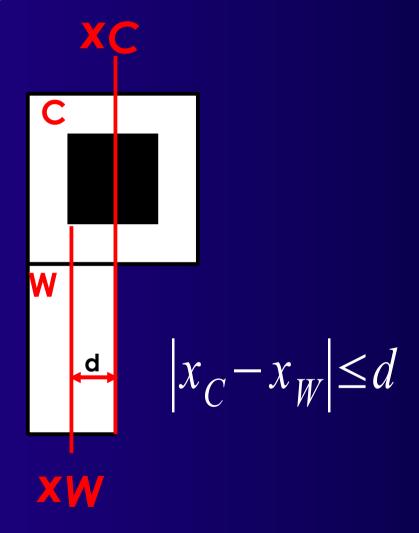

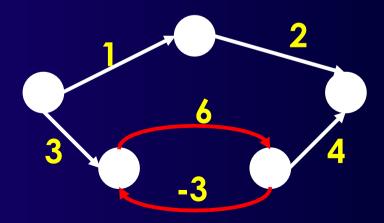

Bedingungen an maximalen Abstand

- **■** |xc-xw| ≤ d

- $x_j x_i \le c_{ij}$ ,  $c_{ij} \ge 0$

- Xi Xj ≥ -Cij

- Passende Form für Einschränkungsgraph

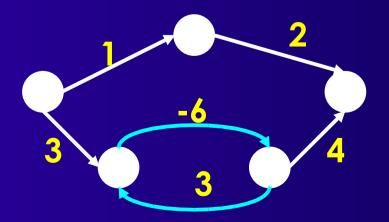

- Jetzt aber Richtung (vj, vi): Zyklen möglich!

- Aufgabe:

- Berechnung des längsten Pfades in Graphen mit Zyklen

### Längster Pfad

- Zyklenfreie Graphen

- OK, ähnlich BFS

- Graphen mit Zyklen

- Ohne positiven Zyklus: OK

- Mit positivem Zyklus: Undefiniert

- ◆ Kompaktierung: Überbeschränktes Layout

### Zyklenfreie Graphen 1

```

longest path(G) {

main() {

for (i:=1; i \le n; ++i)

for (i:=0; i \le n; ++i)

pi := vi.indegree();

x_i := 0;

longest path(G);

set Q := {v<sub>0</sub>};

while (Q \neq \emptyset) {

v_i := Q.pickany();

Q := \overline{Q \setminus \{v_i\}};

foreach (\vee_i, \vee_i) \in E \{

- Directed Acylic Graph (DAG)

xi := max(xi, xi + dii);

- Längster, gerichteter, einfacher

--p;;

Pfad (trail)

if (p_i \leq 0)

Q := Q \cup \{v_i\};

```

# Zyklenfreie Graphen 2

## Graphen mit Zyklen

- Nur mit negativen Zyklen

- Erkenne positive Zyklen

- Überbeschränkte Layouts

- Aber lokalisiere sie nicht

## Längster Pfad mit Liao-Wong 1

```

count := 0;

for (i:=1; i \le n; ++i)

X_i := -\infty;

x_0 := 0;

do {

is modified := false;

foreach (v_i, v_i) \in E_b

if (x_i < x_i + d_{ii}) \{

x_i := x_i + d_{ii}

is modified := true;

++count;

if (count > |Eb| && is_modified)

error("positive cycle!");

} while (is modified);

```

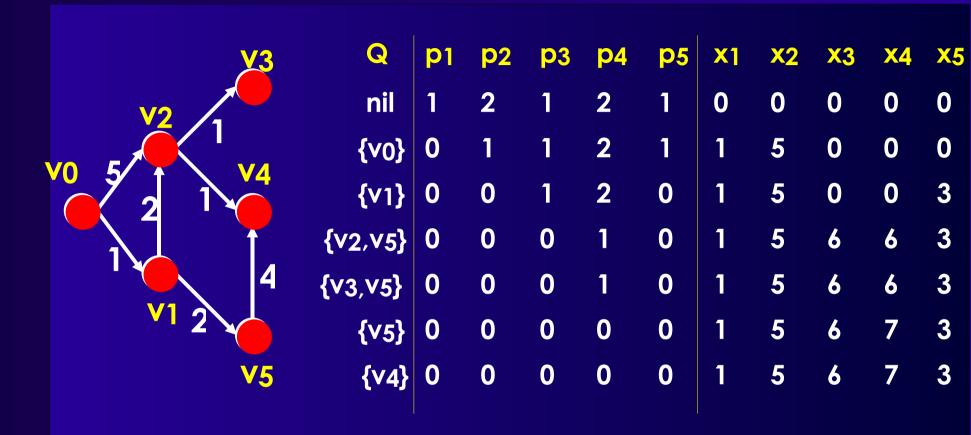

#### Idee:

- Trennen zwischen

- ◆ Ef: min. Distanz

- ◆ Eb: max. Distanz

- Erzeugen Zyklen!

- Berechne LP Gf(V, Ef)

- Korrigiere für Eb

- Schließen Zyklen

- Stabilisiert sich in |Eb|

- ◆ Jedes eb nur 1x in Pfad

- sonst überbeschränkt

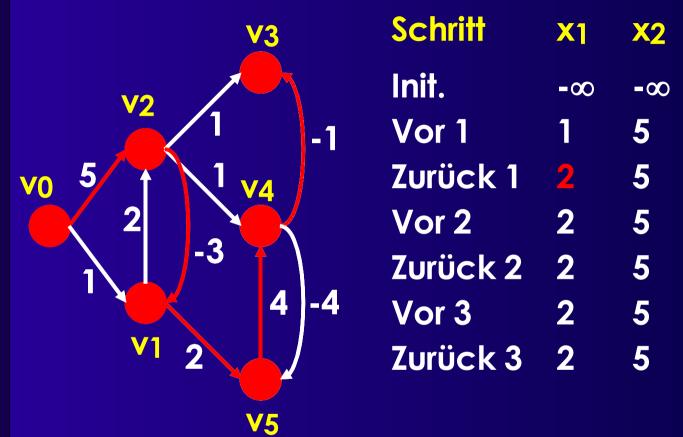

### Längster Pfad mit Liao-Wong 2

| Schritt  | <b>X</b> 1 | <b>X2</b> | <b>X3</b> | <b>X4</b> | <b>X5</b> |

|----------|------------|-----------|-----------|-----------|-----------|

| Init.    | -∞         | -∞        | -∞        | -∞        | -∞        |

| Vor 1    | 1          | 5         | 6         | 7         | 3         |

| Zurück 1 | 2          | 5         | 6         | 7         | 3         |

| Vor 2    | 2          | 5         | 6         | 8         | 4         |

| Zurück 2 | 2          | 5         | 7         | 8         | 4         |

| Vor 3    | 2          | 5         | 7         | 8         | 4         |

| Zurück 3 | 2          | 5         | 7         | 8         | 4         |

|          |            |           |           |           |           |

- Verbesserung: longest path(Gf) bemerkt Änderung

- O(|E<sub>f</sub>| x |E<sub>b</sub>|)

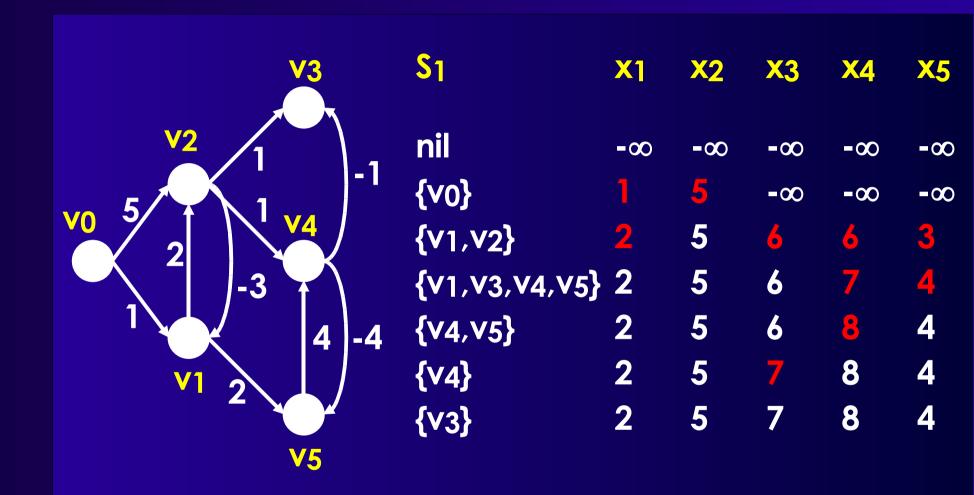

#### LP mit Bellman-Ford 1

- Kein Unterschied zwischen Ef und Eb

- Vergleichbar azyklischem LP

- Aber mehrere Durchläufe durch Graph

#### LP mit Bellman-Ford 2

```

for (i:=1; i \le n; ++i)

x_i := -\infty;

x_0 := 0;

count := 0;

S_1 := \{ v_0 \};

S_2 := \emptyset;

while (count \leq n && S_1 \neq \emptyset) {

foreach \forall i \in S_1

foreach (\vee_i, \vee_i) \in E

if (x_i < x_i + d_{ii}) \{

x_i := x_i + d_{ii};

S_2 := S_2 \cup \{v_i\};

S_1 := S_2;

S_2 := \emptyset;

++count;

if (count > n) error("positive cycle!");

```

#### Idee:

- Zwei Wellenfronten

- ◆ S<sub>1</sub>: aktuelle

- ♦ S2: nächste Iteration

- Zyklendetektion

- ♦ k-te Iteration

- ▶ LP durch k-1 Knoten

- ◆ LP hat max. n Knoten

- → Falls mehr Iterationen

- Zyklus!

- $O(n^3)$ , avg.  $O(n^{1.5})$

#### LP mit Bellman-Ford 3

# Übersicht Pfad-Algorithmen

- LP wird SP bei Multiplikation der cij mit -1

- Gerichtete zyklenfreie Graphen (DAGs)

- SP und LP lösbar in linearer Zeit

- Gerichtete Graphen mit Zyklen

- Alle Gewichte positiv

- ◆ SP in P (Dijkstra), LP ist NP-vollständig

- Alle Gewichte negativ

- ◆ LP in P, SP ist NP-vollständig

- Keine positiven Zyklen: LP in P

- Keine negativen Zyklen: SP in P

- Sonst: NP-vollständig

#### Kritische ./. Unkritische Elemente

- Layout-Breite

- Hängt nur von kritischen Elementen ab

- Unkritische Elemente: Verschiebbar

- Beeinflussen aber weitere Iterationen

### Kompaktierungsdetails

- Freie Layoutelemente

- Optimale Lösung ist 2D-Kompaktierung

- Einfügen von Jogs (Knicke in Leitungen)

- Berechnung der Einschränkungen

- Einfacher n<sup>2</sup>-Ansatz: Redundanzen

- Hierarchisches Vorgehen

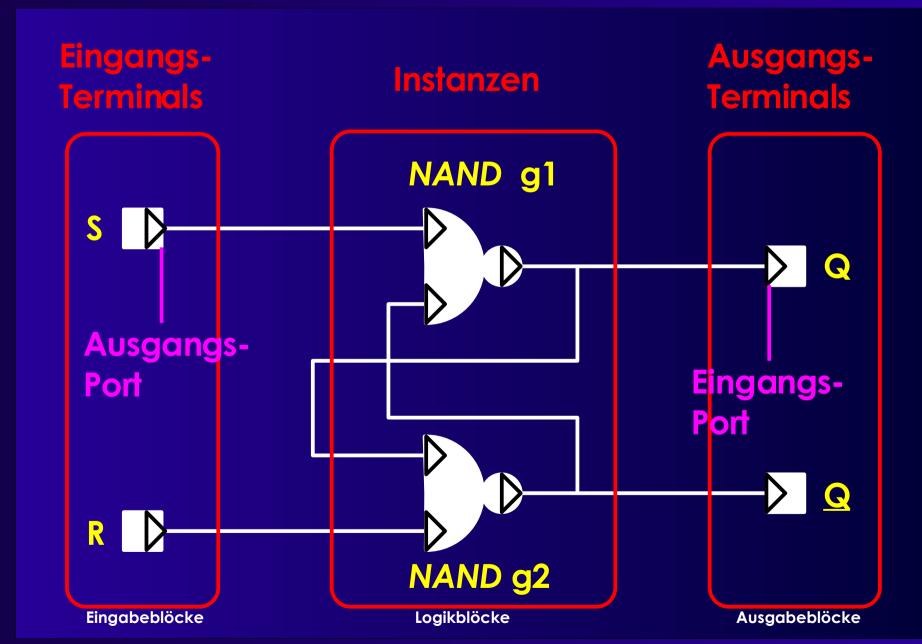

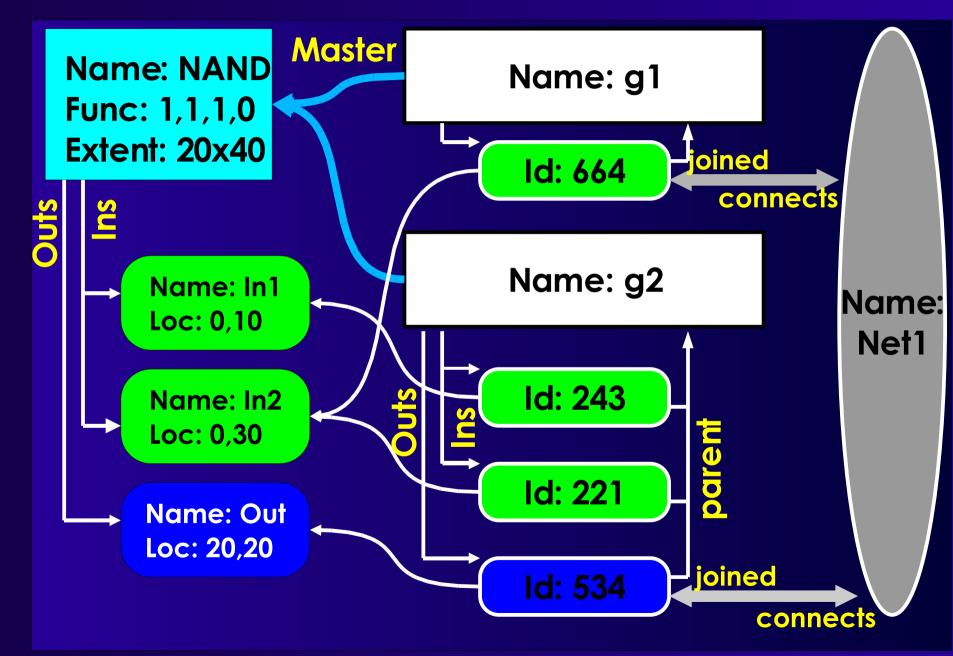

# Darstellung von Schaltungen 1

#### Darstellung von Schaltungen 2

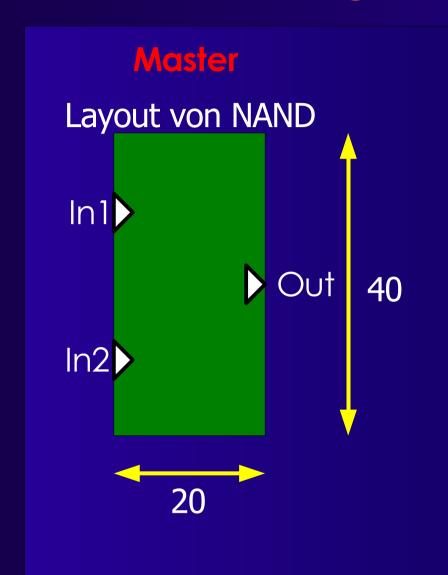

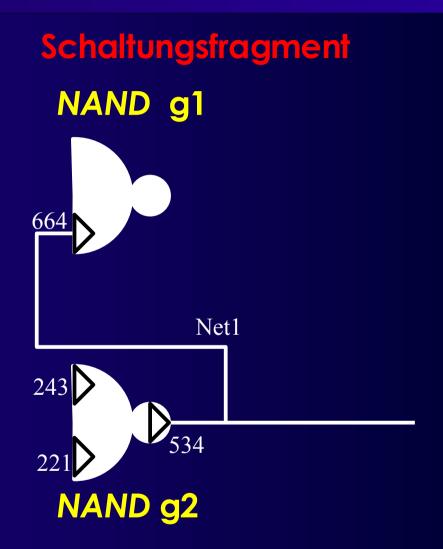

#### Instanz oder Zelle

- Ein Auftreten einer Master-Zelle

- Speichert Instanz-spezifische Eigenschaften

- ◆ z.B. Name

#### Master-Zelle

- Speichert Eigenschaften aller Instanzen

- ◆ z.B. Funktion, Ports, Layout, ...

#### Netz

- Verbindung von mehreren Ports

- Port

- Anschlusspunkt von Leitung an Zelle

- I.d.R. nicht untereinander austauschbar

- Hierarchie: Terminals werden zu Ports

#### Darstellung von Schaltungen 3

```

class cell master {

class port master {

String name;

String name;

truth table func;

Point location;

Rect extent;

set<port master> ins, outs;

};

class port {

port master master;

class cell {

String id;

cell master master;

cell parent;

String name;

net connects;

set<port> ins, outs;

class net {

String name;

set<port> joined;

```

# Darstellung von Schaltungen 4

# Darstellung von Schaltungen 5

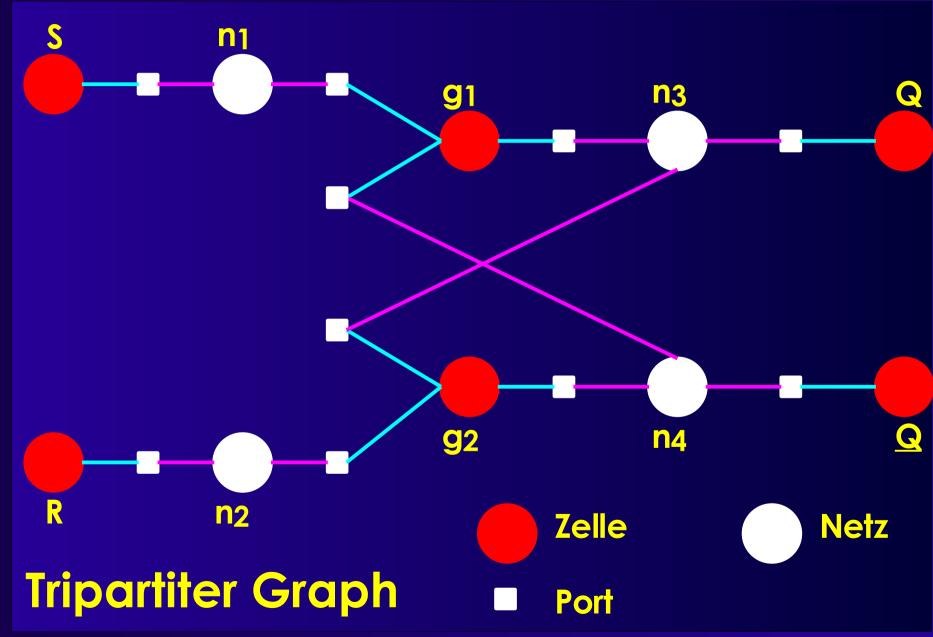

# Schaltungen als Graphen 1

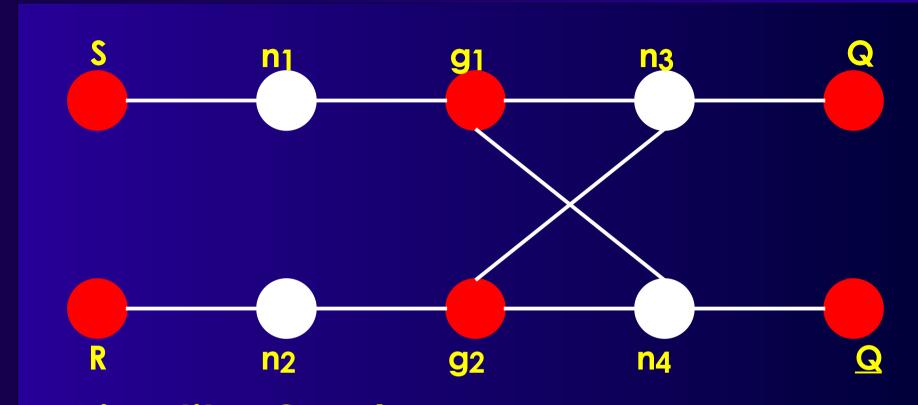

# Schaltungen als Graphen 2

- Bipartiter Graph

- Weniger Details

- Verschmelze Ports mit Zellen

- Äquivalent zu Hypergraph

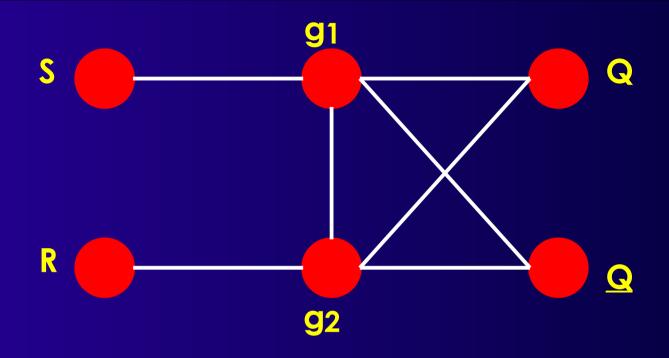

# Schaltungen als Graphen 3

- Cliquen-Modell

- Netze nicht mehr explizit modelliert

- Zellen an Netzen bilden jetzt Clique

# Schaltungsdarstellungen

- Zelle-Port-Netz Modell

- Tripartiter Graph

- Bipartiter Graph

- Clique-Modell

**Ungenauer**

- Für Problem passendes Modell wählen

- Mehr Daten nicht immer besser

- Konvertierungsroutinen bereitstellen

- Nur in ungenauere Darstellung möglich

- Buchführen über Herkunft von Daten

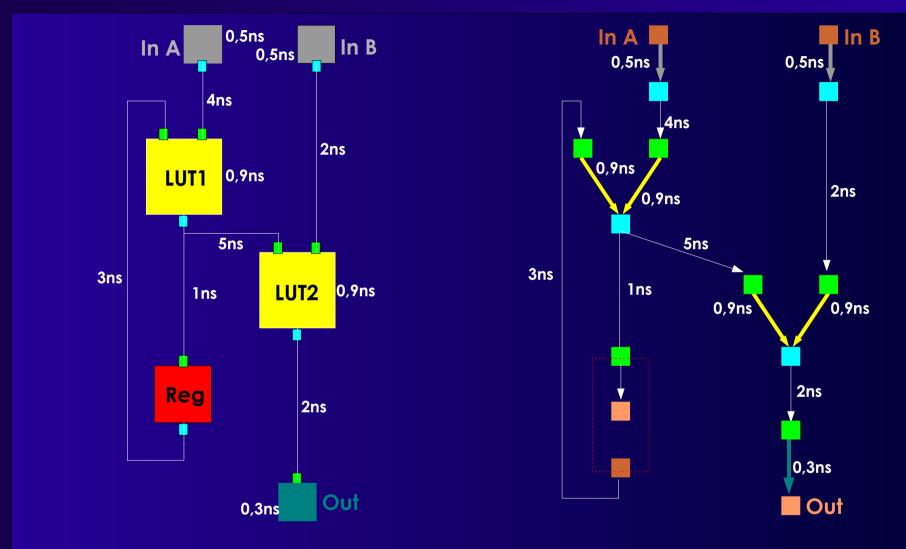

# Grundlagen Timing-Analyse

#### ■ Wozu?

- Analysiere fertige Layouts

- Analysiere einzelne Verbindungen während Layouterzeugung

- **◆ Erkenne kritische Verbindungen**

- Behandele diese mit Vorrang

#### Worauf?

- Schaltungselemente

- ◆ Gatter, Wertetabellen (LUT), Register, I/O-Blöcke, ...

- Bleiben konstant, exakte Verzögerungen bekannt

- Netze

- Nur nach Layouterzeugung bekannt, vorher schätzen

### Modellierung

- Auf "5-partitem" Graph

- Externe Ein-/Ausgänge, Ein-/Ausgangs-Ports

# Berechnung Ankunftszeit

Ankunftszeit (Arrival) an Knoten v:

$$T_a(v) = Max_{(u,v)\in E} (T_a(u) + w(u,v))$$

- Idee: BFS oder zyklenfreier LP

- Beginne mit  $T_a(v) = 0$  für Knoten v die sind:

- Externer Eingang, Registerausgang

- Bearbeite Knoten mit bearbeiteten Vorgängern

- Späteste Gesamtankunftszeit D<sub>max</sub> = Taktper.

- An externem Ausgang oder Registereingang

- Im Beispiel 13,6ns

# Spätestmögliche Ankunftszeit

- Wie unwichtig sind unkritische Netze?

- Idee: Verschiebbare Elemente bei Kompakt.

- Hier auf Zeitintervalle anwenden (slack)

- "Wieviel langsamer kann ein Netz werden, ohne dass die gesamte Schaltung leidet?"

#### Berechnung

- Mittels spätestmöglicher Ankunftszeit

- $\bullet$  Required time T(u) an Knoten u

- Spätestmöglicher Ankunftszeitpunkt von Signalen

- Sonst Verlangsamung der ganzen Schaltung

- Analog Kompaktierungsbeispiel

- Rechteste Position ohne Breitenvergrößerung

# Berechnung $T_r(u)$ & slack(u,v)

- Beginne mit  $T_r(u) = D_{max}$  für Knoten:

- Externer Ausgang, Registereingang

- Nun BFS/LP rückwärts

- Bearbeite Knoten

- Nur mit komplett bearbeiteten Vorgängern

- Rückwärts: Vorgänger hier sind sonst Nachfolger!

$$\mathbf{T}_r(u) = \underset{(u,v) \in E}{\mathbf{Min}} \left( \mathbf{T}_r(v) - w(u,v) \right)$$

■ Slack einer Verbindung von u nach v

$$\operatorname{slack}(u, v) = \operatorname{T}_r(v) - \operatorname{T}_a(u) - w(u, v)$$

Beachte: Auf kritischem Pfad slack = 0

### Beispiel s27.critical

```

Node: 4 INPAD SOURCE Block #2 (s27 in 3)

Tarr: 0 Treq: -3.88578e-16 Tdel: 5e-10

Node: 5 INPAD OPIN Block #2 (s27 in 3)

Pin: 0

T arr: 5e-10 T reg: 5e-10 Tdel: 5e-09

Net to next node: #2 (s27 in 3). Pins on net: 5.

Node: 12 CLB IPIN Block #6 (s27 out)

Pin: 0

T arr: 5.5e-09 T req: 5.5e-09 Tdel: 0

Node: 17 SUBBLK IPIN Block #6 (s27 out)

Pin: 0 Subblock #0

T arr: 5.5e-09 T reg: 5.5e-09 Tdel: 9e-10

Node: 21 SUBBLK OPIN Block #6 (s27 out)

Pin: 4 Subblock #0

T arr: 6.4e-09 T reg: 6.4e-09 Tdel: 0

Node: 16 CLB OPIN Block #6 (s27 out)

Pin: 4

T arr: 6.4e-09 T req: 6.4e-09 Tdel: 1e-09

Net to next node: #5 (s27 out). Pins on net: 2.

Node: 10 OUTPAD IPIN Block #5 (out:s27 out)

Pin: 0

T arr: 7.4e-09 T reg: 7.4e-09 Tdel: 3e-10

Node: 11 OUTPAD SINK Block #5 (out:s27 out)

T arr: 7.7e-09 T reg: 7.7e-09

Tnodes on crit. path: 8 Non-global nets on crit. path: 2.

Global nets on crit. path: 0.

Total logic delay: 1.7e-09 (s) Total net delay: 6e-09 (s)

```

# Weiteres Vorgehen

- Dienstag

- Kick-Off für praktische Arbeiten

- Vorher zu 3er Gruppen zusammenfinden

- Vorher den Leitfaden lesen

- ... um gezielt Fragen stellen zu können

- Nächste Vorlesung: Freitag

- Kleine Übungsaufgabe

- Berechne T<sub>a</sub>, T<sub>r</sub>, Slack

- ◆ Für das Beispiel auf Folie 46

- Allgemeine Vorbereitung

- Buch Kapitel 5.5 5.9

### Zusammenfassung

- Kompaktierung

- Berechnung der längsten Pfade

- Ohne und mit Zyklen

- Modellierung von Schaltungen

- Graphbasiert

- Hierarchisch

- Timing-Analyse

- Ankunftszeit

- Spätestmöglicher Ankunftszeit

- Slack