## Algorithmen im Chip-Entwurf 5

# Längenmaße und Platzierung: VPR

Andreas Koch FG Eingebettete Systeme und ihre Anwendungen TU Darmstadt

## Überblick

- Längenmaße

- Arten von Platzierungsproblemen

- Konkreter FPGA-Placer: VPR

- Zusammenfassung

# Verdrahtungsfläche

- Mögliches Platzierungs-Qualitätskriterium

- Gesamtfläche für Verdrahtung

- Nur bei ASIC

- ◆ Bei FPGA: Feste Breite der Leitungen, Länge reicht

- Aber: Vollständiges Routing zu komplex

- NP

- Abschätzen der Länge durch Metrik

- Einzeln pro Netz

- Aufsummieren der Teillängen

- Multiplizieren mit angenommener

- Leitungsbreite plus

- Leitungsabstand

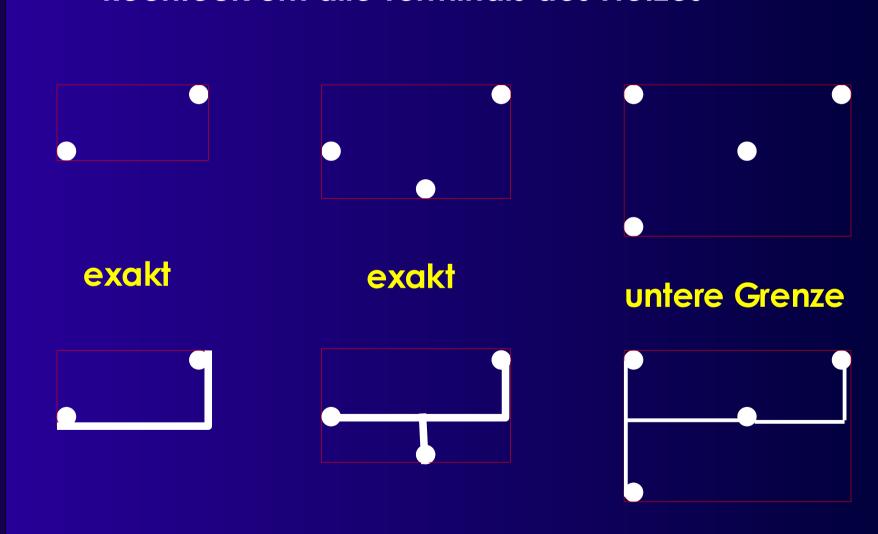

- Halber Umfang (half perimeter)

- Rechteck um alle Terminals des Netzes

Minimaler Rechtwinkliger Überspannender Baum (MRST)

- Sonderfall von MRST

- In P via Prim's Algorithmus (im Buch 3.4.4)

- Vollständiger planarer Graph

Rechtw. Steiner-minimaler Baum (RSMT)

$$L_{s} = 15$$

$L_{R}/L_{s} = 1.26$

- RSMT-Berechnung ist NP-vollständig

- Annäherung durch MRST: max. 1,5x so lang

- Bessere Näherungen existieren

- Quadratischer Euklidischer Abstand

- Arbeitet auf Zellen, nicht auf Netzen

- ◆ Für Clique-Modell geeignet

$$\frac{1}{2} \sum_{i=1}^{n} \sum_{j=1}^{n} \gamma_{ij} [(x_i - x_j)^2 + (y_i - y_j)^2]$$

- γij

- =0 wenn (v<sub>i</sub>, v<sub>j</sub>) ∉ E

- =|(vi,vj)|: Gewichtet nach Anzahl Kanten

- < |(vi,vj)|: nicht nur Einzelleitungen</p>

## Platzierungsprobleme

- Standardzellen

- Semi-Custom

- Building Block

- Teilweise Full-Custom möglich

- MPGA/FPGA

- Auf vorgegebene Strukturen

## Standardzellen 1

- Standardzellen (Semi-Custom)

- Kleinere Schaltungen (Gatter) aus Bibliothek

- Festes Layout

- **♦** Grösse

- Terminal-Anordnung

- Anreihbar in Zeilen

- Logistische Signale

## Standardzellen 2

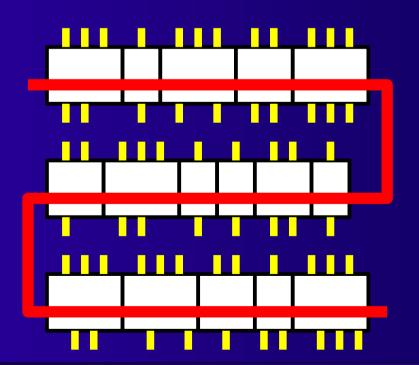

- Zeilenweise Anordnung

- Verdrahtung zwischen Zeilen

- Ausnahmen

- Angrenzende Verbindungen (abutment)

- Durchleitungen (feedthroughs)

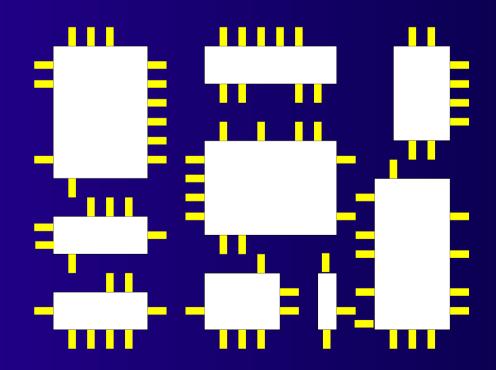

## **Building Blocks 1**

- Mehr Flexibilität

- Kann auch Full-Custom Teile enthalten

- Automatisch generierte Blöcke (z.B. RAM)

- Verdrahtungskanäle an allen Seiten

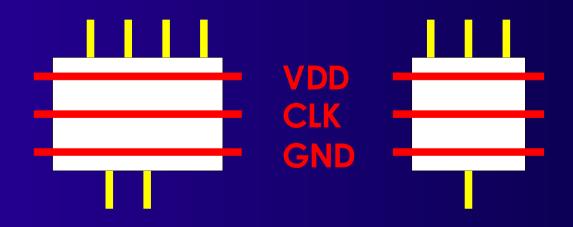

## MPGA/FPGA 1

- Mask-Programmable Gate Array

- Modebezeichnung: Structured ASIC

- Field-Programmable Gate Array

- Feste Anordnung von

- Logik

- Verdrahtung

- Anpassung auf Anwendung

- MPGA: Beim Hersteller (Metalllagen)

- FPGA: Beim Anwender (Programmierung)

## MPGA/FPGA 2

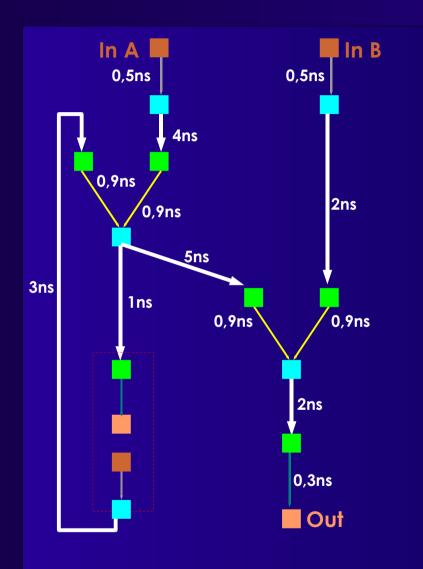

Switch Wire Länge 2 Box **Aktive Logik** Wire Länge 1

Längenmaße und VPR-Placer

## MPGA/FPGA 3

- Sehr ähnlich zu UPP

- Aber: Segmentierte Verbindungen

- Mehrere Verdrahtungslängen

- Verzögerung abhängig von

- Anzahl durchlaufener Switch Boxes

- Last (Fan-Out)

- Feste Verdrahtungskapazität

- Nicht jede Platzierung verdrahtbar

- Verdrahtbarkeit in Kostenfunktion

- Versatile Place and Route

- Betz und Marquardt, U Toronto

- Platzierer

- Simulated Annealing-basiert

- Adaptive Annealing Schedule

- Optimiert gleichzeitig

- ◆ Leitungslänge

- Verzögerung

- Paarweises Austauschen von Blöcken

- N<sub>blocks</sub> = Größe der Schaltung

- Aber nicht ganz wahllos

- Beschränkung der Entfernung

## Starttemperatur

- Wird automatisch bestimmt

- Für aktuelle Schaltung passend

- Idee:

- Anfangs fast alle Züge akzeptieren

- Wie hoch muss die Starttemperatur sein?

- Vorgehen

- N<sub>blocks</sub> paarweise austauschen

- Beobachte Änderung der Kostenfunktion x

- Standardabweichung

$$s_x = \sqrt{\frac{1}{n-1}} \left( \left( \sum_i x_i^2 \right) - n \, \bar{x}^2 \right)$$

- Starttemperatur =  $20 \cdot s_x$

- Beachte: Kostenfunktion ggf. normieren

- ◆ Bei VPR

# Thermal Equilibrium

Anzahl von Schritten pro Temperaturstufe:

$$10\,N_{blocks}^{\phantom{blocks}4/3}$$

■ 10x schneller, aber ca. 10% schlechter:

$$N_{\it blocks}^{\rm 4/3}$$

#### Beobachtung

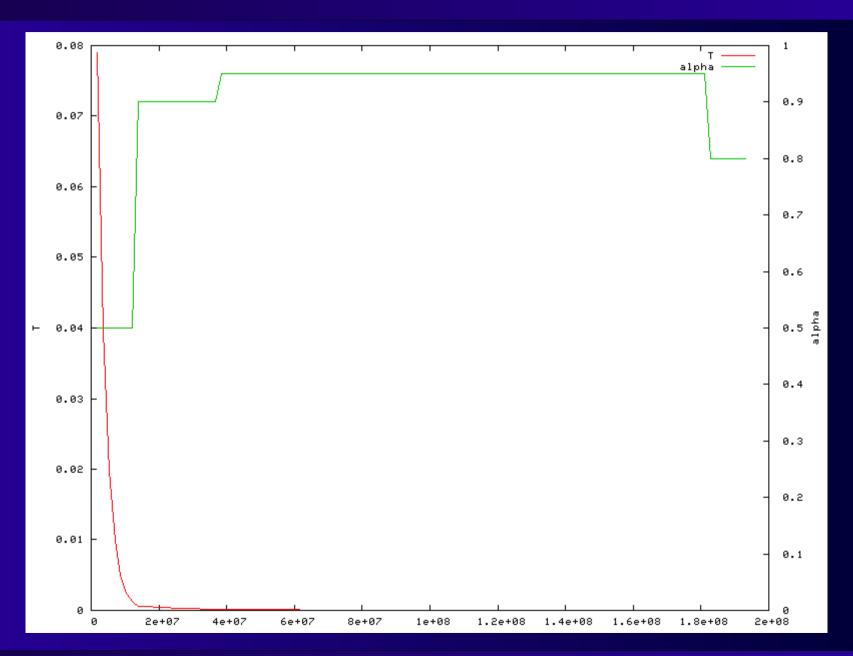

- Anfangs: T hoch, fast alle Züge akzeptiert

- ◆ Im wesentlichen zufälliges Bewegen

- ◆ Keine echte Verbesserung der Kostenfunktion

- Ende: T niedrig, kaum Züge akzeptiert

- Fast keine Bewegung mehr

- Wenig Veränderung in Kostenfunktion

#### Idee

- Meiste Optimierung passiert <u>dazwischen</u>

- Bringe T schnell in den produktiven Bereich

- Halte T lange im produktiven Bereich

- Vorgehen

- Steuere T anhand der Akzeptanzrate

$$T_{\text{new}} = \alpha T_{\text{old}}$$

| οι   | Acceptance Rate                 |

|------|---------------------------------|

| 0.50 | $R_{a} > 0.96$                  |

| 0.90 | $0.80 < R_{a} \le 0.96$         |

| 0.95 | $0.15 < R_{_{\rm cl}} \le 0.80$ |

| 0.80 | $R_{\alpha} \leq 0.15$          |

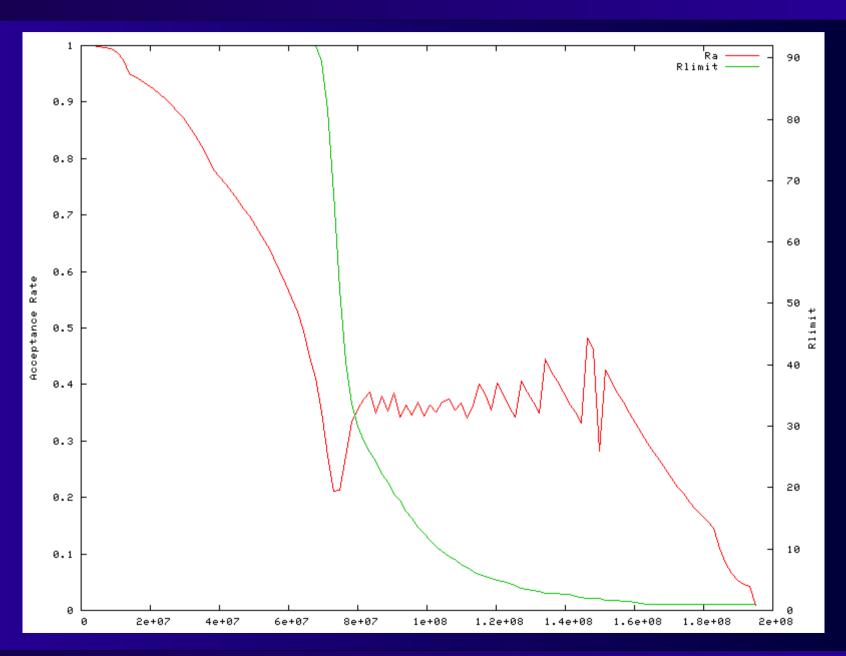

- Vorahnung

- Gute Fortschritte bei  $R_a \approx 0.5$

- Am effizientesten  $R_a = 0.44$

- Beste Fortschritte

- Idee

- R<sub>a</sub> möglichst auf diesem Wert halten

- Nicht temperaturbasiert (kühlt nur ab!)

- Sondern: <u>Auswirkungen</u> der Züge beeinflussen

- Beobachtung

- ♦ Weite Züge: Grosse Änderung der Kostenfunktion

- ♦ Kurze Züge: Kleine Änderung der Kostenfunktion

- Vorgehen

- Variiere Zugweite  $R_{\text{limit}}$  um  $R_{\text{a}} \approx 0.44$  zu halten

#### R<sub>limit</sub> klein

- Kleine Zugreichweite

- Kleine Änderungen der Kostenfunktion

- Kleine Verschlechterungen

- Werden eher angenommen

- $\bullet$   $R_a$  steigt

#### R<sub>limit</sub> gross

- Grosse Zugreichweite

- Grosse Änderungen der Kostenfunktion

- Große Verschlechterungen

- Werden eher abgelehnt

- R<sub>a</sub> sinkt

- Anfangs:  $R_{limit}$  = ganzer Chip  $L_{Chip}$

- Bei jedem Abkühlschritt:

$$R_{limit}^{new} = R_{limit}^{old} (1 + R_a^{old} - 0.44), 1 \le R_{limit}^{new} \le L_{Chip}$$

- Zuviel akzeptiert: R<sub>limit</sub> grösser machen

- Zuwenig akzeptiert: R<sub>limit</sub> kleiner machen

## Abbruchbedingung

- Wann Abkühlung beenden?

- Idee

- Erkennung von Stillstand

- Vorgehen

- Jeder Zug beeinflusst mindestens ein Netz

- Bestimme die durchschnittlichen Kosten pro Netz

- Wenn T kleiner als Bruchteil davon ...

- Nur noch kleine Chance, dass Zug akzeptiert wird

- ◆ T < 0.005 Cost/#Nets</p>

- ◆ Auch hier: Kostenfunktion ggf. normieren

- \* Bei VPR

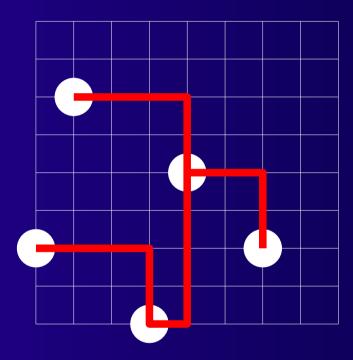

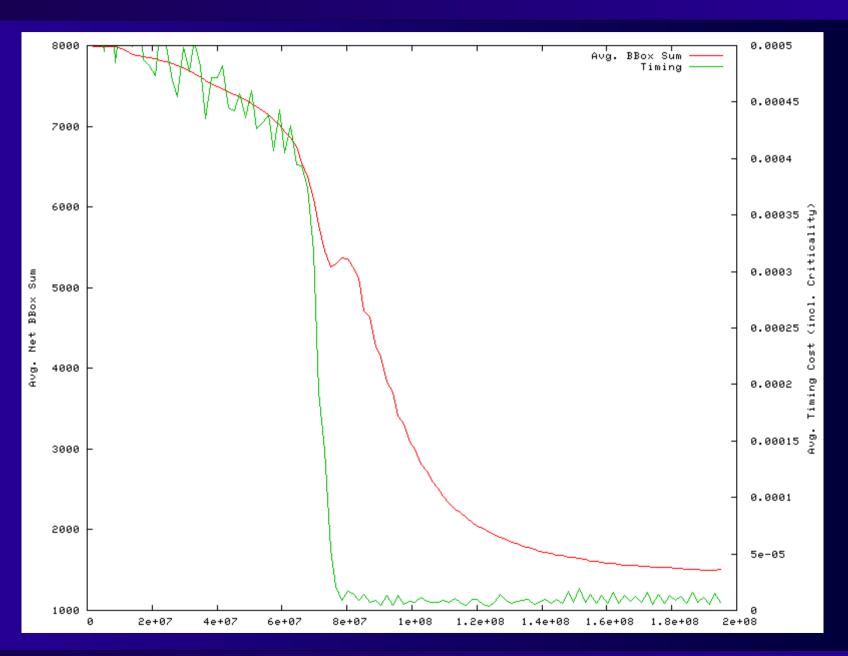

## Kostenfunktion

- Gleichzeitig optimieren

- Zeitverhalten

- Verdrahtungslänge

- Verdrahtungslänge

- Bestimmt als korrigierter halber Netzumfang

$$c_w = \sum_{n \in N} q(n_{pincount})[bb_x(n) + bb_y(n)]$$

$$q(i) = 1 \text{ für } i=1..3, =2.79 \text{ für } i=50$$

(Cheng 1994)

Web-Seite: Paper, Datei mit Korrekturfaktoren q(i)

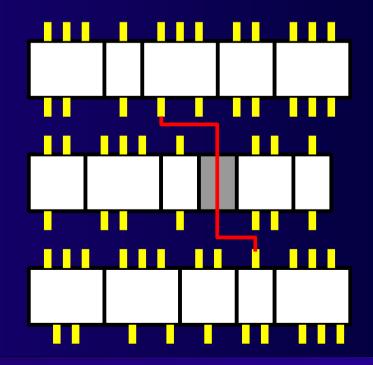

## Inkrementelle Berechnung 1

- Berechnung des Netzumfangs

- Simpel: O(k), k Anzahl der Pins

- Problem: k = 100 ... 1000 realistisch

- Nach jedem Zug neu berechnen

- Besser:

- Nach Möglichkeit nur bewegte Pins neu berechnen

- ◆ Ein Pin ist nur in einem Netz

- Ein Block hat aber mehrere Pins

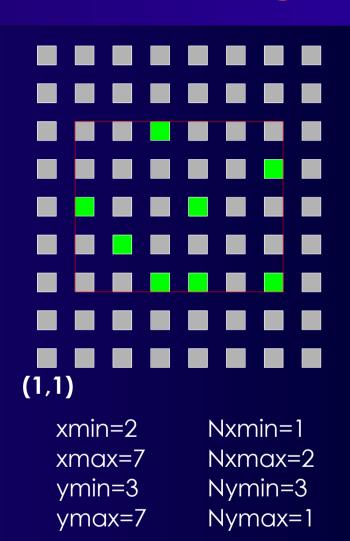

- Vorgehen

- Je Netz umspannendes Rechteck speichern

- ♦ (X<sub>min</sub>, X<sub>max</sub>, Y<sub>min</sub>, Y<sub>max</sub>)

- \* Position der Seiten

- ◆ (N<sub>xmin</sub>, N<sub>xmax</sub>, N<sub>ymin</sub>, N<sub>ymax</sub>)

- \* Anzahl Pins direkt auf den Seiten

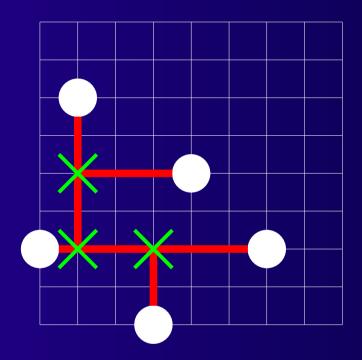

# Inkrementelle Berechnung 2

#### Betrachtet nur linke Seite (xmin)

- Bewege Terminal von xold nach xnew

- Netz an Terminal: n

```

If (xnew!=xold) { // horiz. bewegt

if (xnew < n.xmin) {

n.xmin = x_{new};

n.Nxmin = 1;

} else if (x_{new} == n.xmin) {

n.Nxmin++;

} else if (x_{old} == n.xmin) {

if (n.Nxmin > 1) {

n.Nxmin--;

} else {

BruteForce(n);

```

- Betrachte

- Platzierungs-abhängiges

Zeitverhalten

- Punkt-zu-Punkt Verbind.

- Von

- Netzquelle u

- Zu

- Jeder Netzsenke v

- Sicht: Two-Terminal-Nets

- ENetTiming

ETiming

- Zeitverhalten

- Bestimmt aus Slacks

- Nicht auf Pfaden (langsam)

- "Wichtigkeit" einer Verbindung

- Punkt-zu-Punkt zwischen Terminals u und v

Criticality

$$(u, v) = 1 - \frac{\operatorname{slack}(u, v)}{D_{max}}$$

- (u,v) auf kritischem Pfad

- ♦  $slack(u,v) = 0 \Leftrightarrow Criticality(u,v) = 1$

- (u,v) absolut unkritisch

- ♦  $slack(u,v) = D_{max} \Leftrightarrow Criticality(u,v) = 0$

- Timing Cost: Delay(u,v) ist Schätzung!

- Noch kein "echtes" Routing

$$c_t = \sum_{(u,v) \in E_{NetTiming}} Delay(u,v) Criticality(u,v)^{CriticalityExponent}$$

- Criticality Exponent

- Gewichtet kritischere Verbindungen h\u00f6her

- ♦ Wenige kritische Verbindungen dominieren c,

- Untergewichtet unkritischere Verbindungen

- ◆ Fallen fast ganz aus c, Berechnung heraus

- Idee

- Gegen Ende auf kritische Netze konzentrieren

- Vorgehen:

- Steigern von ce<sub>start</sub>=1 auf ce<sub>final</sub>=8 (experimentell)

CritExp =

$$1 - \frac{R_{limit}^{now} - 1}{R_{limit}^{start} - 1} \cdot (ce_{final} - ce_{start}) + ce_{start}$$

- slack() ist platzierungsabhängig

- Unkritische Netz können kritisch werden

- ♦ Zu lange Leitungslängen

- Kritische Netze können unkritisch werden

- Sehr kurze Leitungslängen

- Slack-Werte müssen <u>aktualisiert</u> werden

- Timing-Analyse: Ta, Tr

- Wie oft?

- Nach jedem Zug? Nach N Zügen?

- N-mal pro Temperaturstufe?

- Alle N Temperaturstufen?

- Bewährt:

- 1x pro Temperaturstufe

## Gesamtkostenfunktion

#### Selbstnormierend

- λ gewichtet Zeit ./. Längenoptimierung

- Aber  $\lambda=1$  erzeugt <u>nicht</u> die schnellste Lösung

- Netze wechselnd kritisch/unkritisch

- Nicht erkannt, da Timing-Analyse nur 1x pro Temp.

- Besser  $\lambda = 0.5$

- Längenmaß wirkt als Dämpfer für Oszillation

## Gesamtalgorithmus

```

S = RandomPlacement();

T = InitialTemperature();

Rlimit = InitialRlimit();

CritExp = ComputeNewExponent(Rlimit);

while (!ExitCriterion()) {

TimingAnalyze();

// Bestimme T_a, T_r und slack()

OldWiringCost = WiringCost(S); // für Normalisierung der Kostenterme

OldTimingCost = TimingCost(S);

while (InnerLoopCriterion()) {      // eine Temperaturstufe

Snew = GenerateSwap(S, Rlimit);

∆timingCost = TimingCost(Snew) - TimingCost(S);

\DeltawiringCost = WiringCost(Snew) - WiringCost(S);

\Delta C = \lambda \left(\Delta timingCost/OldTimingCost\right) + (1-\lambda) \left(\Delta wiringCost/OldWiringCost\right);

if (\Delta C = < 0)

S = Snew:

else

if (random(0,1) < exp(-\Delta C/T))

S = Snew

T = UpdateTemp();

Rlimit = UpdateRlimit();

CritExp = ComputeNewExponent(Rlimit);

```

## VPR Simulated Annealing 1

## VPR Simulated Annealing 2

# VPR Simulated Annealing 3

## Weiteres Vorgehen

#### Für 4SWS'ler

Donnerstag: Kolloquien

◆ Gruppe 1: Benz/Welti/Mahs 16:00-16:30 Uhr

◆ Gruppe 2: Rexroth/Look/Weber 16:30-17:00 Uhr

◆ Gruppe 3: Rendel/Längsfeld 17:00-17:30 Uhr

Gruppe 4: Guckes/Rohde/Podrazhansky 17:30-18:00 Uhr

Gruppe 5: Vogel/Pottharst/Juling

18:00-18:30 Uhr

- Freitag: Vorträge (je ca. 15 Minuten)

- ◆ In gleicher Reihenfolge

- Für alle

- Dienstag Vorlesung

## Zusammenfassung

- Längenmaße

- VPR

- Adaptives Simulated Annealing

- Selbstnormalisierende Kostenfunktion

- Schnelle Netzumfangsberechnung

- Gesamtalgorithmus

- Papers auf Web-Seite

- Cheng 1994: q(i) Korrekturfaktoren

- ... sonst eher schlecht zu lesen

- Marquardt & Betz: VPR

- ◆ 1997 Grundlagen

- 2000 Timing-gesteuerte Betriebsart (Criticality, etc.)