# Algorithmen für Chip-Entwurfswerkzeuge Platzierungsverfahren

Vorlesung WS 2018/2019

Florian Stock

Eingebette Systeme und Anwendungen Technische Universität Darmstadt

### Klausur

Klausurtermin: 27.02.19 von 10-12 Uhr in S101/A02

# Platzierungsproblem allgemein Design Stile

- Design Stile:

- Standardzellen

- Gate Arrays

- Makroblock

- Mixed-Size

- "UPP" Einfaches Beispielproblem

- Alle Gleich:

Platziere die zur Verfügung stehenden Module Überlappungsfrei!

Unterschiedlich in Zielfunktionen und Randbedingungen

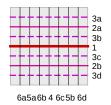

# Design Stil Standarzellen-Design

- Semi-Custom

- Bibliothek mit Logikmodule mit einfachen Funktionen (AND, OR, Inverter, ...)

- Alle Module haben die gleiche Höhe

- Module habe variable Breite

- Es gibt für das Platzieren vordefinierte Reihen

- Sehr beliebter Design-Ansatz

- ⇒ Viele Algorithmen gehen von Standardzellen Design aus

- Platzierung überlappungsfrei innerhalb der Reihen

# Design Stil Standarzellen-Design

### Routing:

▶ Infrastruktur (*V<sub>DD</sub>*, *CLK*, *GND*) durch alle Reihen

- Verdrahtung zwischen Reihen

- Ausnahmen:

Angrenzende Verbindungen (abutment)

Durchleitungen (feedthroughs)

## Design Stil Makroblock-Design

- Alle Module sind Makroblöcke (Building-Blocks) fester Größe, Form und Ausrichtung

- Kann auch Full-Custom Teile enthalten

- Automatisch generierte Blöcke (z.B. RAM)

- Verdrahtungskanäle an allen Seiten

- Alle sind überlappungsfrei zu platzieren

- Ähnlich zu Floorplanning (dort sind i.d.R. Form und Orientierung variabel).

### Design Stil Mixed-Size-Design

- Sehr häufig benutzt

- Vereint

- Makroblöcke und

- Standardzellen

- ► Makroblöcke ≫ Standardzellen

- $\Rightarrow$  Schwer Überlappungen zu vermeiden

### Zielarchitektur MPGA/FPGA

- Gate Arrays

- ► Field Programmable Gate Array (FPGA)

Wird beim Anwender an Funktion angepasst ⇒ Programmierung

- Mask Programmable Gate Array (MPGA)

Andere Bezeichnung: Structured ASIC

Wird beim Hersteller an Funktion angepasst ⇒ Metallagen Herstellung

- Reguläre Struktur mit fester Anordnung von

- Programmierbarer Logik

- Festen Funktionsblöcken

- Speicher

- Verdrahtung

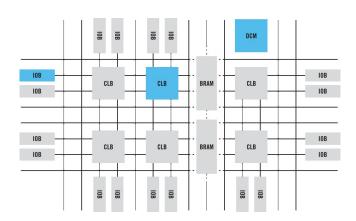

### Zielarchitektur MPGA/FPGA

[Quelle: Xilinx]

### Zielarchitektur MPGA/FPGA

- Sehr ähnlich zu UPP

- Aber: Segmentierte Verbindungen

- ⇒ Mehrere Verdrahtungslängen

- Verzögerung abhängig von

- Anzahl durchlaufener Switch Boxes

- Last (Fan-Out)

- Feste Verdrahtungskapazität

- ⇒ Nicht jede Platzierung verdrahtbar

- Verdrahtbarkeit in Kostenfunktion

### Platzierungsproblem

- Platzierungsproblem in nahezu allen Varianten NP-Vollständig

- Zur Lösung:

- Heuristische Algorithmen Simulated Annealing

- Analytische Algorithmen kräftebasiert, partionierungsbasiert, ...

# Simulated Annealing TimberWolf (1985)

- Standard Cell-Placer

- Start mit T = 4.000.000

- Stop bei T < 0.1

- Equilibrium abhängig von Problemgröße

- 100 Züge pro Zelle bei 200 Zellen

- 700 Züge pro Zelle bei 3000 Zellen

- Abkühlen

- Anfangs mit  $T_n = 0.8T$

- Im Mittelbereich mit  $T_n = 0.95T$

- Gegen Ende mit  $T_n = 0.8T$

- Cooling Schedule

- Versatile Place and Route

- Betz und Marquardt, University of Toronto

- Ab hier Auszüge aus Paper (auf Web-Seite)

- Platzierer

- Simulated Annealing-basiert

- Mit adaptivem cooling schedule

- Optimiert gleichzeitig

- Leitungslänge

- Verzögerung

### VPR Züge

- Paarweises Austauschen von Blöcken

- ► N<sub>blocks</sub> = Größe der Schaltung

- Aber nicht ganz zufällig: Beschränkung der Entfernung

## VPR Starttemperatur

- Wird automatisch bestimmt passend für aktuelle Schaltung

- Idee:

- Anfangs fast alle Züge akzeptieren

- Wie hoch muß die Starttemperatur sein?

- Vorgehen:

- N<sub>blocks</sub> Blöcke paarweise austauschen

- Beobachte Änderung der Kostenfunktion c (Standardabweichung)

$$s_c = \sqrt{\frac{1}{n-1}((\sum_i c_i^2) - n\bar{c}^2)}$$

Starttemperatur =  $20 \cdot s_c$

## Thermisches Gleichgewicht

Anzahl von Schritten pro Temperaturstufe:

$$10 \cdot N_{blocks}^{\frac{4}{3}}$$

10× schneller, aber nur ca. 10% schlechter:

$$N_{blocks}^{\frac{4}{3}}$$

- Beobachtung:

- Anfangs: T hoch, fast alle Züge akzeptiert

- Im wesentlichen zufälliges Bewegen

- Keine echte Verbesserung der Kosten

- Ende: T niedrig, kaum Züge akzeptiert

- Fast keine Bewegung mehr

- Wenig Veränderung in Kosten

- Idee:

Meiste Optimierung passiert zwischen Anfangs- und Endphase

- Bringe T schnell in den produktiven Bereich

- ► Halte *T* möglichst lange im produktiven Bereich

- Taile / moglicist larige im produktivem bereich

- Vorgehen: Steuere T anhand der Akzeptanzrate  $R_a$ Akzeptanzrate  $R_a$ : Anteil der Züge die akzeptiert wurde (egal, ob verbesserend oder verschlechternd)

▶ Cooling Schedule  $T_{new} = \alpha T_{old}$

| Acceptance Rate $R_a$ | $\alpha$ |

|-----------------------|----------|

| $R_a > 0.96$          | 0.50     |

| $0.80 < R_a \le 0.96$ | 0.90     |

| $0.15 < R_a \le 0.80$ | 0.95     |

| $R_a \leq 0.15$       | 0.80     |

- Vorahnung

- Gute Fortschritte bei  $R_a \approx 0.5$

- Am effizientesten R<sub>a</sub> = 0.44 Beste Fortschritte

- Idee

- R<sub>a</sub> möglichst auf diesem Wert halten, aber wie?

- Nicht temperaturbasiert (kühle nur ab!)

- Sondern: Auswirkungen der Züge beeinflussen

- Beobachtung:

- ► Weite Züge: Große Änderung der Kosten

- Kurze Züge: Kleine Änderung der Kosten

- Vorgehen:

- ▶ Variiere Zugweite  $R_{limit}$ , um  $R_a \approx 0.44$  zu halten

#### R<sub>limit</sub> klein

- Kleine Zugreichweite

- Kleine Änderungen der Kosten

- Kleine Verschlechterungen (Werden eher angenommen)

- ► R<sub>a</sub> steigt

### R<sub>limit</sub> groß

- Große Zugreichweite

- Große Änderungen der Kosten

- Große Verschlechterungen (Werden eher abgelehnt)

- ► R<sub>a</sub> sinkt

Anfangs:

$$R_{limit}$$

= ganzer Chip  $L_{Chip}$

Bei jedem Abkühlschritt:

$$R_{\mathit{limit}}^{\mathit{new}} = R_{\mathit{limit}}^{\mathit{old}} (1 + R_{\mathit{a}}^{\mathit{old}} - 0.44)$$

mit  $1 \leq R_{\mathit{limit}}^{\mathit{new}} \leq L_{\mathit{Chip}}$

- Zuviel akzeptiert: R<sub>limit</sub> größer machen

- Zuwenig akzeptiert: R<sub>limit</sub> kleiner machen

### VPR Abbruchbedingung

- Wann Abkühlung beenden?

- ▶ Idee:

- Stillstand erkennen

- Vorgehen:

- Jeder Zug beeinflußt mindestens ein Netz

- Bestimme die durchschnittlichen Kosten pro Netz

- Wenn T kleiner als ein Bruchteil davon . . .

- Nur noch kleine Chance, dass Zug akzeptiert wird

- ► T < 0.005 · AvgCostPerNet</p>

- Auch einfachere Realisierung möglich

- Letzte k Züge ohne akzeptierten Zug

- Letzte k Züge ohne Verbesserung von BSF

- **.**...

### Kostenfunktion

- Gleichzeitiges optimieren von

- 1. Verdrahtungslänge

- Zeitverhalten

- ⇒ Kombination von 2 Kostenfunktionen

- 1. Korrigierter HPWL:  $c_w = \sum_{n \in N} q(n_{pincount}) HPWL(n)$ Korrekturfaktor  $q_n$  um Unterschätzung vorzubeugen (q(1) = 1, ..., q(50) = 2.79, für Details siehe Paper auf Web-Seite [Cheng 1994])

- Zeitverhaltensabschätzung c<sub>t</sub>

# VPR Optimierung HPWL

- Berechnung HPWL

- ▶ Simpel:  $\mathcal{O}(k)$ , k Anzahl der Pins

- ▶ Problem: *k* = 100 ... 1000 realistisch

- Nach jedem Zug neu berechnen

- Besser:

- Nach Möglichkeit nur bewegte Pins neu berechnen

- Ein Pin ist nur in einem Netz

- Ein Block hat aber mehrere Pins

- Vorgehen:

- Je Netz umspannendes Rechteck speichern: Position der Seiten: (x<sub>min</sub>, x<sub>max</sub>, y<sub>min</sub>, y<sub>max</sub>,) Anzahl der Pins direkt auf den Seiten: (N<sub>xmin</sub>, N<sub>xmax</sub>, N<sub>ymin</sub>, N<sub>ymax</sub>,)

## VPR Optimierung HPWL

- ► Als Beispiel nur linke Seite

- **Bewege Terminal von**  $x_{old}$  nach  $x_{new}$

- Netz an Terminal: n

### if $x_{new} \neq x_{old}$ then

if

$$x_{new} < n.xmin$$

then

$$n.xmin := x_{new}$$

;

$$n.Nxmin := 1$$

else if

$$x_{new} = n.xmin$$

then

else if

$$x_{old} = n.xmin$$

then

if

$$(n.Nxmin > 1)$$

then

$$(x_{min}, x_{max}, y_{min}, y_{max},) = (2, 7, 3, 7)$$

$(N_{xmin}, N_{xmax}, N_{ymin}, N_{ymax},) = (1, 2, 3, 1)$

- Betrachte Platzierungsabhängiges Zeitverhalten

- Punkt-zu-Punkt Verbindungen

- Von Netzquelle u

- Zu jeder Netzsenke v

- ► Sicht: Two-Terminal-Nets

- Zeitverhalten:

- Bestimmt aus Slacks

- Nicht auf Pfaden (langsam)

- Wichtigkeit einer Verbindung

- Punkt-zu-Punkt zwischen Terminals u und v

$$Criticality(u, v) = 1 - \frac{slack(u, v)}{D_{max}}$$

- ► (u, v) auf kritischem Pfad:  $slack(u, v) = 0 \Leftrightarrow Criticality(u, v) = 1$

- ► (u, v) absolut unkritisch:  $slack(u, v) = D_{max} \Leftrightarrow Criticality(u, v) = 0$

- Timing Cost: Delay(u, v) ist Schätzung! Noch kein echtes Routing!

$$c_t = \sum_{(u,v) \in E_{NetTiming}} Delay(u,v) \cdot Criticality(u,v)^{ce}$$

- Criticality Exponent ce

- Gewichtet kritischere Verbindungen h\u00f6her

- Untergeweichtet unkritischere Verbindungen

- Idee:

- Gegen Ende auf kritische Netze konzentrieren

- Vorgehen:

- Steigern von ce<sub>start</sub> = 1 auf ce<sub>final</sub> = 8 (experimentell)

$$ce = \left(1 - \frac{R_{limit}^{now} - 1}{R_{limit}^{start} - 1}\right) \cdot (ce_{final} - ce_{start}) + ce_{start}$$

- slack() ist platzierungsabhängig

- Unkritische Netze k\u00f6nnen kritisch werden Zu lange Leitungsl\u00e4ngen

- Kritische Netze k\u00f6nnen unkritisch werden Sehr kurze Leitungsl\u00e4ngen

- Slack-Werte müssen (zeitaufwendig!) aktualisiert werden Timing-Analyse: T<sub>a</sub>, T<sub>r</sub>

- ▶ Wie oft?

- ▶ Nach jedem Zug? Nach N Zügen?

- N-mal pro Temperaturstufe?

- Alle N Temperaturstufen?

- 1× pro Temperaturstufe

### Gesamtkostenfunktion

Selbstnormierend:

$$\begin{split} & \Delta c_w = c_w(g) - c_w(f) \\ & \Delta c_t = c_t(g) - c_t(f) \\ & \Delta c = \lambda \frac{\Delta c_t}{c_t^{old}} + (1 - \lambda) \frac{\Delta c_w}{c_w^{old}} \end{split}$$

- $ightharpoonup \lambda$  gewichtet Zeit- gegenüber Längenoptimierung

- Aber  $\lambda$  = 1 erzeugt nicht die schnellste Lösung

- Netze wechselnd kritisch/unkritisch Nicht erkannt, da Timing-Analyse nur 1× pro Temperaturstufe

- Besser λ = 0.5

Längenmaß wirkt als Dämpfer für Oszillation

# Gesamtalgorithmus

```

S := RandomPlacement():

T := InitialTemperature();

Rlimit := InitialRlimit():

CritExp := ComputeNewExponent(Rlimit);

repeat

/* Bestimme Ta. Tr und slack()

/* eine Temperaturstufe:

TimingAnalyze();

Snew := GenerateSwap(S, Rlimit);

/* für Normalisierung der Kostenterme

\Delta timingCost := TimingCost(Snew) - TimingCost(S) :

\DeltawiringCost := WiringCost(Snew) - WiringCost(S);

OldWiringCost := WiringCost(S);

\Delta C := \lambda (\Delta timingCost/OldTimingCost) +

OldTimingCost := TimingCost(S) :

(1-\lambda)(\Delta wiringCost/OldWiringCost):

while !InnerLoopCriterion() do

if \Delta C < 0 then

S = Snew

else

/* eine Temperaturstufe

*/

if random(0,1) < exp(-\Delta C/T) then

S = Snew

T := UpdateTemp():

Rlimit := UpdateRlimit();

CritExp := ComputeNewExponent(Rlimit) :

until ExitCriterion():

```

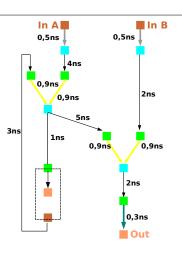

# VPR Temperatur- und $\alpha$ -Graph

Vorlesung | WS 2018/2019 | F. Stock | FG ESA, TU Darmstadt | 32 / 66

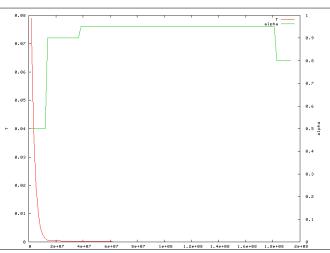

# VPR $R_a$ - und $R_{limit}$ -Graph

Vorlesung | WS 2018/2019 | F. Stock | FG ESA, TU Darmstadt | 33 / 66 ACE Organisatorisches Einführung Heuristische Verfahren - Sim

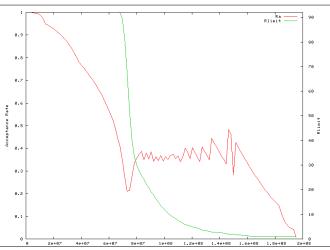

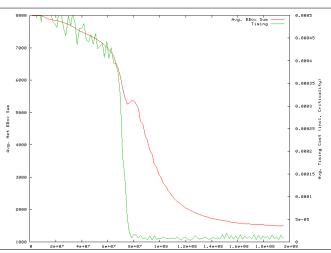

# VPR Kosten-Graphen

Vorlesung | WS 2018/2019 | F. Stock | FG ESA, TU Darmstadt | 34 / 66 ACE Organisatorisches Einführung Heuristische Verfahren - Sim

### DAST STUN

- Weitere SA Verbesserung

- Dynamisch Adaptives STUN ⇒ DAST (Lin & Warzynek 2010)

- Idee: Verbessertes entkommen lokaler Minima

- Stochastisches Tunneln ⇒ STUN (Hamacher 1999)

- Zusätzlich:

- Multimodale Bewegungen

- ► Lokale Minima Detektion ⇒ Nur dann STUN benutzen

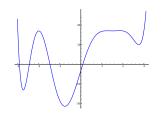

# STUN

# **Stochastic Tunneling**

- SA kann immer noch in lokalen Minima stecken bleiben (Freezing Problem)

- Idee: Tunneln durch (lokales) Maximum

- ► Kostenfunktion wird modifiziert:  $c'(x) = g(x) \circ c(x)$

- Große Werte werden geglättet

- Kleine werden hervorgehoben

- Klein und groß relativ zu der bisher besten Lösung mit Kosten c<sub>BSF</sub>

- Mehere Funktionen möglich ( $\gamma$  Tunnel Parameter der die Stärke des Glättens steuert):  $1-e^{-\gamma(c-c_{BSF})}$ ,  $\frac{1-sgn(c-c_{BSF})}{2}c$ ,  $\tanh(-\gamma(c-c_{BSF}))$ ,  $\sinh(-\gamma(c-c_{BSF}))$ , ...

- Empirisch festgestellt:

- Funktion beeinflußt Ergebnis bis zu 20%

- Für das Platzierungsproblem am besten: 1  $-e^{-\gamma(c-c_{BSF})}$

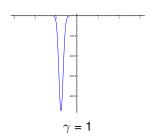

- $\gamma \in [0,\dots,5] \text{ beeinflußt Ergebnis bis zu 30\%} \\ \text{Wird manuell angepaßt}$

- Veränderung der Kostenfunktion

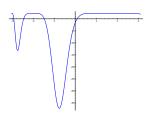

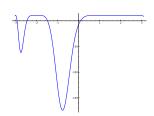

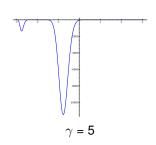

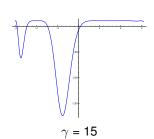

# STUN Glättungsfunktion

$$c_{STUN}(x) = 1 - e^{-\gamma(c(x) - c_{BSF})}$$

1-D Kostenfunktion

Kostenfunktion mit Glättung, BSF bei  $x_{BSF} = 2.76$

Kostenfunktion mit Glättung, BSF bei  $x_{RSF} = -2.73$

$$x_{BSF} = -2.73$$

# Glättungsfunktion Einfluß $\gamma$

In DAST: Adapativ, so dass  $\frac{c-c_{\mathit{BSF}}}{\gamma} \approx 0.05$

# DAST

# Multimodale Bewegungen

- Verallgemeinerung von VPRs R<sub>limit</sub>

- Es gibt verschiedene Arten von Zügen (z.B. Züge mit maximalen Reichweiten: <sup>2</sup>/<sub>3</sub>L, <sup>4</sup>/<sub>3</sub>L, 2L)

- Akzeptanzrate a<sub>i</sub> für jede Zugart m<sub>i</sub> mitprotokollieren

- Gibbs-Sampling (spez. Metropolis-Hastings-Algorithmus)

- Anfänglich werden Züge mit gleicher Wahrscheinlichkeit gewählt

- Später mit Wahrscheinlichkeit  $p(m_i) = \frac{a_i}{\sum_{i=0}^{n} a_i}$

Für Details: Siehe Paper

## DAST Lokale Minima Erkennung

- STUN besonders gut wenn in lokalem Minimum

- Permanentes stochastisches Tunneln negativ:

- Golfkurs-Effekt (Ebene mit einem Loch)

- Lokale Züge sind weniger effektiv

- ⇒ Versuche Minima zu erkennen und nur wenn nötig STUN zu benutzen

- DAST: Nutzt jede 10000. Iteration DFA (Detrended Fluctuation Analysis)

- Für Details: Siehe Paper

- Alternativen möglich: z.B. Ableitung

## DAST Zusammenfassung

- Stochastisches Tunneln

- Multimodale Züge

- Minima Erkennung

- Vergleich mit VPR5: Verbesserung von . . .

Laufzeit: ≈ 30%

Verzögerung: (kritischer Pfad)  $\approx$  12%

Verdrahtbarkeit: (min. Tracks) 3%

# SPA Structured Parallel Annealer

- Zug basiert immer auf (Nicht-)Akzeptanz des Vorhergenden

- ⇒ SA sehr sequentiell, schlecht parallelisierbar

- Verbessertes SA: SPA von Fobel, et al., 2014 FPL

- Nutzt Star+ Metrik

- Geschickte Wahl der Züge erlaubt Parallelisierung

- Angenommen 2 Züge parallel:

- Thread Blau

- Thread Rot

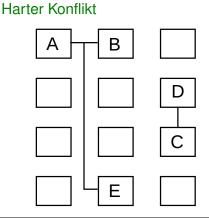

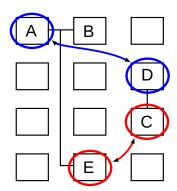

- Harter Konflikt:

- Beide wählen zufällig gleichen Block für Zug aus

- Kritisch, Folgezustand wäre fehlerhaft

- SPA vermeidet Harte Konflikte

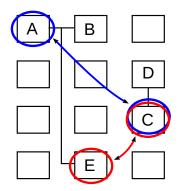

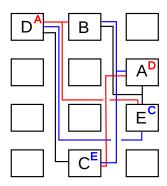

- Angenommen 2 Züge parallel:

- Thread Blau

- Thread Rot

- Harter Konflikt:

- Beide wählen zufällig gleichen Block für Zug aus

- Kritisch, Folgezustand wäre fehlerhaft

- SPA vermeidet Harte Konflikte

#### Harter Konflikt

- Angenommen 2 Züge parallel:

- Thread Blau

- Thread Rot

- Harter Konflikt:

- Beide wählen zufällig gleichen Block für Zug aus

- Kritisch, Folgezustand wäre fehlerhaft

- SPA vermeidet Harte Konflikte

#### Harter Konflikt

- Angenommen 2 Züge parallel:

- Thread Blau

- Thread Rot

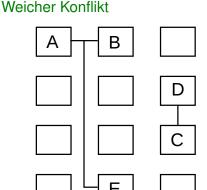

- Sanfter/Weicher Konflikt:

- Beide wählen zufälligen Block aus, der an gleichem Netz hängt

- Unkritisch, Nur geschätzte Kosten wären leicht fehlerhaft

- Zulassen von Weichen keine negativen Auswirkungen

- Angenommen 2 Züge parallel:

- Thread Blau

- Thread Rot

- Sanfter/Weicher Konflikt:

- Beide wählen zufälligen Block aus, der an gleichem Netz hängt

- Unkritisch, Nur geschätzte Kosten wären leicht fehlerhaft

- Zulassen von Weichen keine negativen Auswirkungen

- Angenommen 2 Züge parallel:

- Thread Blau

- Thread Rot

- Sanfter/Weicher Konflikt:

- Beide wählen zufälligen Block aus, der an gleichem Netz hängt

- Unkritisch, Nur geschätzte Kosten wären leicht fehlerhaft

- Zulassen von Weichen keine negativen Auswirkungen

- Angenommen 2 Züge parallel:

- Thread Blau

- Thread Rot

- Sanfter/Weicher Konflikt:

- Beide wählen zufälligen Block aus, der an gleichem Netz hängt

- Unkritisch, Nur geschätzte Kosten wären leicht fehlerhaft

- Zulassen von Weichen keine negativen Auswirkungen

- Angenommen 2 Züge parallel:

- Thread Blau

- Thread Rot

- Sanfter/Weicher Konflikt:

- Beide wählen zufälligen Block aus, der an gleichem Netz hängt

- Unkritisch, Nur geschätzte Kosten wären leicht fehlerhaft

- Zulassen von Weichen keine negativen Auswirkungen

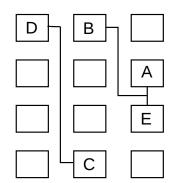

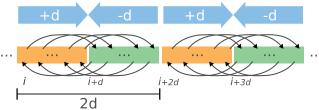

### **SPA**

## Konfliktvermeidung

- ► Idee:

- Alle Threads/Blöcke machen den gleichen Tausch

- Generierung von Mengen von Tauschpaaren,

- Zum Tausch über Distanz d:

[Quelle: Fobel et al.]

Garantiert, dass nie 2 verschiedene Blöcke auf die gleiche Position getauscht werden

#### **SPA**

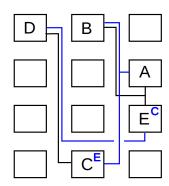

### Konfliktvermeidung 2-Dimensional

Verallgemeinerung auf 2-D:

Jeweils für jede Dimension und zusammenführen

[Quelle: Fobel et al.]

## SPA Algorithmus

- ightharpoonup Übernimmt alles von VPR (inkl. Temperatur, Coolding-Schedule und  $r_{lim}$ )

- Statt S<sub>t</sub> sequentiell auf einer Temperaturstufe

- $\Rightarrow$  parallele Züge bis  $S_t$  erreicht

- Ablauf einer parallelen Iteration:

- 1. Parallel: Kosten aller Kanten (Knoten-Netz-Paare)

- 2. Parallel: Züge bestimmen

- 3. Parallel: Delta-Kosten für alle Züge

(Nur von Tauschpartner mit größerem Index)

- 4. Parallel: (Nicht) aktzeptieren

- 5. Ergebnis verteilen

## SPA Ergebnisse

- Skaliert hervorragend

- Funktioniert mit einfachen Parallelprogrammierungs-Direktiven

- ⇒ Sehr einfach umzusetzen (GPGPU/SSE/...)

- Gute Lösungsqualität (5% besser als VPR (HPWL) im fast-Modus)

- Durchschnittlich 19× schneller als VPR (fast)

- Für mehr Details: Siehe Paper

### Zusammenfassung

- Allgemeines Platzierungsproblem

- Design-Stile & Zielarchitekturen

- Standardzellen

- Makro-/Buildingblock

- FPGA/MPGA

- Mixed-Mode

- VPR

- Adaptives Simulated Annealing

- Kostenfunktion (timingbasiert, selbstnormalisierend)

- Gesamtalgorithmus

- DAST

- STUN

- SPA

- Paralleles SA, durch geschickte Zug-Generierung

# Partionierungsbasierte Platzierer Idee

- Ansatz:

- 1. Verfügbarer Platz wird halbiert

- Schaltung wird partitioniert (mittels FM, KL, ...)

- 3. Halbe Schaltung wird auf jeweils die hälfte platziert

- Rekursiv bis auf das kleinste Element runter

- Anzahl Netze über die Schnittlinien wird minimiert, darum auch Min-Cut-Platzierung

- Problematisch: Partitionsübergreifende Verbindungen

- ⇒ Terminal propagation (Dunlop, 1995):

- Fixierte Dummy Terminals werden eingefügt

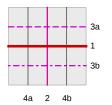

# Partionierungsbasierte Platzierer Rekursion

▶ Verschiedene Ansätze für die Rekursion möglich:

Quadratur-Platzierung (Quadrature placement)

Halbierungs-Platzierung (Bisection placement) Reihen-I Halbierungs-Platzierung (Slice/bisection placement)

arch Sair S. M. Wassesef H. VII S.I Diweinal Designs Author

## Partionierungsbasierte Platzierer Übersicht

- Sehr schnell

- ► Hierarchisch ⇒ sehr gut für große Schaltungen und parallelisierbar

- Unterhalb bestimmter Größen wird oft herkömmlicher Platzierer verwendet

- Optimierung immer nur bzgl. einer Schnittlinie

- Waren in 90ern nicht annähernd so gut wie SA oder analytische Platzierer

- Stark verbessert mit den Multilevel Partitionierern

2 Akademische Platzierer: Capo (Caldwell, 2000), Fengshui (Yildiz, 2001)

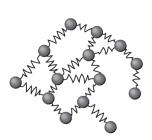

#### Kräftebasierte Placer

Zielkostenfunktion: Quadratische Verdrahtungslänge

Vorteil: Im Gegensatz zu HPWL stetig

differenzierbar

Nachteil: Lange Netze gegenüber kurzer

übergewichtet

Entspricht physikalisch einer Anordnung von Objekten die mittels Federn verbunden sind

Kräftebasierte (Force-Driven) Platzierung

- Optimum entspricht Kräftegleichgewicht (Überlappung erstmal ignoriert)

- ► Optimum finden durch lösen eines LGS

- $\Rightarrow$  sehr einfach  $\Rightarrow$  sehr beliebt

- Für zusätzliche Ziele zusätzliche Kräfte möglich

#### Kräftebasierte Placer

- Überlappungsfreiheit herstellen

- Erst ignorieren, hinterher legaliserien (z.B. Tetris Legalisierung)

- Zustäzliche Kräfte die für Verteilung wirken hinzufügen (Schwerpunkte oder andere explizite Kräfte)

Iterativ wiederholen bis keine Überlappung

- Implementierungen Kräftebasierter Platzierer:

- GORDIAN (Kleinhans, 1991)

- BonnPlace (Brenner, 2005)

- hATP (Nam, 2006)

# Analytische Placer StarPlace

- StarPlace(Xu, Grewal, Areibi 2010)

- Star+-Netzmodel

- Benutzt CG- oder SOR-(Successive Over-Relaxation)-Löser

- Zur Vermeidung von Triviallösungen:

ShrubPlace (vorplatziert alle I/O-Logik am Außenrand)

# StarPlace Star+ Performance

- In VPR: Star+ vs. HPWL

- Benutzt mit empirisch ermittelten Werten

$$\gamma = 1.59 \\

\phi = 1.0$$

Ergebnisse

Verdrahtbarkeit: Ähnlich gut Verdrahtungsressourcen: Ähnlich gut

(2.4% besser als VPR-fast)

Kritischer Pfad: 6% – 9%

Laufzeit: Kaum ein Unterschied

## StarPlace Algorithmus

```

APlace()

begin

Convert_Graph_Star+();

PrePlace();

repeat

CG_Iteration();

Legalize();

until Max Anzahl Iterationen;

```

- . Graph mittels Star+ konvertieren

- Vorplatzieren mit shrubPlace (I/O am Rand, Blöcke mit viel I/O nahe beieinander)

- 3. Konjugiertes Gradientenverfahren

- In jeder Iteration Lösung legalisieren (Partitionsbasierter Ansatz)

### StarPlace Zusammenfassung

- ▶ Benutzt zur Vorplatzierung shrubPlace ⇒

- 1.5% besseres Ergebnis bei Vedrahtungsressourcen gegenüber zufälliger Vorplatzierung

- Benötigt 5% der Laufzeit von StarPlace

- Benutzt CG-Löser

2% besserer kritischer Pfad, 4% mehr Verdrahtungsressourcen bei 56% längerer Laufzeit

- Besserer Löser: SOR (Successive Over-Relaxation)

(CG schwächelt bei nichtquadratischen Funktionen)

9% besserer kritischer Pfad bei 1% mehr Verdrahtungsressourcen bei 78% weniger Laufzeit

### Analytische Placer APlace

- Khang & Wang, 2005

- Zufällige Startplatzierung

- LSE-Zielkosten

- Zusätzliche Kosten/Kräfte zur Vermeidung von Überlappung

- Top-Down hierarchisches Vorgehen

- CG-Löser

### **APlace** Kostenfunktion

- LSE-Zielkosten

- Verteilung der Zellen (Reduzierung der Überlappung): Aufteilung der vorhandenen Fläche in Gitter a

$$\textit{DichteStrafe} := \sum_{\text{Gitterelemente } g} (\text{GesamtZellFläche}(g) - \text{DurchschnittZellenFläche})^2$$

- Ziel: Möglichst gleichmäßige Verteilung aller Zellen über gesamte Fläche

- Nicht differenzierbar, darum Potenialfunktion

$$Potenial(c, g) := K_c \cdot p(Zelle_x - Gitter_x) \cdot p(Zelle_y - Gitter_y)$$

$K_c$  Normierungsfaktor, so dass  $\sum_{a} Potenial(c, g) = A_c \text{ mit } A_c \text{ Fläche der Zelle } c$

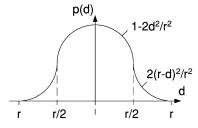

# APlace Glockenfunktion p

- Naylor et al., 2001

- Glockenfunktion

$$p(d) = \begin{cases} 1 - 2d^2/r^2 & 0 \le d \le r/2\\ 2(d - r)^2/r^2 & r/2 \le d \le r\\ 0 & \text{sonst} \end{cases}$$

ightharpoonup r ist der Einflußradius (empirisch r = 4)

[Quelle: Kahng]

### APlace Kostenfunktion

Differenzierbare Straffunktion:

$$\textit{DichteStrafe} \coloneqq \sum_{\text{Gitterelemente } g} \left( \left( \sum_{\text{Zellen c}} \textit{Potenial}(c,g) \right) - \textit{ExpPotenial}(g) \right)^2$$

Erwartetes Potenial von Gitterelement g:

$$ExpPotenial(g) := \frac{GesamtZellFläche}{AnzahlGitterelemente}$$

Kombination von Verdrahtungslänge und Dichte:

$Gewicht_{WL} \cdot c_{LSE} + Gewicht_{Dichte} \cdot DichteStrafe$

# APlace Zusammenfassung

- LSE-Kosten

- Dichtefunktion zur Überlappungsreduzierung

- Ergebnisse bis zu 10% besser als bei anderen Placern

- ▶ Laufzeit −5% bis +1300% höher

- Varianten:

- Auch andere Verdrahtungslängenfunktionen

- Timing-Driven

- Congestion-Driven

- Mixed-Size-Design

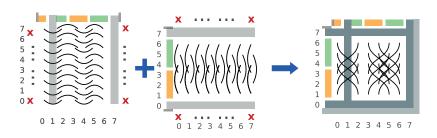

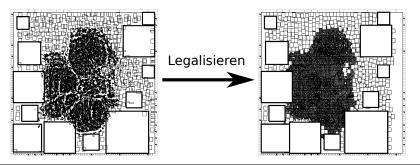

### Legalisierung

- Legalisierung von Platzierungen mit Überlappungen

- Weit verbreitet bei analytischen Platzierern

- Erst Problem ohne Nebenbedingungen optimieren

- Hinterher gefundene Lösung legalisieren

## Legalisierung Tetris-Algorithmus

- ▶ Hill, 2002 für Standardzellen, verwendet z.B. bei APlace

- Greedy-Algorithmus:

- Module in absteigender x-Koordinate sortieren (Breitere bei unentschieden) → Abarbeitungsreihenfolge

- Für jedes Modul: Mögliche Kandidatenposition, ist die am weitesten links liegende Position in jeder Reihe ⇒ die mit kleinstem Kosten (d.h. Abstand) wird Zielposition

- Sehr schnell

- Funktioniert auch gut bei Mixed-Size-Designs

- Varianten:

- lacktriangle Erleichterte vertikale Bewegung  $\Rightarrow$  Ausgeglichenere Reihen

- Diffusionsbasierter Ansatz

- ⇒ Ergebnis näher an Ausgangslösung

# Legalisierung Partionsbasierter Ansatz

- Verwendung u.a. bei StarPlace oder GORDIAN

- Rekursiv abwechselnded horizontal und vertikal unterteilen

- Solange bis nur noch eine Zelle in einer Partition Diese eine Zelle legalisieren

- Details später bei Partitionierer

### Zusammenfassung

- Analytische Placer

- Kräftebasiertes Platzieren

- StarPlace

- APlace

- Legalisierung