## **Compiler 2**

#### 8. Block: Registerallokation

# Organisatorisches

- Klausur

- Keine Hilfsmittel erlaubt

## Quellenangabe

Präsentation basiert auf Kapitel 13 von

Engineering a Compiler, 2<sup>nd</sup> Edition

Keith Cooper & Linda Torczon Morgan-Kaufman Publishers 2012

Folienpräsentation enthält Abbildungen und Beispiele aus Begleitmaterial zum Buch

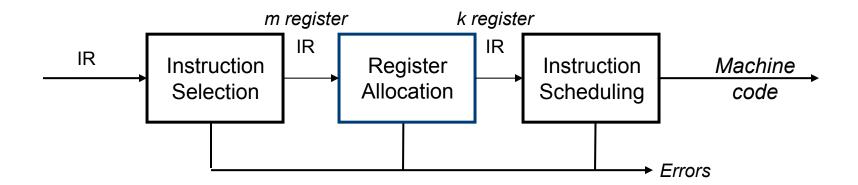

# **Einordnung in Compilefluß**

- Teil von Compiler-Back End

- Erzeugt korrekten Code der nicht mehr als k Maschinenregister benötigt

- Vermeide Loads/Stores bei Überbelegungen (spills) des Registerfeldes

- Minimiere Platz zur Auslagerung von Werten aus überbelegten Registern

- Laufzeiteffizienz ist wichtig: In der Praxis maximal O(n²), nicht O(2n)

- Muss potentiell alle n Instruktionen bearbeiten

## Beispiel

#### **EAC2e verwendet ILOC, ähnlich Bantam TAC**

- Virtuelle oder Pseudo-Register repräsentieren Werte

- Für jede Instruktion entscheiden

- Welche Pseudo-register vrX in echten Maschinenregistern rY halten?

- Einfach: | Werte| <= |Maschinenregister|</pre>

- Komplizierter: | Werte| > | Maschinenregister|

## **ILOC**

- Intermediate Language for Optimizing Compilers

- Beschrieben in Anhang A von EAC2e

- Semantik sehr ähnlich zu Bantam TAC

- Unbegrenzt viele Pseudo-Register

- Operanden: I-Immediate, A-Basisadressregister, O-Offsetregister

- Wenn nichts angegeben: Register

## Aufgaben der Registerallokation

- Wähle zu jedem Zeitpunkt die in Maschinenregistern gehaltenen Werte

- Erzeuge Instruktionen zum Transfer von Werten zwischen

- Registern

- Speicher

- Minimiere Aufwand für Transfer-Instruktionen

- Dynamisch Anzahl ausgeführter Instruktionen

- Statisch Anzahl abgespeicherter Instruktionen

- Bei lokalem Vorgehen (Basisblöcke): Dynamisch

Statisch

- Genauer

- Allokation (allocation): Welche Werte sollen in Registern gehalten werden?

- Zuweisung (assignment): In welchen Registern sollen Werte gehalten werden?

- Compiler muss beide Aufgaben erledigen!

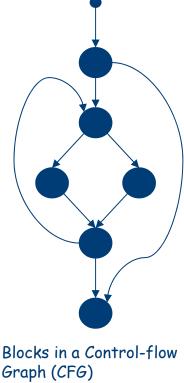

## **Lokale Registerallokation**

- Beschränkung auf einzelne Basisblöcke

- Liefert gute Ergebnisse innerhalb der Blöcke

- Wird aber ineffizient an Blockgrenzen

Graph (CFG)

## **Optimale Allokation ist hart**

#### Lokale Allokation

- In vereinfachten Fällen: O(n)

- Werte haben nur eine Größe

- Alle Werte müssen am Blockende in den Speicher geschrieben werden

- Alle Speicherzugriffe haben die selben Kosten

- Realistische Fälle: NP-vollständig

#### Lokale Zuweisung

- In vereinfachten Fällen: O(n)

- Werte haben nur eine Größe

- Keine Spills

- Realistische Fälle: NP-vollständig

- Globale Allokation: NP-vollständig für  $k \geq 1$  Register

- Globale Zuweisung: NP-vollständig

### Effekt der SSA-Form

- Registerallokation auf SSA-Form geht an sich schneller

- Polynomiale Zeit, mit niedrigem Grad des Polynoms

- Aber: Danach muss SSA-Form aufgelöst werden

- Phi-Funktionen in Kopien auflösen

- Benötigt wiederum Register

- ...

- Hier nicht diskutiert, erstmal grundsätzliches Vorgehen

## **ILOC** und Registerallokation

- Der Registerallokator braucht keine Kenntnisse über Bedeutung des Codes

- Lediglich DEFs und USEs sind relevant

- DEFs können einen überbelegenden Wert in den Speicher schreiben

- USEs können einen überbelegten Wert aus dem Speicher lesen

- DEFs und USEs leicht in ILOC-Instruktionen erkennbar

## **Beobachtung**

- Ein Wert lebt (is live) zwischen seinen DEFs und USEs

- Bestimme DEFs (x  $\leftarrow$  ...) und USEs (...  $\leftarrow$  ... x ...)

- Lebenszeit eines Wertes (live range)

Anfang: Letzte DEF

Ende: Letzte USE

- Darstellung innerhalb eines Basisblocks: Als Intervall [i,j]

- *i,j* sind die fortlaufenden Nummern der Instruktionen in BB

- Lebenszeiten sind schwerer zu bestimmen bei globalen Verfahren

## **MAXLIVE und sein Einfluß**

#### MAXLIVE

- Über alle Instruktionen i eines BBs ...

- ...die Anzahl von Lebenszeit-Intervallen, in denen *i* enthalten ist.

- Bedeutung: Anzahl der lebenden Werte (Pseudo-Register) zur Instruktion i

- Interpretation: Falls ...

- ... MAXLIVE ≤ k: Allokation einfach

- ... MAXLIVE  $\leq k$ : Keine Reserveregister zur Handhabung von Spills vorhalten

- ... MAXLIVE > k: einige Werte müssen im Speicher gehalten werden

- ... MAXLIVE > k: F Register reservieren, um Werte aus Speicher zurückzuholen

- Beispiel: MIPS braucht mindestens F=1 Register für Speicherzugriff

- Ausnahme bei MIPS?

## **Beispiel für MAXLIVE**

#### **Eingabecode**

```

loadI

1028 \Rightarrow vr1 // vr1 \leftarrow 1028

load

vr1 \Rightarrow vr2 // vr2 \leftarrow MEM(vr1), y

mult

vr1, vr2 \Rightarrow vr3 // vr3 \leftarrow 1028 \cdot y

load

\Rightarrow vr4 // vr4 \leftarrow x

Χ

vr4, vr2 \Rightarrow vr5 // vr5 \leftarrow x - y

sub

load

\Rightarrow vr6 // vr6 \leftarrow z

mult

vr5, vr6 \Rightarrow vr7 // vr7 \leftarrow z \cdot (x - y)

// vr5 \leftarrow z \cdot (x - y) - (1028 \cdot y)

sub

vr7, vr3 \Rightarrow vr8

// MEM(vr1) \leftarrow z \cdot (x - y) - (1028 \cdot y)

vr8

store

```

Store benutzt (USE) vr1, kein DEF! Enthält Zieladdresse

- Beispiel benutzt 1028 als

- Adresse von y

- Konstante in der Berechnung

- Hier verwendet, um längere Lebenszeit zu konstruieren

## Beispiel für MAXLIVE

#### Lebenszeiten

```

loadI

1028 \Rightarrow vr1 // vr1

load

vr1 \Rightarrow vr2 // vr1 vr2

vr1, vr2 \Rightarrow vr3 // vr1 vr2 vr3

mult

x \Rightarrow vr4 // vr1 vr2 vr3 vr4

load

vr4, vr2 \Rightarrow vr5 // vr1 vr3 vr5

sub

z \Rightarrow vr6 // vr1 vr3 vr6 vr5, vr6 \Rightarrow vr7 // vr1 vr3

load

mult

vr7

sub

vr7, vr3 \Rightarrow vr8 // vr1

vr8

vr8 \Rightarrow vr1 //

store

```

Ein Pseudo-Register lebt nach einer Operation falls es vorher einen Wert bekommen hat (DEF), der in Zukunft benutzt wird USE).

## **Beispiel für MAXLIVE**

#### **Bestimmung von MAXLIVE**

```

loadI

1028 \Rightarrow vr1

// vr1

MAXLIVE ist 4

load

vr1 \Rightarrow vr2 // vr1 vr2

mult

vr1.vr2 \Rightarrow vr3

// vr1 vr2 vr3

load

⇒ vr4 // vr1 vr2 vr3 vr4

Χ

// vr1

sub

vr4, vr2 \Rightarrow vr5

vr3

vr5

load

vr3

⇒ vr6

vr1

vr5 vr6

Ζ

mult

vr5, vr6 \Rightarrow vr7

// vr1

vr3

vr7

// vr1

vr7, vr3 \Rightarrow vr8

sub

vr8

\Rightarrow (vr1)

vr8

store

```

Wichtig: Bei store ist RHS ein USE, kein DEF Berechne Mengen lebender Variablen in Rückwärtsrichtung:

- 1. Beginn mit leerer Menge

- 2. In jeder Instruktion: entferne DEF, nehme Operanden aus USE (LHS) auf

## **Top-Down und Bottom-Up**

#### Vorgehensweisen bei der Registerallokation

#### Top-Down Allokator

- Basiert auf Angaben externer Funktion zur Bestimmung von "Wichtigkeit"

- Üblich: Am häufigsten benutzte Werte sind wichtig

- Weise dann Register an Werte in absteigender Wichtigkeit zu

- Halte Reserveregister zurück, um Speicherzugriffe ausführen zu können

- Ablegen/Wiederholen von überbelegten Werten

#### Bottom-Up Allokator

- Bestimme genaue DEF/USE-Struktur für jeden Eingabecode

- Baue dann konstruktiv Gesamtlösung aus Teillösungen zu jedem Schritt auf

- Behandelt alle Werte gleich (keine "Prioritäten" mehr)

# **TOP-DOWN ALLOKATOR**

## Grundlagen

#### Idee

- Halte am häufigsten benutzte Werte in Registern

- Reserviere F Register zum Ablegen/Wiederholen von Werte in/aus Speicher

#### Algorithmus

- Bestimme Priorität von Werten: Häufiger auftretende haben höhere

- Alloziiere die ersten k F Werte an Register

- Alle anderen verbleiben in Speicher und werden nur bei Bedarf geholt

- Schreibe Code um

- Einfügen von LOAD/STOREs für nur im Speicher abgelegte Werte

#### In den 70er/80er Jahren

- Manuelles Vorgehen: Schlüsselwort register in C

- Weise Compiler manuell an, diese Variable in Register zu halten

## **Anzahlen von Registern**

- Bestimme F: Wieviele reservierte Register werden benötigt?

- Register benötigt für

- Berechnung der Speicheradresse

- Speichern des geladenen Wertes

- Genaue Anzahl hängt von Zielarchitektur ab

- Bei MIPS: 0...1 Register für Speicheradresse

- Typische Instruktionen haben zwei Operanden, also Register für max. zwei Werte

- Falls Speicheroperationen nicht auf beliebigen Registern arbeiten können

- Reserviere diese Anzahl von Registern für Spilling

- Sonderfall: *k-F* < |Werte| < *k*

- Einfachste Vorgehensweise: Genau auf Sonderfall testen

## Beispiel für Top-Down Allokator

## TECHNISCHE DARMSTADT

#### **Ausgangssituation**

```

loadI

1028 \Rightarrow vr1 // vr1

load vr1 \Rightarrow vr2 // vr1 vr2

mult vr1, vr2 \Rightarrow vr3 // vr1 vr2 vr3

x \Rightarrow vr4 // vr1 vr2 vr3 vr4

load

vr4, vr2 \Rightarrow vr5 // vr1 vr3

sub

vr5

load

z \Rightarrow vr6 // vr1 vr3 vr5 vr6

mult vr5, vr6 \Rightarrow vr7 // vr1 vr3

vr7

sub vr7,vr3 \Rightarrow vr8 // vr1

store

vr8 \Rightarrow vr1 //

```

- Annahmen: k=5, F=2 (für zwei Operanden und ein Ergebnis)

- Hier kein separates Register für Speicheradresse erforderlich (ähnl. MIPS \$0)

- Beliebige Register als Quelle/Ziel in Speicheroperation

- Auftrittshäufigkeiten

- |vr1|=4, |vr2|=3, |vr3|=2, |vr4|=2, |vr5|=2, |vr6|=2, |vr7|=2, |vr8|=2

## Beispiel für Top-Down Allokator

# TECHNISCHE UNIVERSITÄT DARMSTADT

#### Allokation

```

loadI

1028 \Rightarrow vr1 //

vr1 \Rightarrow vr2 // vr1 vr2

load

spill vr3

vr1, vr2 \Rightarrow vr3 // vr1 vr2 vr3

mult

x \Rightarrow vr4 // vr1 vr2

load

vr3 vr4

sub

vr4, vr2 \Rightarrow vr5 //

vr1

vr5

load

⇒ vr6 //

vr5 vr6

vr1

mult

vr5, vr6 \Rightarrow vr7 //

vr1

vr7

vr7,vr3⇒ vr8 //

sub

vr1

restore vr3

vr8 \Rightarrow vr1

store

```

In Register

- Es dürfen maximal k-F=3 Werte in einer Instruktion am Leben sein

- Wenn mehr: Verschiebe Wert mit niedrigster Priorität in Speicher

- Auftreten: |vr1|=4, |vr2|=3, |vr3|=2, |vr4|=2, |vr5|=2, |vr6|=2, |vr7|=2, |vr8|=2

- Priorität: vr1 > vr2 > vr3 = vr4 = vr5 = vr6 = vr7 = vr8

# **Beispiel Top-Down Allokator**

#### Spill/Restore

```

loadI

1028 \Rightarrow vr1

vr1

Getrennte Lebenszeiten

vr1 vr2

load

vr1 \Rightarrow vr2

für vr3

mult vr1, vr2 \Rightarrow vr3 //

vr1 vr2 vr3

spill

\Rightarrow 16 //

vr1 vr2

vr3

load

vr1 vr2

⇒ vr4

vr4

Χ

sub

vr4, vr2 \Rightarrow vr5

vr1

vr5

load

vr5 vr6

⇒ vr6

vr1

Ζ

vr5, vr6 \Rightarrow vr7

mult

vr1

vr7

restore

16

⇒ vr3

vr1

vr3

vr7

vr7, vr3 \Rightarrow vr8

sub

vr1

vr8

store vr8 \Rightarrow vr1

```

In Register

- Spill/Restore Instruktionen hier nur beispielhaft, bei MIPS benutzbar:

- sw \$t3,0x10(\$0)

- lw \$t3,0x10(\$0)

- vr3 hat nun zwei getrennte Lebenszeiten!

## **Beispiel Top-Down Allokator**

#### Effekt der Aufteilung von Lebenszeiten

```

loadI

1028 \Rightarrow vr1

vr1

Getrennte Lebenszeiten

load

vr1 \Rightarrow vr2 // vr1 vr2

für vr3

mult vr1,vr2 \Rightarrow vr3 // vr1 vr2 vr3

⇒ 16 //

spill

vr3

vr1 vr2

load

vr1 vr2

x \Rightarrow vr4 //

vr4

sub vr4, vr2 \Rightarrow vr5 //

vr1

vr5

load

\Rightarrow vr6 //

vr5 vr6

vr1

Ζ

mult vr5, vr6 \Rightarrow vr7 //

vr1

vr7

⇒ vr3 //

vr3

restore 16

vr1

vr7

sub vr7, vr3 \Rightarrow vr8

vr1

vr8

store vr8 \Rightarrow vr1

```

In Register

- Kürzere Lebenszeiten für vr3 überlappen sich mit weniger Lebenszeitintervallen anderer Werte

- Mit jeder Entscheidung für Spill wird Allokationsproblem vereinfacht

- Siehe: iteratives Vorgehen

- Code ist nun legal: Maximal drei Pseudo-Register in Benutzung

- Braucht aber zwei weitere Instruktionen

# **Diskussion Top-Down Allocator**

- Funktioniert

- Problem: Häufigkeit des Auftretens ist naives Maß für Wichtigkeit

- Gegenbeispiel

- vr1 tritt extrem häufig am Anfang des BBs auf, danach nicht mehr

- Trotzdem wird Maschinenregister den ganzen BB über für vr1 reserviert

- Lösungsansatz mit Bottom-Up Allokator

# **BOTTOM-UP ALLOKATOR**

## Grundlagen

#### Idee

- Konzentriert sich auf das Ersetzen von Werten in Registern anstatt auf Allokation von Registern

- Halte Werte die "bald" wieder gebraucht werden in Registern

#### Algorithmus

- Beginne mit komplett unbelegten Registern

- Nimmt an, dass alle Werte im Speicher stehen

- Hole Werte nur bei Bedarf in Register

- Wenn kein Register verfügbar, gebe eines frei

#### Ersetzen von Werten bei Freigabe

- Gebe Register mit Wert frei, der am weitesten in der Zukunft gebraucht wird

- Bevorzuge unmodifizierte (*clean*) vor modifizierten (*dirty*) Werten

- Ähnliche Strategie wie bei Paging in virtuellem Speicher

## Beispiel für Bottom-Up Allokator

#### Gleicher Code wie vorher

```

Ab hier alle Register

loadI

1028 \Rightarrow vr1 // vr1

Belegt.

load vr1 \Rightarrow vr2 // vr1 vr2

mult vr1, vr2 \Rightarrow vr3 // vr1 vr2 vr3

load

x \Rightarrow vr4 // vr1 vr2 vr3 vr4

vr4, vr2 \Rightarrow vr5 // vr1 vr3

sub

vr5

load

\Rightarrow vr6 // vr1 vr3 vr5 vr6

mult vr5, vr6 \Rightarrow vr7 // vr1 vr3

sub vr7,vr3 \Rightarrow vr8 // vr1

vr8 \Rightarrow vr1 //

store

```

## Beispiel für Bottom-Up Allokator

Nun Spilling des Wertes mit entfernter Benutzung

```

1028 \Rightarrow vr1 // vr1

loadI

load vr1 \Rightarrow vr2 // vr1 vr2

spill vr1

mult vr1, vr2 \Rightarrow vr3 // vr1 vr2 vr3

x \Rightarrow vr4 // vr1 vr2 vr3 vr4

load

vr4, vr2 \Rightarrow vr5 // vr1 vr3

sub

vr5

load

z \Rightarrow vr6 // vr1 vr3

vr5 vr6

mult vr5, vr6 \Rightarrow vr7 // vr1 vr3

sub vr7,vr3 \Rightarrow vr8 // vr1

store

vr8 \Rightarrow vr1 //

restore vr1

```

## Beispiel für Bottom-Up Allokator

```

loadI

1028 \Rightarrow vr1 // vr1

load

vr1 \Rightarrow vr2 // vr1 vr2

mult vr1, vr2 \Rightarrow vr3 // vr1 vr2 vr3

vr1 \Rightarrow 20 // vr2 vr3

spill

load

\Rightarrow vr4 // vr2 vr3 vr4

Χ

vr4, vr2 \Rightarrow vr5 //

sub

vr3

vr5

⇒ vr6 //

vr5 vr6

load

vr3

mult

vr5, vr6 \Rightarrow vr7 //

vr3

vr7

sub

vr7, vr3 \Rightarrow vr8 //

vr8

restore 20 \Rightarrow vr1 // vr1

vr8

store

vr8 \Rightarrow vr1

```

- Zu jeder Instruktion maximal drei Werte am Leben

- vr1 hat nun zwei getrennte Lebenszeitintervalle

- Überlappen sich mit weniger anderen Lebenszeiten

- Vereinfachen Allokationsproblem

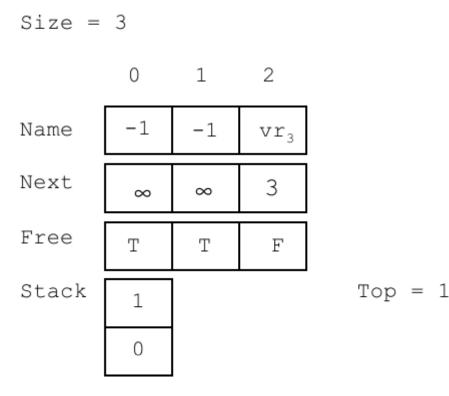

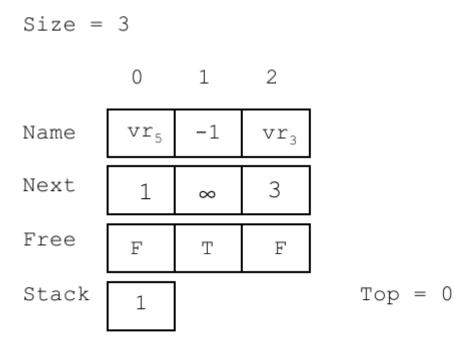

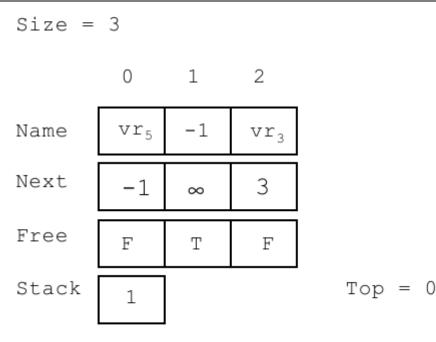

## **Datenstrukturen**

- Eine Klasse von Maschinenregistern

- Size: Anzahl von Registern in der Klasse

- Für jedes Register in der Klasse

- Namen des virtuellen Registers in diesem Maschinenregister

- Distanz bis zum nächsten USE des virtuellen Registers

- Marker, ob dieses Maschinenregister gerade verwendet wird

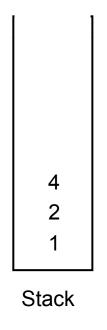

- Einen Stack verfügbarer Maschinenregister mit Stapelzeiger

```

initialize(class,size) {

class.Size \( - \) size-1 to 0 do

class.Name[i] \( - -1; \)

class.Next[i] \( - \)

class.Free[i] \( - \) true;

push(i,class);

class.StackTop = size-1;

}

```

Quelle der Erklärung und des Beispiels: Pedro Diniz, USC CSCI 565, S 2011

## **Funktionen 1**

- class(vr<sub>x</sub>) gibt Klasse von Maschinenregistern zurück, die vrx aufnehmen können

- ensure (vr, class) bestimmt schon vergebenes Register für vrx in der Klasse

- falls noch keines vergeben: vergebe ein neues und lade den Inhalt aus Speicher

- allocate(vr<sub>x</sub>, class) alloziert ein neues Register aus der Klasse

- gibt bevorzugt ein freies zurück

- falls alles belegt: das Register mit am weitesten in der Zukunft liegenden USE

- sichert vorher dessen Inhalt in den Speicher

## Funktionen 2

- free (vr, class) gibt ein benutztes Register der Klasse frei

- reinitialisiert seine Attribute

- legt es wieder auf den Stack freier Register der Klasse

- dist(vr<sub>x</sub>) Distanz zur Instruktion mit nächsten USE von vrx

## ensure (vr<sub>x</sub>, class)

```

req ensure(vr,class){

r ← find(vr,class); // Schon Maschinenregister alloziiert?

if (r exists) then

result \( \tau \);

else

result \( \text{allocate(vr,class);} \)

emit code to move vr into r; // hole Wert aus Speicher

end

return result;

```

## allocate (vr, class)

```

reg allocate(vr,class) {

if (class.StackTop ≥ 0) then // ein Maschinenregister frei?

r ← pop(class);

else

r ← findMaxNext(class); // r mit am weitesten entfernten USE

if (r is dirty) then

emit code to save r in memory at address for vr;

end

// vergebe Maschinenregister neu

class.Name[r] \( \nu \nu r; \)

class.Next[r] \leftarrow -1; // Temp. Marker: wird aktuell benutzt,

// nicht sofort wieder freigeben!

class.Free[r] \( \) false;

return r;

```

## free (vr<sub>x</sub>, class)

### Hauptfunktion

**Eingabe: Basisblock B**

Ausgabe: B mit umgeschriebenen Instruktionen

```

foreach instr i: "vr;3 \( \text{vr}_{i1} \) op vr;2" \( \text{B} \)

rx \( \infty \) ensure (vr; 1, class (vr; 1));

ry \( \text{ensure} \( \text{vr}_{i2}, \text{class} \( \text{vr}_{i2} \) );

if (vr; 1 is not needed after i) then

free (vr;1, class(vr;1));

if (vr; 2 is not needed after i) then

free (vr; 2, class (vr; 2));

rz \( \text{allocate} \( \text{vr}_{i3} \), \( \text{class} \( \text{vr}_{i3} \) );

rewrite i as "rz - rx op ry"

if (vr; 1 is needed after i) then

class.Next[rx] = dist(vr<sub>i1</sub>);

if (vr; is needed after i) then

class.Next[ry] = dist(vr;2);

class.Next[rz] = dist(vr; 3);

```

### **Diskussion Algorithmus 1**

- Berücksichtige erst Operanden vr<sub>i1</sub> und vr<sub>i2</sub>

- ... falls nicht mehr gebraucht, freigeben

- Kann möglicherweise gleiches Register verwenden: ...

vr<sub>b</sub> op vr<sub>b</sub>

- Anschließend Ergebnis vr<sub>i3</sub> behandeln

- Kann evtl. freigebene Operandenregister sofort wiederverwenden

- allocate setzt Next temporär auf -1, um sofortige Neubenutzung zu unterbinden

- Korrekter Wert wird erst später eingetragen

- dist(vrx) bei Wiederbenutzung

### **Diskussion Algorithmus 2**

#### Intuitive Vorgehensweise

- Nehme an, dass alle Maschinenregister frei sind

- Vergebe Maschinenregister, solange freie verfügbar sind

- Falls keine verfügbar, lagere Wert in Speicher aus

- Den am weitesten in der Zukunft liegenden

- Und verwende dessen Maschinenregister erneut

#### Rechtfertigung

- Führe so viele nützliche Instruktionen aus, wie möglich

- ... bevor ein Wert wieder geladen werden muss

```

\mathbf{vr}_3 \leftarrow \mathbf{vr}_1 \text{ op } \mathbf{vr}_2

\mathbf{vr}_5 \leftarrow \mathbf{vr}_4 \text{ op } \mathbf{vr}_1

\mathbf{vr}_6 \leftarrow \mathbf{vr}_5 \text{ op } \mathbf{vr}_6

\mathbf{vr}_7 \leftarrow \mathbf{vr}_3 \text{ op } \mathbf{vr}_2

```

$$\mathbf{vr}_3 \leftarrow \mathbf{vr}_1 \text{ op } \mathbf{vr}_2$$

$\mathbf{vr}_5 \leftarrow \mathbf{vr}_4 \text{ op } \mathbf{vr}_1$

$\mathbf{vr}_6 \leftarrow \mathbf{vr}_5 \text{ op } \mathbf{vr}_6$

$\mathbf{vr}_7 \leftarrow \mathbf{vr}_3 \text{ op } \mathbf{vr}_2$

Size = 3

$$\begin{array}{c|cccc}

0 & 1 & 2 \\

Name & -1 & -1 & -1 \\

Next & \infty & \infty & \infty \\

Free & T & T & T

\end{array}$$

Stack  $\begin{array}{c|ccccc}

2 & & & & & & & & & & \\

\hline

1 & & & & & & & & & & \\

\hline

0 & & & & & & & & & & \\

\hline

1 & & & & & & & & & & \\

\hline

0 & & & & & & & & & \\

\end{array}$

$$\mathbf{vr}_3 \leftarrow \mathbf{r}_0$$

op  $\mathbf{vr}_2$

$\mathbf{vr}_5 \leftarrow \mathbf{vr}_4$  op  $\mathbf{vr}_1$

$\mathbf{vr}_6 \leftarrow \mathbf{vr}_5$  op  $\mathbf{vr}_6$

$\mathbf{vr}_7 \leftarrow \mathbf{vr}_3$  op  $\mathbf{vr}_2$

Size = 3

$$0 \quad 1 \quad 2$$

Name

$$\begin{array}{c|cccc} vr_1 & -1 & -1 \\ \hline Next & 1 & \infty & \infty \\ \hline Free & F & T & T \\ \hline Stack & 2 & Top = 1 \\ \hline \end{array}$$

$$\mathbf{vr}_3 \leftarrow \mathbf{r}_0 \quad \text{op} \quad \mathbf{r}_1$$

$\mathbf{vr}_5 \leftarrow \mathbf{vr}_4 \quad \text{op} \quad \mathbf{vr}_1$

$\mathbf{vr}_6 \leftarrow \mathbf{vr}_5 \quad \text{op} \quad \mathbf{vr}_6$

$\mathbf{vr}_7 \leftarrow \mathbf{vr}_3 \quad \text{op} \quad \mathbf{vr}_2$

Size = 3

$$0 \quad 1 \quad 2$$

Name

$$vr_1 \quad vr_2 \quad -1$$

Next

$$1 \quad 3 \quad \infty$$

Free

$$F \quad F \quad T$$

Stack

$$2 \quad Top = 0$$

Size = 3

$$0 \quad 1 \quad 2$$

Name

$$vr_1 \quad vr_2 \quad vr_3$$

Next

$$1 \quad 3 \quad 3$$

Free

$$F \quad F$$

Stack

$$Top = -1$$

Name

$$vr_1$$

$vr_2$

Next  $1$   $3$

Free  $F$   $F$

Stack

Size = 3

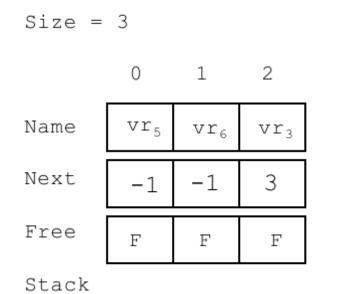

Problem: Kein Register frei für vr<sub>4</sub>, allocate sucht nach Wert mit am weitesten entferntem USF für Spill. Hier bspw. vr<sub>2</sub>

$$Top = -1$$

$vr_3$

F

$$\mathbf{r}_{2} \leftarrow \mathbf{r}_{0}$$

op  $\mathbf{r}_{1}$

$\mathbf{r}_{1} \rightarrow \mathbf{mem}$

$\mathbf{vr}_{5} \leftarrow \mathbf{r}_{1}$  op  $\mathbf{vr}_{1}$

$\mathbf{vr}_{6} \leftarrow \mathbf{vr}_{5}$  op  $\mathbf{vr}_{6}$

$\mathbf{vr}_{7} \leftarrow \mathbf{vr}_{3}$  op  $\mathbf{vr}_{2}$

Size = 3

$$0 \quad 1 \quad 2$$

Name

$$vr_1 \quad vr_4 \quad vr_3$$

Next

$$1 \quad -1 \quad 3$$

Free

$$F \quad F$$

Stack

Spill von vr<sub>2</sub> verwende r<sub>1</sub> wieder für vr<sub>4</sub>

Top = -1

$$\mathbf{r}_{2} \leftarrow \mathbf{r}_{0}$$

op  $\mathbf{r}_{1}$

$\mathbf{r}_{1} \rightarrow \mathbf{mem}$

$\mathbf{vr}_{5} \leftarrow \mathbf{r}_{1}$  op  $\mathbf{vr}_{1}$

$\mathbf{vr}_{6} \leftarrow \mathbf{vr}_{5}$  op  $\mathbf{vr}_{6}$

$\mathbf{vr}_{7} \leftarrow \mathbf{vr}_{3}$  op  $\mathbf{vr}_{2}$

vr<sub>4</sub> wird nicht mehr gebraucht, r<sub>1</sub> unmittelbar nach **ensure** freigeben

| Size = 3 |                 |    |                 |

|----------|-----------------|----|-----------------|

|          | 0               | 1  | 2               |

| Name     | vr <sub>1</sub> | -1 | vr <sub>3</sub> |

| Next     | 1               | ∞  | 3               |

| Free     | F               | Т  | F               |

| Stack    | 1               |    |                 |

Top = 0

$$\mathbf{r}_{2} \leftarrow \mathbf{r}_{0}$$

op  $\mathbf{r}_{1}$

$\mathbf{r}_{1} \rightarrow \mathbf{mem}$

$\mathbf{vr}_{5} \leftarrow \mathbf{r}_{1}$  op  $\mathbf{r}_{0}$

$\mathbf{vr}_{6} \leftarrow \mathbf{vr}_{5}$  op  $\mathbf{vr}_{6}$

$\mathbf{vr}_{7} \leftarrow \mathbf{vr}_{3}$  op  $\mathbf{vr}_{2}$

$$\mathbf{r}_{2} \leftarrow \mathbf{r}_{0}$$

op  $\mathbf{r}_{1}$

$\mathbf{r}_{1} \rightarrow \mathbf{mem}$

$\mathbf{r}_{0} \leftarrow \mathbf{r}_{1}$  op  $\mathbf{r}_{0}$

$\mathbf{vr}_{6} \leftarrow \mathbf{vr}_{5}$  op  $\mathbf{vr}_{6}$

$\mathbf{vr}_{7} \leftarrow \mathbf{vr}_{3}$  op  $\mathbf{vr}_{2}$

$$\mathbf{r}_{2} \leftarrow \mathbf{r}_{0}$$

op  $\mathbf{r}_{1}$

$\mathbf{r}_{1} \rightarrow \mathbf{mem}$

$\mathbf{r}_{0} \leftarrow \mathbf{r}_{1}$  op  $\mathbf{r}_{0}$

$\mathbf{vr}_{6} \leftarrow \mathbf{r}_{0}$  op  $\mathbf{vr}_{6}$

$\mathbf{vr}_{7} \leftarrow \mathbf{vr}_{3}$  op  $\mathbf{vr}_{2}$

$$\mathbf{r}_{2} \leftarrow \mathbf{r}_{0}$$

op  $\mathbf{r}_{1}$

$\mathbf{r}_{1} \rightarrow \mathbf{mem}$

$\mathbf{r}_{0} \leftarrow \mathbf{r}_{1}$  op  $\mathbf{r}_{0}$

$\mathbf{vr}_{6} \leftarrow \mathbf{r}_{0}$  op  $\mathbf{r}_{1}$

$\mathbf{vr}_{7} \leftarrow \mathbf{vr}_{3}$  op  $\mathbf{vr}_{2}$

Top = -1

$$\mathbf{r}_{2} \leftarrow \mathbf{r}_{0}$$

op  $\mathbf{r}_{1}$

$\mathbf{r}_{1} \rightarrow \mathbf{mem}$

$\mathbf{r}_{0} \leftarrow \mathbf{r}_{1}$  op  $\mathbf{r}_{0}$

$\mathbf{r}_{1} \leftarrow \mathbf{r}_{0}$  op  $\mathbf{r}_{1}$

$\mathbf{vr}_{7} \leftarrow \mathbf{vr}_{3}$  op  $\mathbf{vr}_{2}$

Size = 3

$$0 \quad 1 \quad 2$$

Name

$$vr_5 \quad vr_6 \quad vr_3$$

Next

$$-1 \quad -1 \quad 3$$

Free

$$F \quad F$$

Stack

$$Top = -1$$

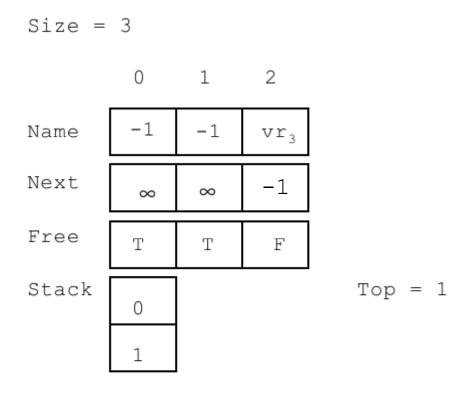

vr<sub>5</sub> vr<sub>6</sub> zurückschreiben (werden in BB nicht mehr gebraucht)

$$\mathbf{r}_{2} \leftarrow \mathbf{r}_{0} \quad \text{op } \mathbf{r}_{1}$$

$\mathbf{r}_{1} \rightarrow \mathbf{mem}$

$\mathbf{r}_{0} \leftarrow \mathbf{r}_{1} \quad \text{op } \mathbf{r}_{0}$

$\mathbf{r}_{1} \leftarrow \mathbf{r}_{0} \quad \text{op } \mathbf{r}_{1}$

$\mathbf{vr}_{7} \leftarrow \mathbf{r}_{2} \quad \text{op } \mathbf{vr}_{2}$

$$egin{array}{llll} \mathbf{r}_2 & \leftarrow & \mathbf{r}_0 & \mathrm{op} & \mathbf{r}_1 \\ \mathbf{r}_1 &

ightarrow & \mathrm{mem} \\ \mathbf{r}_0 & \leftarrow & \mathbf{r}_1 & \mathrm{op} & \mathbf{r}_0 \\ \mathbf{r}_1 & \leftarrow & \mathbf{r}_0 & \mathrm{op} & \mathbf{r}_1 \\ \mathbf{r}_1 & \leftarrow & \mathrm{mem} \\ \mathbf{vr}_7 & \leftarrow & \mathbf{r}_2 & \mathrm{op} & \mathbf{r}_1 \\ \end{array}$$

Size = 3

$$0 \quad 1 \quad 2$$

Name

$$-1 \quad vr_2 \quad vr_3$$

Next

$$\infty \quad -1 \quad -1$$

Free

$$T \quad F \quad F$$

Stack

$$0 \quad Top = 0$$

Vorher gespilltes vr<sub>2</sub> zurückholen

$$egin{array}{llll} \mathbf{r}_2 & \leftarrow & \mathbf{r}_0 & \mathbf{op} & \mathbf{r}_1 \\ \mathbf{r}_1 &

ightarrow & \mathbf{mem} \\ \mathbf{r}_0 & \leftarrow & \mathbf{r}_1 & \mathbf{op} & \mathbf{r}_0 \\ \mathbf{r}_1 & \leftarrow & \mathbf{r}_0 & \mathbf{op} & \mathbf{r}_1 \\ \mathbf{r}_1 & \leftarrow & \mathbf{mem} \\ \mathbf{r}_0 & \leftarrow & \mathbf{r}_2 & \mathbf{op} & \mathbf{r}_1 \end{array}$$

Size = 3

$$0 \quad 1 \quad 2$$

Name

$$vr_7 \quad vr_2 \quad vr_3$$

Next

$$-1 \quad -1 \quad -1$$

Free

$$F \quad F$$

Stack

Vorher gespilltes vr<sub>2</sub> zurückholen

Hier nicht diskutiert:

Laden der initialen Werte der Register aus Speicher Zurückschreiben der Ergebnisse in Speicher

Top = -1

### **Diskussion: Dirty / Clean**

- Schreiben von r1 in Speicher nicht nötig

- r1 wurde im Code nicht modifiziert

- Ist Clean

#### Idee

- Verwende bevorzugt Register wieder, die Clean sind

- Wert muss nicht zurückgeschrieben werden

#### Kann aber ineffizient sein

- Wenn ein Dirty-Wert sehr weit entfernt benutzt wird

- Rückschreiben in Speicher wäre besser, ...

- ... als Dirty Wert sehr lange im Register zu halten

```

\mathbf{r}_{2} \leftarrow \mathbf{r}_{0} \quad \text{op } \mathbf{r}_{1}

\mathbf{r}_{1} \rightarrow \text{mem} //\text{unn\"otig}

\mathbf{r}_{0} \leftarrow \mathbf{r}_{1} \quad \text{op } \mathbf{r}_{0}

\mathbf{r}_{1} \leftarrow \mathbf{r}_{0} \quad \text{op } \mathbf{r}_{1}

\mathbf{r}_{1} \leftarrow \text{mem}

\mathbf{r}_{0} \leftarrow \mathbf{r}_{2} \quad \text{op } \mathbf{r}_{1}

```

# Anforderungen an guten Allokator

- Lebenszeiten von Werten bestimmen

- Überlappungen (interference) zwischen Lebenszeiten erkennen

- Kosten eines Register-Spills bestimmen (Clean/Dirty)

- Entscheidung, welche Lebenszeiten von Werten in Registern gehalten werden (allocation)

- Lebenszeiten aufteilen (spilling, splitting)

- Zuweisung von Maschinenregistern an Werte (assignment)

- Code-Generierung

- Umschreiben auf Maschinenregister

- Code zur Handhabung von Spills einfügen

- (Code zum Rückschreiben von Ergebnissen einfügen)

### Zusammenfassung

- Lokale Methoden sind besser als nichts

- Ohne Registerallokator: Variablen nur im Speicher halten

- Z.B. in der Basis-Version von Bantam

- Müssen in der Praxis aber auch schon NP-harte Probleme lösen.

- Viele Vorgehensweisen möglich

- Bottom-Up besser als Top-Down

- Bottom-Up berücksichtigt tatsächliche Programmstruktur

- Top-Down verlässt sich auf die aggregierten Wichtigkeitsdaten

# GLOBALE REGISTERALLOKATION

### Übersicht

- Gängige Vorgehensweise für globale Registerallokation

- Baue Konflikt- oder Interferenzgraph für CFG auf

- Löse dann Graphenfärbungsproblem mit *k* Farben

- Falls nicht möglich: Transformiere Code, so dass k-Einfärbung möglich ist

- Jede Farbe entspricht dann einem Maschinenregister

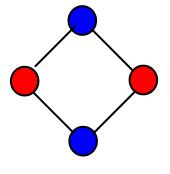

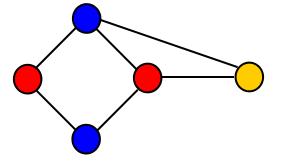

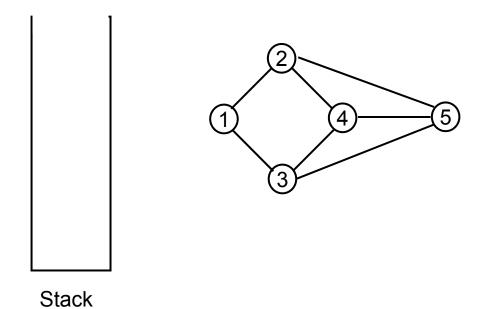

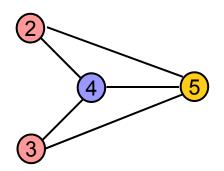

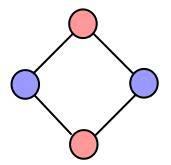

# Exkurs: Graphenfärbungsproblem

- Keine durch eine Kante verbundenen Knoten haben dieselbe Farbe

- Für Einfärbung des kompletten Graphen werden maximal k Farben benötigt

2-einfärbbar

3-einfärbbar

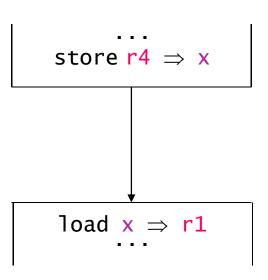

# Schwierigkeiten 1

- Triviales Vorgehen

- Alle Werte im Speicher zu Blockanfang

- Dann lokale Registerallokation

- Alle Werte zum Blockende in Speicher schreiben

- Ineffizient: Im Beispiel

- Load durch Move ersetzbar

- Idealerweise ganz weglassen

- Stattdessen gleiches Register verwenden

- Sinnvolle Registerzuweisung über Blockgrenzen hinweg

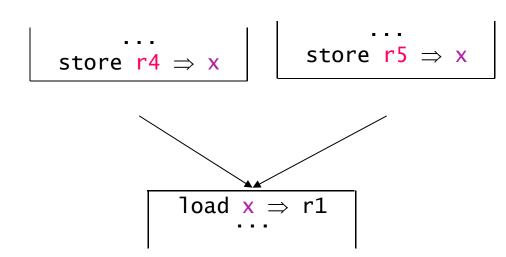

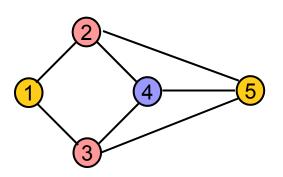

# Schwierigkeiten 2

- Komplexer: Mehrere Vorgänger im CFG

- Registerzuweisung muß nun über drei Blöcke abgestimmt werden

- Spezialität: Schleife

- Block ist sein eigener Vorgänger

- Macht Erweitern der lokalen Verfahren extrem kompliziert

- ... und potentiell langsam

### Vorgehensweise

- Grenzen zwischen Intra-Block und Inter-Block Bearbeitung aufgeben

- Alles mit globalem Verfahren rechnen

- Registerallokation auf Basis von Graphenfärbung

- 1 Baue Interferenzgraph G<sub>1</sub> für Prozedur auf

- Lebenszeiten sind schwerer zu bestimmen

- G<sub>I</sub> ist kein Intervallgraph

- 2 Berechne Einfärbung mit maximal k Farben

- Minimale Einfärbung von allgemeinen Graphen ist NP-Vollständig

- Heuristik benutzen

- Platzierung von Spills nun sehr kritisch (Schleifen!)

- 3 Ordne Farben an Maschinenregister zu

# Interferenzgraphen 1

#### Interferenz

- Zwei Werte x und y interferieren, falls eine Operation existiert, während der beide Live sind

- Falls x und y interferieren, können sie nicht im gleichen Register abgelegt sein

- Offensichtlich erforderlich: Bestimmung der Liveness von Werten

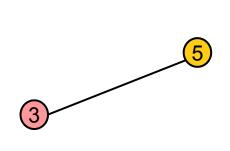

- Interferenzgraph  $G_{I} = (N_{I}, E_{I})$

- Knoten in N<sub>1</sub> repräsentieren Lebenszeiten von Werten

- Kanten in E<sub>T</sub> repräsentieren einzelne Interferenzen

- Für x,  $y \in N_T$ :  $(x,y) \in E_T$  genau dann, wenn x und y interferieren

- k-Einfärbung von  $G_{\tau}$  kann betrachtet werden als Allokation auf kRegister

### **Interferenzgraphen 2**

- Lebenszeiten bestimmen

- Auf SSA-Form der Prozedur

- Nun Low-Level IR bzw. Maschineninstruktionen mit virtuellen Registern

- Bilde Vereinigungsmenge der Lebenszeiten der Argumente an Phi-Funktionen

- Arbeite nun auf Lebenszeiten, nicht mehr auf virtuellen Registern

- Berechne LIVE-Mengen über Lebenszeiten

- Mit iterativem Datenflusslöser

- Übliche Gleichungen wie bei Live-Variablen, nun mit Lebenszeiten

- Iteriere über jeden Block, rückwärts über dessen Operationen

- Konstruiere LIVENOW-Menge (nun per Operation), beginnend mit LIVEOUT(B)

- Füge entsprechende Kanten in Graph hinzu

- Vom Ergebnis der Operation zu allen Lebenszeiten in LIVENOW

- Entferne Ergebnis aus LIVENOW

- Füge Operanden zu LIVENOW hinzu

- Eine Lebenszeit *L* in einem CFG enthält DEFs und USEs von Werten

- Für jeden USE *u* in *L* müssen alle DEFs, die *u* erreichen auch in *L* enthalten sein

- Für jeden DEF d in L müssen alle USEs enthalten sein, die von d erreicht werden

- Komplizierter als im lokalen Falle

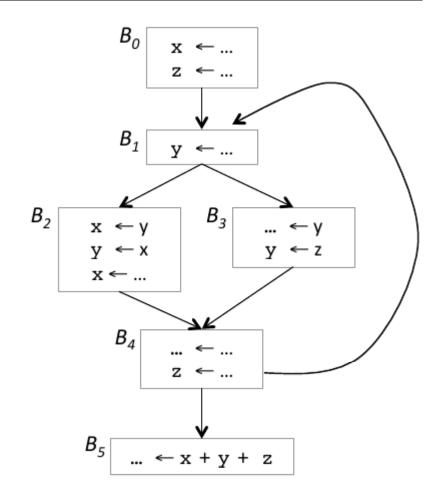

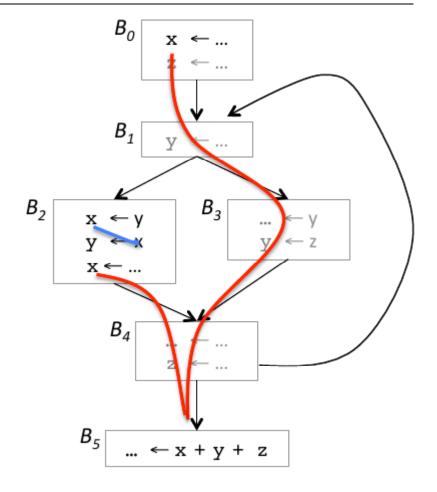

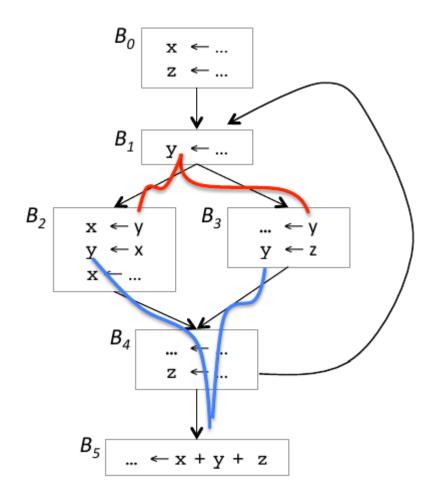

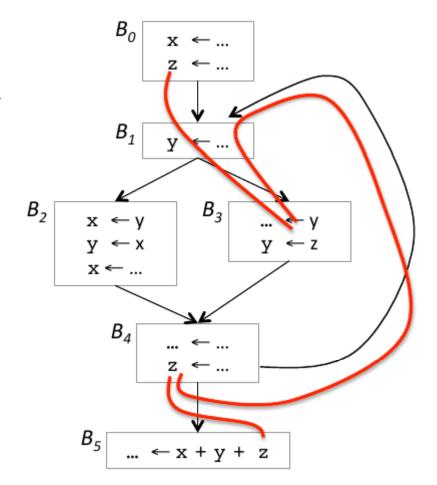

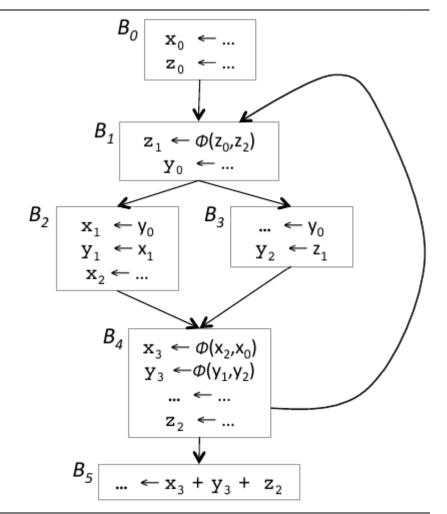

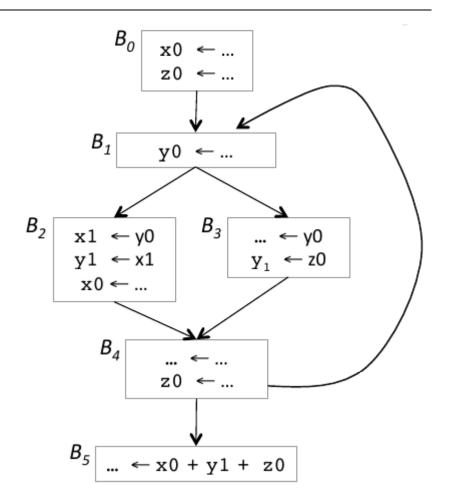

- Beispiel: Lebenszeiten von x, y und z

- Komplizierter als im lokalen Falle

- Beispiel: Lebenszeiten von x, y und z

- *x* hat zwei getrennte Lebenszeiten

- Komplizierter als im lokalen Fall

- Beispiel: Lebenszeiten von x, y und z

- x hat zwei getrennte Lebenszeiten

- y hat zwei getrennte Lebenszeiten

- Komplizierter als im lokalen Fall

- Beispiel: Lebenszeiten von x, y und z

- x hat zwei getrennte Lebenszeiten

- y hat zwei getrennte Lebenszeiten

- z hat nur eine Lebenszeit

- z lebt niemals in B<sub>2</sub>

- Bestimmung kann mühsam werden

### **Lebenszeiten in SSA-Form 1**

- Deutlich einfacher in SSA-Form

- Jeder Wert hat genau eine Definition

- An Phi-Funktionen fliessen Werte zusammen

- Algorithmus

- Wandele CFG ggf. in SSA-Form um (nur für Lebenszeitbestimmung!)

- Betrachte zunächst jeden einzelnen SSA-Namen als einzelne Lebenszeit

- Bei Phi-Funktion: Vereinige Lebenszeiten

- der Parameter

- des Ergebnisses

- Verbliebene Mengen sind die Lebenszeiten der Werte

- Benenne nun Werte im SSA-Graphen in Lebenszeiten um

- Jede Lebenszeit entspricht einem virtuellen Register

### Lebenszeiten in SSA-Form 2

- 2. ... {z0,z1,z2} ...

- 3. ... {x0,x2,x3} ...

- 4. ... {y1,y2,y3} ...

#### Ergebnis:

**Hinweis**: Kopieroperation x := y legt x und y nicht in dieselbe Lebenszeit!

### Lebenszeiten in SSA-Form 3

- Nun wieder ursprünglichen Nicht-SSA CFG verwenden

- Benenne alle Wertnamen in Lebenszeiten um

- Vorschlag hier: Ein Element der Menge von SSA-Wertinstanzen

- $\{ x0, x2, x3 \}$

- {x1}

- {y0}

- {y1,y2,y3}

- {**z**0,z1,z2}

### LIVE über Lebenszeiten

- Berechne nun LIVE-Mengen

- Genau wie mit Variablen

LIVEOUT(b) =

$$\bigcup_{s \in Succ(b)}$$

LIVEIN(s)

LIVEIN(b) = UEVAR(b)  $\cup$  (LIVEOUT(b)  $\cap$  VARKILL(b))

LIVEOUT( $n_{final}$ ) =  $\emptyset$

Variablen repräsentieren nun aber Lebenszeiten von Werten

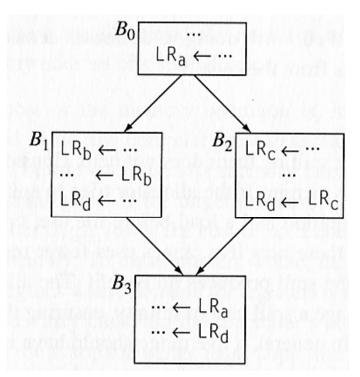

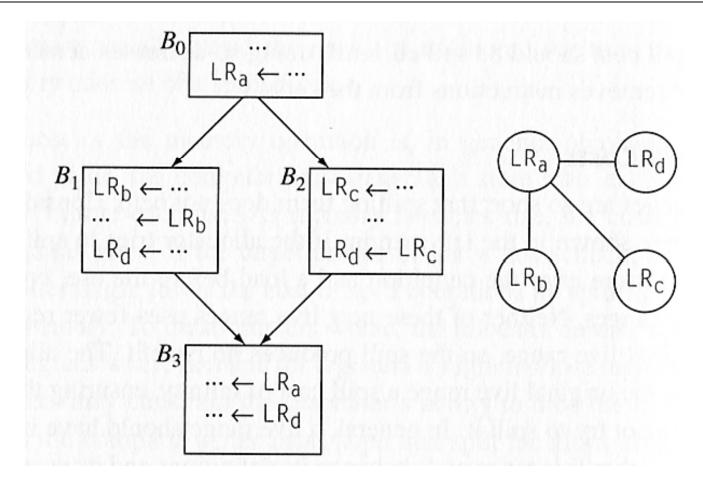

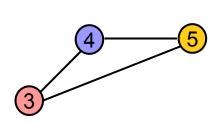

### Aufbau des Interferenzgraphen 1

```

for each LR_i create a node n_i \in N

for each basic block b

LiveNow \leftarrow LiveOut(b)

for each operation op_n, op_{n-1}, op_{n-2}, ... op_1 in b

with form op_i LR_a, LR_b \Rightarrow LR_c

for each LR_i \in \text{LiveNow}

add (LR_c, LR_i) to E

remove LR_c from LiveNow

add LR_a and LR_b to LiveNow

```

Quelle: EAC2e Fig 13.4 und 13.5

### Aufbau des Interferenzgraphen 2

Quelle: EAC2e Fig 13.4

# Vorbereitende Überlegungen

- Für k Maschinenregister ist eine k Einfärbung ausreichend

- Globales Minimum muss nicht gefunden werden

- Knoten n mit weniger als k Nachbarn (Grad kleiner k) können immer erfolgreich eingefärbt werden. Notiert als  $n^{\circ} < k$ .

- Wähle eine der Farben, die von den Nachbarn noch nicht benutzt wird

- Genauer: Spilling

- Füge Code hinter jedem DEF ein, um Wert in Speicher zu schreiben

- Füge Code vor jedem USE ein, um Wert aus Speicher zu lesen

- Erzeugt sehr viele trivial kleine Lebenszeiten

- Haben in der Regel weniger Interferenzen mit anderen Lebenszeiten

- Verwendet üblicherweise F reservierte Register

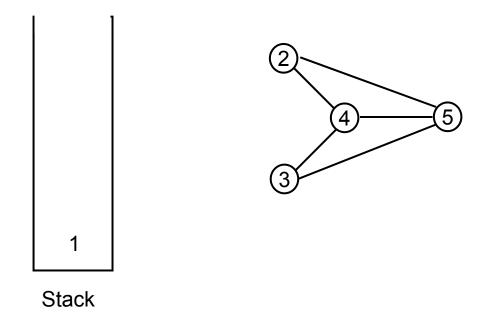

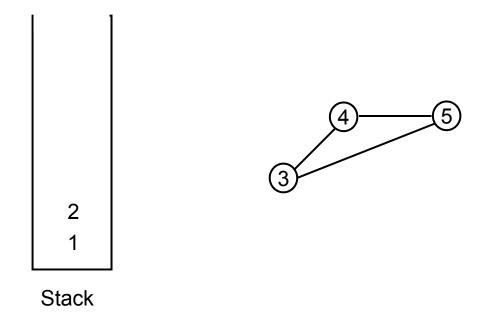

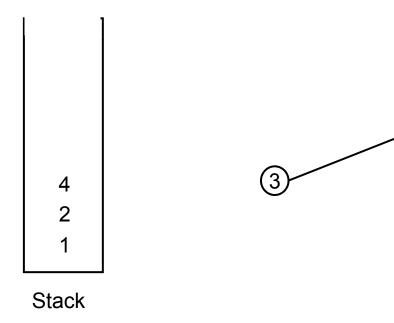

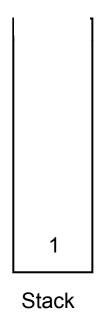

# Chaitins Algorithmus zur Registerallokation (PLDI 1982)

- 1 Wähle beliebigen Knoten n mit  $n^{\circ} < k$  und lege ihn auf Stack

- 2 Entferne *n* und alle seine Kanten aus Interferenzgraph

- Dies kann den Grad benachbarter Knoten auf kleiner als k absenken!

- 3 Falls nur noch Knoten n in Graph mit  $n^{\circ} >= k$

- wähle ein n (Heuristik) und merke n als zu spillen vor

- Entferne n und seine Kanten aus Interferenzgraph

- Falls nun Knoten n mit n° < k vorhanden, Gehe zu 1; sonst Wiederhole 3

- 4 Falls nötig: Erzeuge spill code für alle gemerkten Knoten

- Baue Interferenzgraph komplett neu auf und versuche Allokation erneut

- 5 Anderenfalls nehme Knoten vom Stack und färbe sie in der Farbe mit dem kleinsten, von den Nachbarn unbenutzten Index

#### 3 Register

1 ist einziger Knoten mit Grad < 3

#### 3 Register

Jetzt haben 2 und 3 einen Grad < 3

#### 3 Register

Jetzt haben alle Knoten einen Grad < 3

3 Register

#### 3 Register

Stack

#### Farben:

1:

2:

3:

### 3 Registers

Stack

#### 3 Register

#### Farben:

### 3 Register

#### Farben:

#### 3 Register

#### Colors:

### 3 Register

#### Farben:

### **Diskussion**

- Chaitins Algorithmus bildete die Grundlage für intensive Weiterentwicklungen

- Ein Ansatzpunkt: Chaitins Algorithmus ist pessimistisch

- Wenn nur noch Knoten mit Grad >= k vorliegen, sofort zum Spillen vormerken

- Optimistische Einfärbung (Briggs PLDI 1989)

- Erstmal weitermachen: Lege Knoten auf Stack wie üblich

- Möglicherweise ist ja beim Herunternehmen eine Farbe verfügbar

#### Beispiel

- Knoten n hat k+2 Nachbarn, diese benutzen selbst aber nur 1 Farbe!

- Grad eines Knotens+1 ist nur lose obere Schranke für Einfärbbarkeit

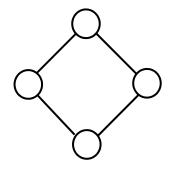

### **Chaitin vs. Briggs**

#### 2 Register:

Chaitin entscheidet sofort, einen der Knoten zu spillen

Briggs findet Lösung mit zwei Farben

### **Chaitin-Briggs Algorithmus**

TBD SoSe 2014