#### Verilog Crash-Kurs

Einführung in Computer Microsystems

Sommersemester 2007

Holger Lange

FG Eingebettete Systeme und ihre Anwendungen Informatik, TU Darmstadt

#### Übersicht

- Verilog zwischen "SDL" und HDL

- Synthetisierbare Sprachteile

- Kombinatorische Logik

- Sequenzielle Logik

#### Verilog zwischen "SDL" und HDL

- Verilog ist viel mächtiger als zur reinen Hardware-Beschreibung nötig

- Wichtig zur Modellierung von Systemumgebungen, "Testbenches"

- I/O Funktionen (\$display...), Real-Datentypen, ...

- Von den reinen HW-Beschreibungelementen nicht alle übersetzbar (Synthese)

- z.B. Modellierung von Zeit ("#10") in HW nicht garantierbar

- → Synthetisierbare Untermenge von Verilog

# Synthetisierbare Sprachteile

- Synthese: Abbildung von Register-Transfer-Logik (RTL) auf Gatternetzlisten

- RTL in Verilog

- Datentypen wire und reg

- Permanente Zuweisung assign beschreibt kombinatorische Logik

- always Block beschreibt prozedural kombinatorische oder sequenzielle Logik

- In kombinatorischem Block auch *integer* als Hilfsvariablen zulässig, z.B. Schleifenzähler

- Hierarchie durch Module und Instanzen

- parameter / #(...) / defparam

- Präprozessor `define NAME / `NAME

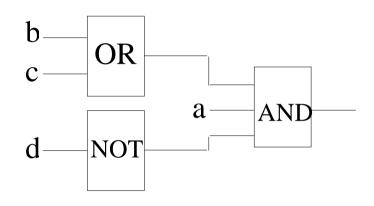

# Kombinatorische Logik I

- Funktion y = a & (b | c) & (!d)

- 1. Möglichkeit: Permanente Zuweisung wire y; assign y = a && (b || c) && (!d);

- Oder kürzer (Def. und Zuweisung kombiniert)

wire y = a && (b || c) && (!d);

#### Kombinatorische Logik II

• 2. Mögl.: Kombinatorischer always-Block

```

reg y; // hier wird kein Flip-Flop erzeugt always @ (a or b or c or d) begin // komplett! y = a \&\& (b || c) \&\& (!d); end

```

- Schleifenzähler: Beispiel Volladdierer for (i = 0; i < 4; i = i + 1)</li>

{c, sum[i]} = a[i] + b[i] + c;

- In kombinatorischen always-Blöcken immer blockende Zuweisung "=" verwenden

- Wie in C oder Java ...

#### Kombinatorische Logik III

- Wie in C oder Java ...

- &&, //, ! usw. sind logische Operatoren und arbeiten auf den gesamten Ausdrücken

- &, /, ~ usw. sind bitweise Operatoren und werten die Ausdrücke Bit für Bit aus

- Logischer Vergleich: ==, !=

- Nicht ====, !== verwenden!

- Multiplexer: Bedingung ? wahr : falsch

- Vorsicht bei komplexeren Ausdrücken

- +, erzeugen oft Addierer; \*, / Multiplizierer

(groß) Dividierer oft gar nicht möglich

- Besser: 2er Potenzen ausnutzen "<<",>>"

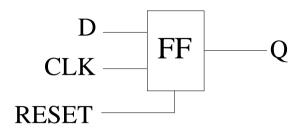

# Sequenzielle Logik I

D-Flip-Flop mit asynchronem Reset

end

end

Sequenzieller always-Block

reg Q;

always @(posedge CLK or posedge RESET) begin

if (RESET == 1) begin

Q <= 0;

end

else begin

Q <= D;</li>

# Sequenzielle Logik II

- In sequenziellen always-Blöcken immer nicht-blockende Zuweisung "<=" verwenden</li>

- Wertet in jedem Zeitschritt zunächst alle Ausdrücke auf der rechten Seite aus

- Transparente Zwischenspeicherung

- Schließlich Zuweisung an die linke Seite

- Modelliert die Zeitverzögerung beim Laden eines Flip-Flops

- Sei B := 3, A := 2

- -A = 4; B = A;  $\rightarrow$  B hat den Wert 4

- $-A \le 4$ ;  $B \le A$ ;  $\rightarrow$  B hat den Wert 3

- Im nächsten Zeitschritt ist A=4 und B hat den Wert 2!

# Sequenzielle Logik III

- Zustandsautomaten

- Werte für Zustandsvariable (Typ reg) mit `define kodieren

```

always @(posedge CLK or posedge RESET) begin

if (RESET) STATE <= `IDLE;</pre>

else begin

case (STATE)

`IDLE: STATE <= `GO:

`GO: begin

STATE <= ...;

end

default: STATE <= 'bx; // darf nicht auftreten

endcase

end

end

```

#### Raumbelegung

• 1. Teilklausur 31.05., 18:00-18:45

Mat.-Nr.

0000000 - 1149999

1150000 - 1311999

S311/08

1312000 - 1400000

S206/030