A. Koch

# Eingebettete Prozessorarchitekturen

5. Konfigurierbare Prozessorarchitekturen

#### Andreas Koch

FG Eingebettete Systeme und ihre Anwendungen Informatik, TU Darmstadt

Wintersemester 2010/2011

# Organisatorisches

- Arbeitsplatzrechner werden demnächst für 1. Aufgabe freigeschaltet

- Wahrscheinlich nächste Woche

- VLIW-Teil beendet

- Nächstes Thema: Konfigurierbare Prozessoren

- ...gelegentliche Ähnlichkeiten zu VLIW

### Material und Literatur

- Auszüge aus Trainingsmaterial der Fa. Tensilica

- Insbesondere alle Zeichnungen und technischen Daten

- Material ist vertraulich

- Nur für die Lehre zur Verfügung gestellt

- Darf nicht weiterverbreitet werden

- Weiterführende Informationen

- Tensilica Dokumentation (in FG ESA installiert)

- Buch "Engineering the Complex SOC" von Chris Rowen

# Konfigurierbare Prozessoren

- Können an Erfordernisse der Anwendung(en) angepasst werden

- Genauer: Solche Prozessoren sind Konfigurierbar Komponieren vordefinierter Funktionen Erweiterbar Hinzufügen neuer Funktionen

- Verschiedene Anbieter

- Tensilica (Marktführer)

- ARC

- ARM (in Grenzen durch Hersteller konfigurierbar)

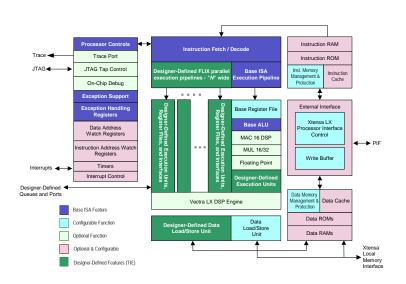

### Tensilica LX Architektur

### Basisaufbau

- RISC-artig

- Harvard-Architektur (getrennte I+D Speicher)

- Pipeline mit 5 oder 7 Stufen

- An Zieltaktfrequenz anpassbar

- Normale Instruktionslänge 24b

- Viele Instruktionen auch platzsparend als 16b

- VLIW-Betriebsart mit 32b oder 64b Instruktionen

- Registerfenster von 16 logischen Registern

- 16 oder 32 physikalische Register

- Bis zu zwei Load-Store-Units

### Erweiterbarkeit

- Zusätzliche Instruktionen

- Kommt später noch im Detail!

- Zusätzliche Schnittstellen

- I/O

- Interprozessorkommunikation

- Schneller Speicher

- Koprozessoren

### Basisbefehlssatz

- Load/Store

- Move

- Shift

- Arithmetik

- Kontrolltransfer

- Steuerung

- ⇒Ca. 80 Instruktionen immer verfügbar

### Konfigurierbare optionale Instruktionen

Vom Benutzer selektiv zum Basissatz hinzufügbar

Schleifen ohne Zeitverlust (zero-overhead loops)

- Multiplikation

- Normalisierung von Zahlen

- Minimum, Maximum

- Gesättigte Arithmetik

- Vorzeichenerweiterung

- Bedingungsregister und -befehle (ähnlich Lx/Vex!)

- Gleitkommakoprozessor

- 128b Vektor- und DSP-Einheit

- Multiprozessorsynchronisation

- ⇒Übersicht in Xtensa LX Microprocessor Overview

### Befehlsaufbau

#### Basisbefehlssatz kodiert in 24b

ADD ar, as, at

$$AR[r] \leftarrow AR[s] + AR[t]$$

| 23       |   |   |   | 0_   |

|----------|---|---|---|------|

| 10000000 | r | s | t | 0000 |

| 8        | 4 | 4 | 4 | 4    |

### Häufige Instruktionen auch kompakt in 16b darstellbar (.n)

ADD.N ar, as, at

$$AR[r] \leftarrow AR[s] + AR[t]$$

| 15 |   |   |      |  |

|----|---|---|------|--|

| r  | ន | t | 1010 |  |

| 4  | 4 | 4 | 4    |  |

Kleine konstante Werte (*immediates*) können direkt im Befehl untergebracht werden

# Flexible Length Instruction eXtensions VLIW-artige Betriebsart

- 32b oder 64b Instruktionen

- Können Mix aus 24b oder 16b Operationen enthalten

### Beispiel:

```

60000520 { I8ui a10, a11, 0; addi a9, a9, 2; abs a12, a10 }

60000528 { I8ui a8, a9, 0; sub a14, a14, a13; add a13, a8, a12 }

60000530 { I8ui a14, a11, 1; addi a11, a11, 2; abs a12, a14 }

60000538 { I8ui a13, a9, 1; sub a10, a10, a8; add a8, a13, a12 } sad+0x70

```

| 63  |     |     | 0    |

|-----|-----|-----|------|

| op0 | op1 | op2 | 1110 |

# Registerfeld

- 32 oder 64 allgemeine Register (AR), 32b breit

- "AR" steht laut Tensilica f

ür Address Register

- Optionale Registerfelder

- 16 Bedingungsregister (1b)

- 16 Gleitkommaregister (32b)

- 4 MAC-Zwischenregister (32b)

- MAC = Multiply Accumulate

- 16 Vektorregister (160b)

- Benutzerdefinierte Registerfelder

- Spezialregister

- Z.B. für Schleifengrenzen, Rundungsmodi, etc.

- Benutzerdefinierte Speicherelemente

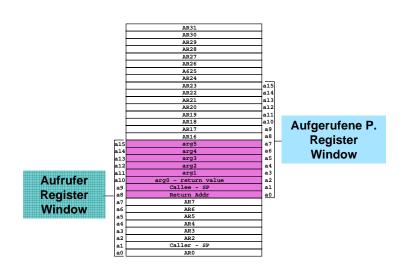

# Allgemeine Register AR

- In der Regel zwei Lese-Ports und ein Schreib-Port

- FLIX-Instruktionen k\u00f6nnen aber mehr Ports anfordern

- Physikalische ARs organisiert in Fenster von 16 logischen Registern a0 ...a15

- Benutzt für Parameterübergabe bei Prozeduraufruf

# Registerfenster

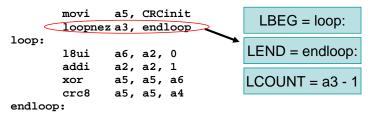

### Effiziente innere Schleifen

- Ersetzt "normale" Schleifeninstruktionen

- add, cmp, branch

- Ohne Pipelining-Zeitverlust von bedingten Sprüngen

- Nicht verschachtelbar

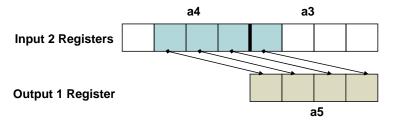

### **Datenextraktion**

A Koch

- Extraktion von 32b Datenfeldern aus bit-orientierten Datenströmen

- Beispielsweise Netzwerkpaketen

ssai 24 //set shift amount to 24bits src a5, a4, a3 //shift right combined to a5

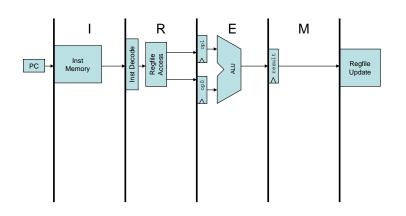

### LX Pipeline

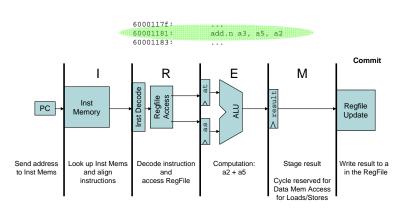

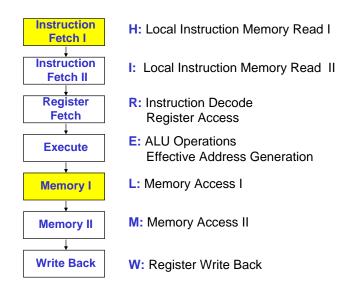

Instruction I: Local Instruction Memory Read **Fetch** Register R: Instruction Decode **Fetch** Register Access **Execute** M: Memory Access **Memory** W: Register Write Back **Write Back**

# LX Pipeline Klassischer Ablauf → TGDI2

# Pipeline-Effekte

A. Koch

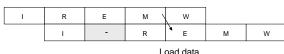

### Zugriff auf geladene Daten

#### Pipeline bubble due to load dependency

Load dat bypass

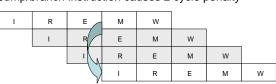

### **Bedingter Sprung**

#### Jump/branch instruction causes 2 cycle penalty

Target address if branch is taken

### Verlängerte Pipeline

Erlaubt höhere Taktfrequenz bzw. langsameren Speicher

### Benutzerdefinierte Instruktionen

- Tensilica Instruction Extensions (TIE)

- Neue Befehle

- Neue Register und Registerfelder

- Spezialschnittstellen

- Formuliert in eigener Sprache

- Stellenweise ähnlich zu Verilog

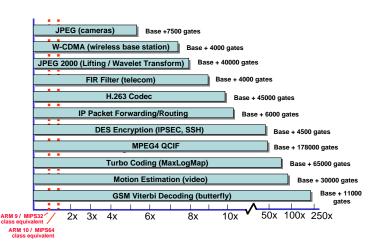

# Gewinn an Rechenleistung durch TIEs

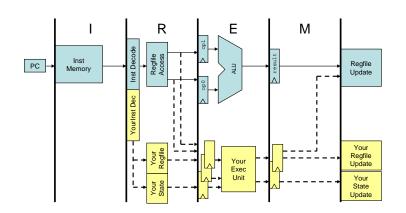

# Erweiterung der Pipeline

## Erweiterung der Pipeline

Neue Ausführungseinheiten

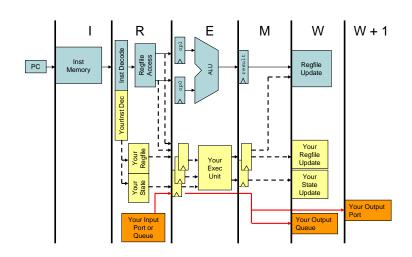

# Erweiterung der Pipeline

Neue Schnittstellen

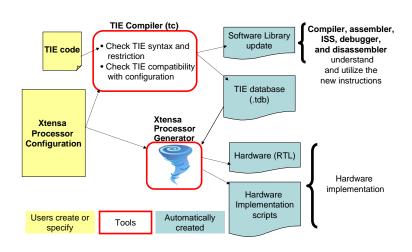

### **Entwurfsfluß**

# TIE: Ein erstes Beispiel Ursprüngliches C-Programm

A. Koch

```

unsigned int add_array(unsigned char * data) {

int i;

unsigned int sum = 0;

for (i = 0; i < SIZE; i++) {

sum += data[i];

}

return sum;

}</pre>

```

Idee: Betrachte ein 32b AR-Register als 4 einzelne 8b-Werte und addiere diese auf.

# TIE: Ein erstes Beispiel

- operation beschreibt Name, Format und Schnittstelle

- Ist so schon ausreichend für viele Anwendungen

### TIE Instruktion

mytiefile.tie

A. Koch

- ADD\_BYTES ist der Name der neuen Instruktion

- TIE-Compiler erzeugt Opcode f

ür neue Instruktion

- Alle Software-Werkzeuge werden aktualisiert und kennen nun neue Instruktion

- Aber: C-Compiler benutzt sie nicht automatisch

- Dafür andere Vorgehensweise → XPRES Compiler

### Schnittstelle der TIE-Instruktion

- Zwei Arten von Schnittstellen zur Instruktion

- Register (AR) und konstante Werte (immediates)

- ② Zustand und I/O → hier leer, kommt später . . .

- Hier: Instruktion liest ein AR und schreibt ein AR

- Auch möglich: inout für Operation im selben AR

### Innenleben der TIE-Instruktion

Beschreibung der Semantik

- Ähnlich zu Verilog

- Hier also einfache kombinatorische Logik

- Liest ein AR-Register (als einzelne Bytes)

- Addiert diese auf

- Schreibt Ergebnis in weiteres AR-Register

- Schlüsselworte

- wire Definiert lokale Variable, kann einmal zugewiesen werden

- assign Zuweisung an Wire oder Register, (Speicherelement, Output-Port)

# Beispiele für TIE-Operatoren

Sehr ähnlich zu Verilog

A Koch

```

Bit-Auswahl a[n:m]

Arithmetik +, -, *

Logik !, &&, ||

Vergleich >, <, >=, <=, ==, !=

Bit ~. &. |. ^. ~&. ~|. ~^

Reduktion &, |, ^, ~&, ~|, ~^

Schieben <<.>>

Konkatenation ( )

Replikation {n{...}}

Bedingter Ausdruck ?:

Konstante 32'd12 (=12), 8'h10 (=16), 4'b0101 (=5)

Nullerweiterung assign myreg[31:0] = 8'hff

setzt myreg auf 0x000000ff

➡Tensilica TIE Language Reference Manual

```

Quelle: /opt/cad/tensilica/tensilica-2006.5/XtDevTools/downloads/RA-2006.5/docs/tie.rm.pdl

# Eigenheiten von TIE-Code

- TIE-Code an sich ist sensitiv f

ür Groß/Kleinschreibung

- Eindeutige Namen f

ür neue Instruktionen vergeben

- Aber TIE-Assembler beachtet nicht Groß/Kleinschreibung für Instruktionsnamen

- Add\_Bytes ist z.B. gleich ADD\_BYTES

- Namen dürfen nicht mit "\_" oder "TIE\_" anfangen

# Anpassung der Software-Werkzeuge

- TIE-Compiler tc übersetzt TIE-Programm

- Dann automatische Anpassung der Werkzeuge Assembler

- C/C++ Compiler Erlauben Benutzung der neuen Instruktion

- Debugger Zeigt neue Instruktion an, erlaubt Einzelschritt, etc.

Disassembler Dekodiert und zeigt neue Instruktion

Disassembler (xt-objdump)

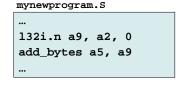

# Benutzung der neuen Instruktion

```

mynewprogram.c

```

```

#include <xtensa/tie/mytiefile.h>

...

unsigned int add_array(unsigned char * cdata) {

unsigned int *data = cdata;

unsigned int sum = 0;

for (i = 0; i < SIZE/4; i++) {

sum += ADD_BYTES(data[i]);

}

return sum;

}</pre>

```

- TIE-Compiler hat .h Definitionsdatei erstellt

- Kapselt neue Instruktion als C-Funktion

- Kapselungsfunktion nun normal aufrufen

- C-Compiler schreibt zugrundeliegende neue Instruktion in ausführbares Programm

## Zusammenfassung

- Konfigurierbare Prozessoren

- Konfiguration

- Erweiterung

- Tensilica LX

- Instruction Set Architecture

- Mikroarchitektur (Pipeline)

- Erweiterte Pipeline

- Beispiel f

ür neue Instruktion

- TIE-Code

- →davon nächste Woche mehr