# KV Computer Microsystems Teil III Bindung und FSMD-Synthese

#### Andreas Koch

FG Eingebettete Systeme und ihre Anwendungen Informatik, TU Darmstadt

Sommersemester 2005

#### Organisatoriso

Bindun

ILP-basierte Lösun LEFTEDGE Algorithmus

Maybiad, was as a

Stouorworksynt

Festverdrahtet

Microcode

Kompaktierung

# Gliederung

- Organisatorisches

- 2 Bindung

- Modell

- ILP-basierte Lösung

- LEFTEDGE Algorithmus

- Registerbindung

- Verbindungssynthese

- Steuerwerksynthese

- Festverdrahtet

- Microcode

- Kompaktierung

- Hierarchie

- Zusammenfassung

Organisatorisc

Bindun Modell

> ILP-basierte Lé LEFTEDGE Algorithmus

. . . . .

verbindungssy

Festverdrahtet

Microcode

Kompaktierung

#### Klausur

- Gesonderte Anmeldung bis zum 6.7.2005 erforderlich

- Unabhängig von Prüfungssekretariat

- Auch für Diplomis, Nebenfächler, etc.

- http://www.vlsi.informatik.tu-darmstadt. de/student area/klausur/?klausurid=6

- Auch von den Vorlesungsseiten verlinkt

- Termin: 13.07.2005, 9:00-11:30 Uhr

- Echte Klausurdauer: 120 Minuten

- Erlaubte Hilfsmittel: Keine!

- Aufgabenstellung kann aber Extrahinweise enthalten

- Alles Papier wird gestellt

- Raumaufteilung: Listen hängen ca. 3 Tage vorher aus

#### Organisatorisch

Bindung

ILP-basierte Lösun LEFTEDGE Algorithmus

Verbindungssyn

Steuerwerksyr

Festverdrahtet

Microcode

# Bindung

- Ordnet Operationen konkrete Instanzen des Ressourcetyps zu

- Kann durchgeführt werden

- Vor

- Während

- Nach (← hier betrachtet)

- ... Ablaufplanung

- Gemeinsame Ressourcenutzung bei nicht ressource-beschränkten Ablaufplänen

- Im anderen Fall: Ressourceanzahlen bereits w\u00e4hrend Ablaufplanung bestimmt

- Ergebnis ist Grundlage f

ür Verbindungssynthese

Organisatorisc

#### Bindung

ILP-basierte Lösun LEFTEDGE Algorithmus

Verbindungssyr

Steuerwerksynt

Festverdrahtet Microcode Kompaktierung Hierarchie

### Grundlegende Annahmen

#### Bindung

- Ein Ressourcetyp kann unterschiedliche Operationen abdecken

- Wir betrachten ressourcedominierte Schaltungen

- Eine Operation verbleibt während ihrer gesamten Ausführungszeit auf derselben Instanz

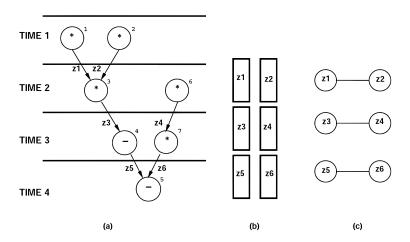

# Graphbasiertes Modell des Problems

- Sequenzgraph  $G_S(V,E)$

- $v_0$  und  $v_n$  spielen keine Rolle mehr (NoOps)

- Ressourcezuordnung  $T: V \to R, R = \{r_k : 1 \le k \le n_{res}\}$

- Gesucht Bindung  $\beta: V \to R \times N$

- Zuordnung einer Operation an eine Instanz einer Bessource

Organisatorisc

Modell

ILP-basierte Lösung LEFTEDGE Algorithmus

Verhindungeevr

Charlamiankaria

Festverdrahtet Microcode Kompaktierung

### Kompatible Operationen

Zwei Operationen können die selbe Ressourceinstanz nutzen, wenn sie . . .

- ...den gleichen Typ haben und

- ... nicht zur gleichen Zeit ablaufen

Dann heissen sie kompatibel

#### Kompatibilität

Zwei ablaufgeplante Operationen  $v_i$  und  $v_j$  sind *kompatibel* wenn gilt:

$$T(v_i) = T(v_j) \wedge ((t_i + d_i \le t_j) \vee (t_j + d_j \le t_i))$$

#### Konflikt

Zwei ablaufgeplante Operationen stehen in *Konflikt* zueinander, wenn sie nicht kompatibel sind.

Organisatorisc

Modell

ILP-basierte L LEFTEDGE Algorithmus

/erbindunassvn

Steuerwerksyr Festverdrahtet Microcode Kompaktierung

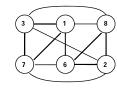

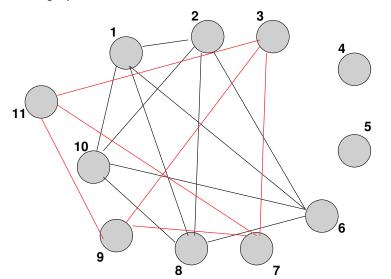

# Graphen-basierte Sicht der Relationen

#### Kompatibilitätsgraph $G_+$

Ungerichteter Graph  $G_+(V,E)$  mit den Operationen als Knoten  $V=\{1,\cdots,n_{ops}\}$  und Kanten

$$E = \{\{v_i, v_j\} : v_i \text{ ist kompatibel zu } v_j\}$$

#### Konfliktgraph $G_{-}$

Ungerichteter Graph  $G_-(V,E,k)$  mit den Operationen als Knoten  $V = \{v_i : T(v_i) = k \land 1 \le i \le n_{ops}\}$  und Kanten

$$E = \{\{v_i, v_j\} : v_i \text{ steht in Konflikt zu } v_j\}$$

Organisatorisc

Modell

ILP-basierte Lösung LEFTEDGE Algorithmus

Verbindungssyn

Steuerwerksynt

Microcode Kompaktierung Hierarchie

Zusammeniassi

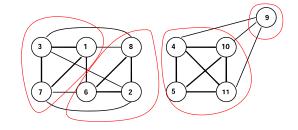

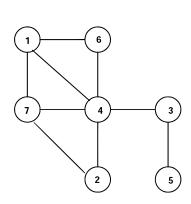

# Beispiel: Kompatibilitätsgraph

#### Bindu Modell

ILP-basierte Lösun LEFTEDGE Algorithmus

....

Verbindungssy

Festverdrahtet

Microcode

Zucammonface

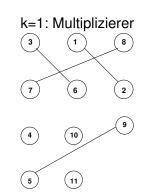

#### Beispiel: Konfliktgraphen je Ressource

k=2: ALUs

Organisatoriso

Bindu Modell

ILP-basierte Lösur LEFTEDGE

. . . . .

verbindungssyr

Festverdrahtet

Microcode

Kompaktierung

# Eigenschaften von $G_+$

- Kompatibilitätsgraph hat mindestens  $n_{res}$  verschiedene disjunkte Teilgraphen

- Untereinander kompatible Operationen bilden Clique

- Ziel von Bindung: Minimiere die Zahl von Ressourcen

- Kompatible Ressourcen können sich Instanz teilen

- Also: Suche nach möglichst wenigen, dafür aber möglichst grossen disjunkten Cliquen

- Grösste Menge untereinander kompatibler Ressourcen ist maximale Clique

- Minimalzahl benötigter Cliquen um ganz V zu partitionieren ist κ(G<sub>+</sub>(V,E))

Organisatorisc

Bindun Modell

ILP-basierte Lösun

Variational consequen

Steuerwerksynt

Festverdrahtet Microcode Kompaktierung Hierarchie

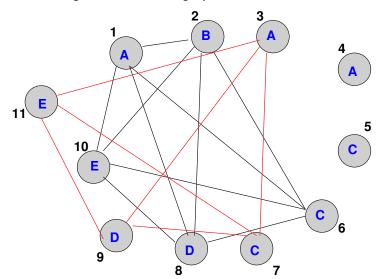

### Beispiel: Maximale Cliquen

$$\kappa(G_+(V,E)) = 4$$

{ $v_1, v_3, v_7$ }, { $v_2, v_6, v8$ }, { $v_4, v_5, v_{10}, v_{11}$ }, { $v_9$ } Ergebnis: 2 Multiplizierer und 2 ALUs

Organisatorisc

Bindui Modell

ILP-basierte Lösung

1 tegisterbiridar

verbindungssyn

Festverdrahtet Microcode Kompaktierung

# Eigenschaften von $G_-$

- Kompatible Operatoren sind nicht durch Kanten verbunden

- Solche Operatoren bilden unabhängige Mengen

- Durch Kanten verbundene Operatoren müssen auf unterschiedlichen Instanzen realisiert werden

- Idee: Löse das Graphfärbungsproblem, Farben c(v) entsprechen Instanzen

- $\forall \{v_i, v_j\} \in E : c(v_1) \neq c(v_2)$

- Gesucht: Färbung mit minimaler Anzahl  $\chi(G_-(V,E,k))$  von Farben

Organisatorisc

Modell

ILP-basierte Löst

Algorithmus

Registerbindun

Verbindungssyr

Festverdrahtet

Microcode

Kompaktierung

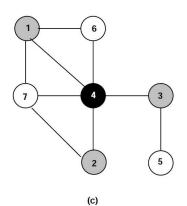

# Beispiel: Minimale Graphfärbung

$$\chi(G_{-}(V,E,1)) = 2,$$

{ $v_1, v_3, v_7$ }, { $v_2, v_6, v_8$ },

# k=2: ALUs

$$\chi(G_{-}(V,E,2)) = 2$$

$\{v_4, v_5, v_{10}, v_{11}\}, \{v_9\}$

Ergebnis: 2 Multiplizierer und 2 ALUs

$$\sum_{k=1}^{n_{res}} \chi(G_{-}(V,E,k)) = \kappa(G_{+}(V,E))$$

Organisatorisc

Bindur

ILP-basierte Lösung

LEFTEDGE

Algorithmus

Vorbindungssy

Steuerwerksynt

Microcode Kompaktierung Hierarchie

# Lösung der Aufgabe

Lösung beider Probleme

- Partitionierung durch maximale Cliquen

- Einfärbung mit minimaler Farbenzahl

in  $\mathcal{N} \mathcal{P}$  für den allgemeinen Fall

Organisatorisc

Bindu

ILP-basierte Lösur LEFTEDGE Algorithmus

Manufation allows are according

Steuerwerksvnt

Festverdrahtet Microcode Kompaktierung

#### Ein Ansatz: ILP-basiert

a<sub>k</sub> Anzahl von Instanzen des Ressourcetyps k

•

$$B = \{b_{i,r} : 1 \le i \le n_{ops}, 1 \le r \le a_k\}$$

- $b_{ir} = 1$ , wenn Operation  $v_i$  auf Instanz r des Ressourcetyps k ausgeführt wird, sonst 0

- Bedeutet Bindung:  $\beta(v_i) = (k, r)$

- $X = \{x_{i,l} : 1 \le i \le n_{ops}, 1 \le l \le \lambda\}$

- $x_{i,l} = 1$ , wenn Operation  $v_i$  in Schritt l gestartet wird, 0 sonst

Organisatorisc

Bindun

ILP-basierte Lösung LEFTEDGE Algorithmus

Vaulainadi na mana

verbindungssyr

Festverdrahtet Microcode Kompaktierung

### ILP für Bindungsproblem

Für jeden Ressourcetyp k muss gelten:

• Jede Operation  $v_i$  muss auf genau einer Instanz ausgeführt werden

$$\sum_{r=1}^{a_k} b_{i,r} = 1 \quad , \forall 1 \le i \le n_{ops}$$

② Auf jeder Instanz r kann im Zeitschritt l nur eine Operation  $v_i$  ablaufen

$$\sum_{\{v_i:T(v_i)=k\}} b_{i,r} \sum_{m=l-d_i+1}^l x_{i,m} \le 1 \quad , \forall 1 \le l \le \lambda, 1 \le r \le a_k$$

Organisatorisc

Bindung Modell

ILP-basierte Lösung LEFTEDGE Algorithmus

Verbindungssyr

Steuerwerksynt

Festverdrahtet Microcode Kompaktierung Hierarchie

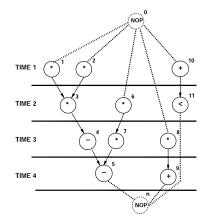

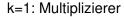

Annahmen: Ressourcetypen 1 (=Mult) und 2 (=ALU),  $d_i = 1$ Aus Schedule: Instanzanzahlen  $a_1 = a_2 = 2$ ,  $\lambda = 4$

Hier gerechnet für Multiplizierer  $\{v_1, v_2, v_3, v_6, v_7, v_8\}$

Jede Operation auf genau einer Instanz

$$b_{1,1} + b_{1,2} = 1$$

$$b_{2,1} + b_{2,2} = 1$$

$$b_{3,1} + b_{3,2} = 1$$

$$b_{6,1} + b_{6,2} = 1$$

$$b_{7,1} + b_{7,2} = 1$$

$$b_{8,1} + b_{8,2} = 1$$

Organisatorisc

Bindung

ILP-basierte Lösung LEFTEDGE Algorithmus

Verhindungssy

Oteronicalisasy

Festverdrahtet Microcode Kompaktierung Hierarchie

#### Vorgegebener Ablaufplan

Organisatorisc

Bindun

ILP-basierte Lösung LEFTEDGE Algorithmus

Steuerwerksyr

Festverdrahtet Microcode Kompaktierung

Zusammenfassı

$x_{il}$  durch Scheduling bereits festgelegt, Werte einsetzen

#### Auf jeder Instanz nur eine Operation pro Zeitschritt

$$b_{1,1} + b_{2,1} \le 1$$

:  $l = 1$   $b_{1,2} + b_{2,2} \le 1$  :  $l = 1$   $b_{3,1} + b_{6,1} \le 1$  :  $l = 2$   $b_{3,2} + b_{6,2} \le 1$  :  $l = 2$   $b_{7,1} + b_{8,1} \le 1$  :  $l = 3$   $b_{7,2} + b_{8,2} \le 1$  :  $l = 3$

Keine Multiplikation mehr in Zeitschritt l = 4

Organisatorisc

Bindur Modell

ILP-basierte Lösung LEFTEDGE Algorithmus

Maybiadi wasan

Steuerwerksynt

Festverdrahtet

Microcode

Kompaktierung

Organisatoriso

Modell

ILP-basierte Lösung LEFTEDGE Algorithmus

....

verbilluurigssyr

Festverdrahtet Microcode

Kompaktierung Hierarchie

Zusammentassi

Demo mit lp\_solve

#### Ergebnis aus ILP-Solver

b11

b12

b21

b22 0

b31

b32

b61

b62 0 b71 0

b72

0/2

b81 1

b82

Organisatorisc

Bindung Modell

ILP-basierte Lösung LEFTEDGE Algorithmus

....

Stouerworksynt

Festverdrahtet

Microcode

Kompaktierung

Hierarchie

#### Bessere Lösung

- Lösung von ILP ist in NP

- Nicht überraschend, andere allgemeine Lösungen sind auch in  $\mathcal{N}$

- Aber:

- Im Fall von Intervallgraphen lässt sich das Problem in polynomieller Zeit exakt lösen!

#### Intervallgraph

Ein ungerichteter Graph G(V,E) heisst Intervallgraph genau dann, falls jedem Knoten  $v_i \in V$  ein Intervall  $[l_i,r_i)$ , mit  $l_i,r_i \in \mathbf{Z} \wedge l_i \leq r_i$ , zugeordnet werden kann und eine Kante  $\{v_i,v_j\} \in E$  genau dann existiert, wenn sich die Intervalle  $[l_i,r_i)$  und  $[l_j,r_j)$  überlappen.

Konfliktgraphen  $G_{-}$  sind Intervallgraphen.

Organisatorisc

Bindung

ILP-basierte Lösur LEFTEDGE Algorithmus

/orhindungseyr

Steuerwerksyn: Festverdrahtet Microcode Kompaktierung

#### LEFTEDGE Algorithmus

- Eingabe: Liste I von Intervallen

- Ausgabe: Überlappungsfreie Farbzuordnung der Intervalle

- Idee

- Sortiere Intervalle nach aufsteigender Untergrenze

- Que Gehe Liste durch und weise nicht-überlappenden Intervallen die gleiche Farbe zu

- Nimm die n\u00e4chste Farbe und wiederhole f\u00fcr ungef\u00e4rbte Intervalle

Organisatorisc

Modell

ILP-basierte Lösun LEFTEDGE Algorithmus

Verhindungssy

- .

Festverdrahtet

Microcode

Kompaktierung

Hierarchie

### Algorithmus LEFTEDGE

#### Optimales überlappungsfreies Einfärben von Intervallen I

```

LEFTEDGE(I)

Sortiere Elemente von I aufsteigend nach l_i in Liste L;

i = 0;

while L \neq \emptyset do

4

S = \emptyset;

5

r=0; /* rechter Rand von Elementen in S */

6

while \exists i \in L : l_i > r do

i = Element aus L mit kleinsten l_i > r;

8

S = S \cup \{i\};

r = r_i:

10

L = L \setminus \{i\};

11

12

i = i + 1;

for i \in S do

13

14

c(i) = j; /* Farbe des Intervalls setzen */

```

Organisatorisc

Bindung

Modell

ILP-basierte Lösu

LEFTEDGE

Algorithmus

riogistorbindari

verbindungssyr

Festverdrahtet

Microcode

Kompaktierung

Hierarchie

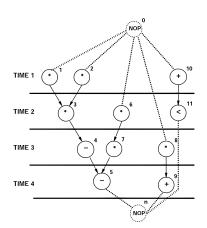

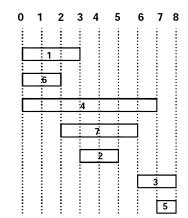

# Beispiel: LEFTEDGE Algorithmus

#### Eingabe

Organisatorisc

Bindung Modell

Modell

ILP-basierte Lösur

LEFTEDGE

Algorithmus

Registerbindun

Verbindungssy

Festverdrahtet

Microcode

Kompaktierung

Hierarchie

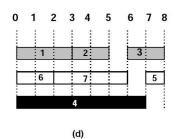

### Beispiel: LEFTEDGE Algorithmus

#### Ausgabe

Organisatoriscl

Bindung Modell

ILP-basierte Lösur LEFTEDGE Algorithmus

....

Oten and a second

Festverdrahtet Microcode Kompaktierung

#### Lebenszeit von Variablen

- Jede Kante zwischen zwei Operatoren braucht Variablen für Datentransfer

- Lebensdauer einer Variablen.

Geburt Zeitpunkt an dem Wert an

Operatorausgang anliegt

Tod Letzter Zeitpunkt an dem der Wert an

einem Operatoreingang benötigt wird

- Variablen müssen für ihre Lebensdauer gespeichert werden.

- Unterschiedliche technische Realisierungsmöglichkeiten

- Speicher: Ein- oder Multi-Port

- Register: Alle parallel zugreifbar ← hier betrachtet

Organisatorisc

Bindun

ILP-basierte Lösur LEFTEDGE Algorithmus

Registerbindung

Charramanantarina

Festverdrahtet

Microcode

Kompaktierung

Hierarchie

Zusammentassi

### Registerbindung

- Register speichern . . .

- Eingabewerte

- Zwischenergebnisse

- Ausgabwerte

- Vereinfachung hier

- Dedizierte Register f

ür Ein- und Ausgabewerte

- Aber optimierbar: Register für Zwischenergebnisse

Organisatorisc

Bindur Modell

ILP-basierte Lösun LEFTEDGE Algorithmus

Registerbindung

Charlamiankaria

Festverdrahtet Microcode Kompaktierung

# Verfahren zur Registerbindung

- Gegeben: Ein Ablaufplan

- Daraus bestimmbar: Lebenszeiten

- Überlappende Lebenszeitintervalle implizieren separate Register

- Lösung mit Konfliktgraph und Einfärbung

- Knoten: Variablen

- Kanten: Überlappende Lebenszeiten

- Gesucht: Minimale Anzahl von Registern für Zwischenergebnisse

- Lösen mit LeftEdge-Algorithmus

Organisatorisc

Bindun

ILP-basierte Lösun LEFTEDGE Algorithmus

Registerbindung

Verbindungssyi

Festverdrahtet

Microcode

Kompaktierung

# Beispiel: Registerbindung

Organisatorisc

Bindun

ILP-basierte Lösur LEFTEDGE Algorithmus

Registerbindun

Verbindungssyn

Festverdrahtet Microcode Kompaktierung

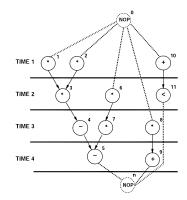

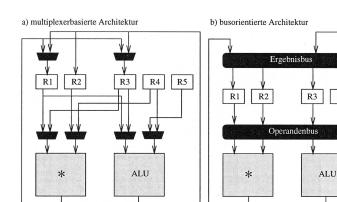

# Verbindungssynthese

Erstellen von Verbindungen

- zwischen Ressourceinstanzen und Registern

- zwischen Registern

- zur Schnittstelle zum Steuerwerk

- zu den Ein-/Ausgabe-Ports zum Restsystem

Organisatorisc

Bindui

ILP-basierte Lösun LEFTEDGE Algorithmus

Manufaction also are as as as

Verbindungssyn

Festverdrahtet Microcode Kompaktierung

# Verbindungsarchitekturen

Organisatoriso

Bindun

ILP-basierte Lösur LEFTEDGE Algorithmus

Registerbindur

Verbindungssyr

Festverdrahtet

Microcode

R5

Kompaktierung Hierarchie

Zusammenfassı

Mehr Parallelität ./. einfacherer Aufbau

#### Beispiel: Verbindungssynthese

Ablaufplan mit 1 Multiplizierer, 1 ALU

Diesmal: Mit Ein-/Ausgabewerten und Registerlebenszeiten Organisatorisc

Bindu

ILP-basierte Lösun LEFTEDGE Algorithmus

Verbindungssyn

Steuerwerksyn: Festverdrahtet Microcode

#### Beispiel: Verbindungssynthese

Organisatoriso

Bindur

ILP-basierte Lösun LEFTEDGE Algorithmus

, rogiotoromidani

Verbindungssyr

Festverdrahtet Microcode

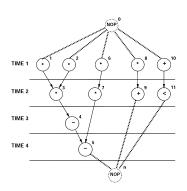

# Steuerwerksynthese

- Verhaltenssicht: Synchrone FSM

- Zunächst: Vereinfachte Sicht

- Flache Sequenzgraphen

- Datenunabhängige Verzögerungen

- Auf unterschiedliche Arten realisierbar

- Festverdrahtete FSM

- Microcode (ROM, PLA)

- Verteilte FSM

Organisatorisc

Bindur

ILP-basierte Lösun LEFTEDGE Algorithmus

Verhindungssy

Steuerwerksynt

Microcode

Kompaktierung

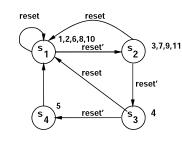

## Beispiel: Festverdrahtete FSM

Annahme: Dedizierte Ressourcen mit Verzögerung 1.

Direkt in Flip-Flops und Gatter umsetzbar.

Organisatoriso

Bindun

ILP-basierte Lösung LEFTEDGE Algorithmus

Verhindungssyr

Steuerwerksynt Festverdrahtet

Microcode Kompaktierung Hierarchie

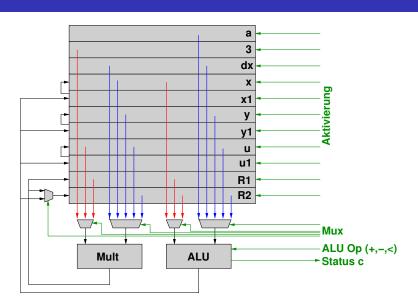

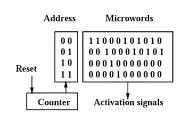

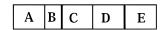

### Microcode

- Kleine Programme, gespeichert in ROMs oder PLAs

- Horizontaler Microcode

- Ein Bit pro Aktivierungs/Steuersignal (z.B. Muxe)

- Ein Microcode-Wort pro Zeitschritt

- Maximale Parallelität → niedrige Latenz

- Breite Worte (mehr Verdrahtung)

- Vertikaler Microcode

- Ein kodiertes Microcode-Wort pro Ressource

- Schmalere Worte (weniger Verdrahtung)

- Auch mehrere Worte pro Zeitschritt erforderlich

- Weniger Parallelität

Organisatorisc

Bindun Modell

ILP-basierte Lō: LEFTEDGE Algorithmus

Verbindungssyr

Steuerwerksyn

Microcode Kompaktierung

Hierarchie

38/49

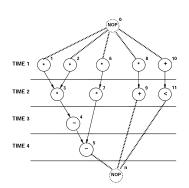

### Beispiel: Horizontaler Microcode

Organisatorisc

Bindun

ILP-basierte Lösur LEFTEDGE Algorithmus

verbindungssyr

Festverdrahtet

Microcode

Kompaktierung Hierarchie

### Beispiel: Vertikaler Microcode

Organisatoriso

Bindun

ILP-basierte Lösu LEFTEDGE Algorithmus

Vorbindungseyr

Steuerwerksynt

Festverdrahtet

Microcode

Kompaktierung

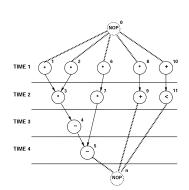

## Kompromiss

- Beobachtung: Horizontaler Microcode enthält viele Nullen

- Breite Microworte lohnen sich nur bei echter Parallelität

- Finde Teile mit paralleler Ausführung

- Steuere diese parallel an (horizontaler Ansatz)

- Für sequentielle Teile

- Benutze kompaktere kodierte Darstellung (vertikaler Ansatz)

Organisatorisc

Modell

ILP-basierte Lösung LEFTEDGE Algorithmus

Vorbindungssyr

Steuerwerksy

Festverdrahtet Microcode Kompaktierung Hierarchie

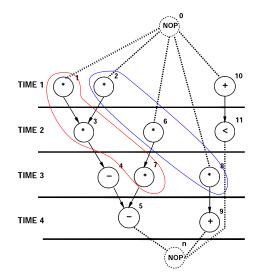

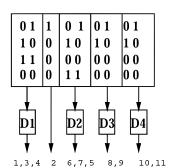

# Microcode-Kompaktierung

#### Ein Ansatz:

- Baue Konfliktgraph von parallelen Steuersignalen auf

- Kante existiert bei paralleler Ausführung

- Dann minimales Einfärbeproblem lösen

- Kein Intervallgraph mehr

- Heuristik verwenden (Verfahren hier nicht behandelt)

- Jede Farbe entspricht einer Gruppe von Steuersignalen

- Innerhalb der Gruppe: Sequentielle Ausführung

- Gruppen untereinander: Parallele Ausführung

Organisatorisc

Modell

ILP-basierte Lösung LEFTEDGE Algorithmus

Verbindungssyn

Festverdrahtet

Microcode

Kompaktierung

#### Konfliktgraph

Organisatorisc

Bindun Modell

ILP-basierte Lösun; LEFTEDGE Algorithmus

Verbindungssyr

Steuerwerks

Festverdrahtet

Microcode

Kompaktierung

#### Minimal eingefärbter Konfliktgraph

Organisatorisc

Bindur

иоден LP-basierte Lösur .EFTEDGE Algorithmus

Varhindungaava

Steuerwerks: Festverdrahtet Microcode

Microcode Kompaktierung Hierarchie

| field                | ор | code |

|----------------------|----|------|

| Α                    | 1  | 01   |

| A                    | 3  | 10   |

| A                    | 4  | 11   |

| В                    | 2  | 1    |

| С                    | 6  | 01   |

| $\cup$ $\cup$ $\cup$ | 7  | 10   |

| C                    | 5  | 11   |

| D                    | 8  | 01   |

| D                    | 9  | 10   |

| E                    | 10 | 01   |

| E                    | 11 | 10   |

Organisatorisc

Bindu

ILP-basierte Lösur LEFTEDGE Algorithmus

Vorbindungssyr

Steuerwerks

Festverdrahtet

Microcode

Kompaktierung Hierarchie

Zusammenfass

Beachte: Braucht Code für NoOp, hier 00.

Damit jetzt schmalere Microworte ohne Parallelitätsverlust

#### Microword format

#### Microwords

Organisatorisc

Bindun Modell

ILP-basierte Lösun LEFTEDGE Algorithmus

Verhindungssyr

Steuerwerks Festverdrahtet

Microcode

Kompaktierung

Hierarchie

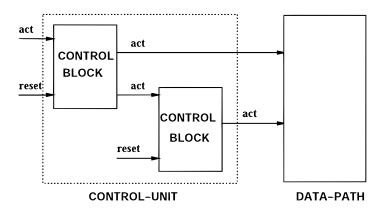

#### Hierarchische Steuerwerke

#### Für hierarchische Sequenzgraphen

Organisatorisc

Bindun

Modell

ILP-basierte Lösun

LEFTEDGE

\/------

Charramandrama

Festverdrahtet Microcode Kompaktierung

Hierarchie

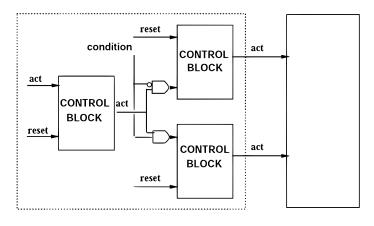

#### Hierarchische Steuerwerke

CONTOL-UNIT

#### Mit Verzweigung

Hierarchie

## Zusammenfassung

- Grundlagen der Architektursynthese

- Modelle

- Ablaufplanung

- Bindung

- Konnektivitätssynthese

- Steuerwerksynthese

#### Noch nicht

- Logiksynthese

- Sequentielle Optimierung

- Bibliotheksabbildung

- Layoutsynthese ← im Wintersemester :-)

Organisatorisc

Bindun Modell

ILP-basierte Lõ LEFTEDGE Algorithmus

. . . . . .

o. . .

Festverdrahtet Microcode Kompaktierung Hierarchie