# Praktikum adaptive Computersysteme

**Aufgabenstellung SS 2010** Thorsten Wink

# Inhaltsverzeichnis

| 1        | Einle | eitung                                                 | 3  |

|----------|-------|--------------------------------------------------------|----|

|          |       |                                                        |    |

| 2        | Prak  | ctikumsablauf                                          | 5  |

|          | 2.1   | Hardware und Arbeitsraum                               | 5  |

|          | 2.2   | 0. Phase: Einführung (17.0423.04.2010)                 | 5  |

|          | 2.3   | 1. Phase: Hardware-Experimente (24.0430.04.2010)       | 6  |

|          | 2.4   |                                                        |    |

|          | 2.5   | 3. Phase: Bildbearbeitung (08.0514.05.2010)            |    |

|          |       | 4. Phase: IP-Blöcke (15.0528.05.2010)                  |    |

|          |       | 5. Phase: Slave-Mode Version (29.0511.06.2010)         |    |

|          |       | 6. Phase: Master-Mode Version (12.0609.07.2010)        |    |

|          | 2.9   | 7. Phase: Nacharbeiten (10.0716.07.2010)               | 12 |

| 3        | Wer   | kzeugfluß                                              | 13 |

|          | 3.1   |                                                        | 13 |

|          | 3.2   |                                                        |    |

|          | 3.3   | Simulation auf Registertransferebene (RTL)             |    |

|          | 3.4   |                                                        |    |

|          |       | Hardware-Test der Slave-Mode-RCU                       |    |

|          |       | Hardware-Test des Gesamtsystems                        |    |

|          |       |                                                        |    |

| 4        | Ada   | ptive Rechensysteme - Eine praktische Einführung       | 23 |

|          | 4.1   | Rechnen mit rekonfigurierbarer Hardware                | 23 |

|          |       | 4.1.1 Anwendungen                                      | 23 |

|          |       | 4.1.2 Idee                                             |    |

|          |       | 4.1.3 Terminologie                                     | 24 |

|          |       | 4.1.4 Abstufungen von Rekonfigurierbarkeit             | 25 |

|          |       | 4.1.5 Aufbau adaptiver Rechensysteme                   |    |

|          |       | 4.1.6 Auswirkungen auf die Architektur von Prozessoren |    |

|          |       | 4.1.7 Beispiel: ML310 als adaptiver Computer           |    |

|          | 4.2   | Programmierung adaptiver Rechner                       |    |

|          | 4.3   | HDL-basierte Programmierung                            |    |

|          |       | 4.3.1 Reine Softwarelösung                             |    |

|          |       | 4.3.2 Beschleunigung durch RCU im Slave-Mode           |    |

|          |       | 4.3.3 Weitere Beschleunigung durch RCU im Master-Mode  | 40 |

| <br>5    | Beis  | miolo                                                  |    |

| <u> </u> |       | •                                                      | 55 |

|          | 5.1   | 8                                                      |    |

|          |       | 5.1.1 main.c                                           |    |

|          |       | 5.1.2 user.v                                           |    |

|          | 5.2   | Master-Mode-Anwendung                                  |    |

|          |       | 5.2.1 main.c                                           |    |

|          |       | 5.2.2 user.v                                           |    |

|          | 5.3   | Bildbearbeitung                                        | 62 |

### 1 Einleitung

Herzlich willkommen beim Praktikum über adaptive Rechensysteme. Dieser Leitfaden soll Ihnen den Einstieg in die Benutzung der Entwurfsumgebung und die Bearbeitung der eigentlichen Aufgaben erleichtern.

Das vorliegende Dokument ist in vier Teile gegliedert: Das zweite Kapitel beschreibt den Praktikumsablauf mit seinen einzelnen Phasen und Teilaufgaben, das dritte (das Sie allerdings zuerst lesen sollten!) führt in den verwendeten Entwurfsfluß ein. Das vierte gibt eine Einführung in adaptive Rechner, die Sie verstanden haben sollten. Für den Fall, daß Sie dieses Werk ohne nebenstehenden Rechner lesen möchten, sind im letzten Kapitel die Quellen aller besprochenen Programme abgedruckt.

Noch eine Bemerkung vorweg: Um Ihnen den Einstieg zu erleichtern und Sie behutsam an die Materie heranzuführen, beginnt das Praktikum mit vergleichsweise einfachen Aufgaben. Das Niveau steigt aber gegen Ende! Diesen Gradienten sollten Sie unbedingt bei Ihrer Zeit- und Arbeitsintensitätsplanung berücksichtigen.

Bitte lassen Sie uns wissen, wo Probleme auftreten, damit wir für nachfolgende Jahrgänge Abhilfe schaffen können.

3

#### 2 Praktikumsablauf

#### 2.1 Hardware und Arbeitsraum

Für die Bearbeitung der Aufgaben benötigen Sie Spezialsoftware, die nicht frei zugänglich ist. Sie ist auf unseren Rechnern im Praktikumsraum E119 installiert und kann an den 4 dort aufgestellten Rechnern verwendet werden. Desweiteren ist auch eine Arbeit von extern möglich. Eine Anleitung hierzu finden Sie im Leitfaden zur Rechnerumgebung, der auf der Webseite des Praktikums verfügbar ist. Sollten Fragen auftreten, wenden Sie sich bitte an uns.

An jedem der Arbeitsplatzrechner im Praktikumsraum E119 des FG ESA ist ein eigenes ML310 ACS angeschlossen, das jeweils nur von *einem* Benutzer parallel benutzt werden kann. Überprüfen Sie daher bitte mit dem Kommando who, ob Sie Ihren ausgewählten Rechner wirklich für sich haben! Da bei Fehlprogrammierungen (und gelegentlich [aber selten] im Regelbetrieb) das ACS den Betrieb einstellt, ist es hilfreich, die Tests mit echter Hardware *vor Ort* in unserem Praktikumsraum zu machen. Sprechen Sie dazu ein Mitglied des FG an, wir schließen Ihnen gerne auf!

#### 2.2 0. Phase: Einführung (17.04.-23.04.2010)

Am Mittwoch, den 21.04.2009 um 13:00 Uhr findet im Raum S2|02 E102 ein erstes gemeinsames Treffen aller Praktikumsteilnehmer statt.

Bei dem ersten Treffen liegt der Schwerpunkt neben den organisatorischen Details (wie Gruppeneinteilung, Kolloquiumsterminen) bei der fachlichen Einführung. Der Praktikumsleitfaden wird besprochen (Sie sollten ihn also bereits vor diesem Treffen gelesen haben) und Fragen werden beantwortet. Sehr wichtig ist auch die Vorführung der im Praktikum verwendeten Entwicklungswerkzeuge. Weiterhin wird der praktische Umgang mit dem adaptiven Rechner ML310 gezeigt, den Sie als Zielplattform für Ihre Experimente nutzen werden.

Vor Lektüre der Aufgabenstellung sollten Sie unbedingt zwei weitere Kapitel gelesen haben: Essenziell ist das Verständnis des vierten Kapitels über adaptive Rechensysteme. Dieses nimmt auch Bezug auf die CAD-Entwurfsumgebung, die in Kapitel drei dieses Leitfadens beschrieben wird, das Sie daher ebenfalls lesen sollten. Falls Sie die Vorlesung *Prozessorarchitekturen für rechenstarke eingebettete Systeme* besucht haben, sollten Sie bereits genug Vorwissen haben, um dieses Praktikum zu bearbeiten.

An dieser Stelle soll kurz auf die Art und Weise der Abgaben eingegangen werden. Zu jeder Phase muss der erstellte Quellcode, evtl. erstellte Simulations-Waveforms und eine Erläuterung Ihres Lösungsweges eingereicht werden.

Die Abgaben erfolgen als E-Mail an wink@esa.informatik.tu-darmstadt.de, beides mit der Betreffzeile Praktikum Gruppe NN Phase M, wobei NN die Gruppennummer und M die Nummer der Phase ist. Abgageschluss ist immer der letzte Tag des Bearbeitungszeitraumes, 23:59. Die einzelnen Teile der Abgabe sind als Anhänge an diese E-Mail angehängt. Waveforms werden dabei als PostScript-Dateien (erstellt mit Print Only To File in VirSim) dargestellt. Die Erläuterungen sollen im pdf-Format abgegeben werden, es wird empfohlen die Dokumente in Latex zu setzen. In allen Dateien geben Sie bitte ebenfalls Ihre Gruppennummer, die Phase, sowie das Datum an. Bitte vergessen Sie nicht, die Kommentare in den Quelltexten an die aktuelle Abgabe anzupassen.

In der Auf die Abgabe folgenden Woche wird in einem Kolloquium vor Ort wird die Funktionsfähigkeit Ihrer Lösungen entsprechend den Anforderungen der Aufgabe durch den Betreuer überprüft. Im Anschluss daran werden Ihnen Fragen zu Ihrer Realisierung gestellt. Hierbei müssen alle Gruppenteilnehmer anwesend sein.

Nicht lauffähige Abgaben werden nicht anerkannt!

#### 2.3 1. Phase: Hardware-Experimente (24.04.-30.04.2010)

In dieser Woche arbeiten Sie das erste Mal selber mit den Entwicklungswerkzeugen und der Hardware. Sie werden die im Skript vorgestellten Beispiele simulieren, synthetisieren und auf dem ML310 erproben. Abgaben werden hier noch keine von Ihnen erwartet. Gehen Sie dabei wie folgt vor:

- 1. Legen Sie mit mkslave ein neues Slave-Mode-Projekt an und erproben Sie die verschiedenen in der Werkzeugeinführung (Kapitel 3) erklärten Arbeitsschritte. Sie sollten also die Funktionsfähigkeit der Anwendung sowohl in Simulation (RTL und Post-Layout) als auch in realer Hardware auf dem ML310 erproben. Letzteres soll nicht nur durch Ausführen von ./main, sondern auch interaktiv mit dem Werkzeug xmd erfolgen.

- 2. Machen Sie analoge Experimente mit einer durch mkmaster angelegten Master-Mode-Anwendung. Verzichten Sie hier aber auf den interaktiven Test mit xmd, sondern nehmen die reale Erprobung nur durch Starten von ./main vor.

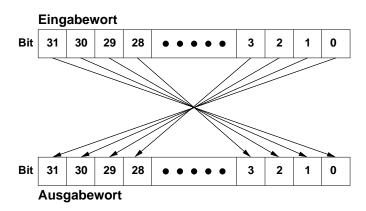

- 3. Erweitern Sie Ihre in 1. angelegte Slave-Mode-Anwendung auf die Spiegelung von 32b Worten wie in Abschnitt 4.3.2 beschrieben. Nehmen Sie die gleichen Simulationen und Tests vor.

- 4. Erweitern Sie auch Ihre in 2. angelegte Master-Mode-Anwendung auf die Spiegelung von 32b Worten (Abschnitt 4.3.3). Erstellen Sie Testdaten mit einem Texteditor im ReadMemFile Format (siehe Abschnitt 3.2), die Sie dann während der Simulation in den simulierten Speicher einlesen. Schreiben Sie die Ausgabedaten mit WriteMemFile in eine Datei.

Berücksichtigen Sie für diese und alle weiteren Phasen folgende Regeln beim Hardware-Entwurf:

- Verwenden Sie nur positiv flankengetriggerte Flip-Flops (@posedge). Sonderwünsche müssen vorher mit dem betreuenden Assistenten durchgesprochen werden.

- Alle Register müssen nach einem Reset auf definierte Werte gesetzt werden (if (RESET) begin ...).

- Ein Register darf nur in exakt einem always-Block Ziel einer Zuweisung sein.

- Interne Tristate-Buffer (also das explizite Setzen eines Signals bzw. Registers auf den Wert Z) sind verboten.

- Verilog register-Arrays dürfen nicht verwendet werden. Wenn Sie partout in Ihrem Entwurf größere Zwischenspeicher brauchen, halten Sie bitte mit dem betreuenden Assistenten Rücksprache.

Nach dieser Phase sollten sie den praktischen Umgang mit den Werkzeugen beherrschen und auch schon erste Erfahrungen mit der Arbeit auf der ML310 Hardware haben.

#### 2.4 2. Phase: Messungen (01.05.-07.05.2010)

Hier werden Sie die Slave-Mode Anwendung reverse, die Sie in der letzten Phase erstellt haben, um Messpunkte erweitern. Ziel ist es zu bestimmen, wie effizient der Datentransfer im Slave-Mode zwischen CPU und RC erfolgt. Dazu werden die maximalen und minimalen Zeiten zwischen zwei CPU-Zugriffen in der Hardware gemessen. Der Software-Teil muß diese Ergebnisse auslesen und dem Benutzer ausgeben. Gehen Sie dabei wie folgt vor:

- 1. Sie müssen den Hardware-Teil um zwei durch die Software lesbare Register erweitern. In einem steht die minimale, in dem anderen die maximale Zeit (in Takten) zwischen zwei Zugriffen.

- 2. Die Zeit zwischen zwei Zugriffen von der Software auf die RC muß durch einen Hardware-Zähler in Takten gemessen werden.

- 3. Nach einem Zugriff müssen die minimalen und maximalen Werte mit dem gerade gestoppten Wert des Zählers aktualisiert werden.

- 4. An Zugriffen sollen sie in drei Schleifen in der Software folgende Muster realisieren: Nur aufeinanderfolgende Lese-Operationen, nur aufeinanderfolgende Schreib-Operationen, abwechselnd je eine Lese- und eine Schreib-Operation.

- 5. Nehmen Sie die Messungen getrennt für jedes Zugriffsmuster vor.

- 6. Simulieren Sie Ihren Entwurf auf RT-Ebene.

- 7. Passen Sie den Software-Teil so an, daß die gemessenen Werte von der RC zurückgelesen und dem Benutzer ausgegeben werden (C-Funktion printf, getrennt für jedes Zugriffsmuster).

6 2 Praktikumsablauf

8. Compilieren Sie die gesamte Anwendung und erproben Sie ./main.

Beachten Sie bei der Realisierung der Messungen folgende Details:

- Ihre Schaltung kann von der CPU mit sogenannten Burst-Transfers angesprochen werden. Dabei bleibt das ADDRESSED-Signal über mehrere aufeinanderfolgende Takte gesetzt. Jeder Takt wird dabei als getrennter Zugriff bearbeitet. Gegebenenfalls wechselt dabei auch der Wert auf dem ADDRESS-Bus, wenn die CPU verschiedene Adressen während des Bursts bearbeitet (schreibt oder liest). Für Ihre Zeitmessungen soll ein Burst-Transfer gleich welcher Länge aber nur als ein Zugriff gewertet werden.

- Schreibzugriffe von der CPU auf Ihre Hardware können ebenfalls mehrere Takte dauern. Dabei bleibt das WRITE-Signal über mehrere aufeinanderfolgende Takte gesetzt. Wie bei Burst-Transfers soll Ihre Zeitmessung auch einen Multi-Takt-Schreibvorgang nur als *einen* Zugriff ansehen.

- Sie sollen also bei deaktiviertem RESET-Signal die Zeit zwischen zwei aufeinanderfolgenden steigenden Flanken des ADDRESSED-Signals messen.

Abgaben: Eine Erläuterung Ihrer Meßmethodik, das erweiterte HDL-Modell und C-Programm sowie die Meßergebnisse.

#### 2.5 3. Phase: Bildbearbeitung (08.05.-14.05.2010)

Als Kernaufgabe in diesem Praktikum werden wir uns mit einem einfachen Problem aus der Bildbearbeitung befassen. Es geht darum, den Kontrast in Graustufenbildern zu erhöhen. Solche Graustufenbilder werden auf dem Rechner als ein zweidimensionales Feld von Zahlen dargestellt, bei dem jede Zahl die Helligkeit des entsprechenden Bildpunktes angibt. In unserem Beispiel sind diese Werte 8b breit, der Wert 0 entspricht dabei vollständiger Schwärze, der Wert 255 dem hellsten Weiß. Aus Vereinfachungsgründen gehen wir davon aus, daß alle Bilder 256 Bildpunkte breit und 256 Bildpunkte hoch sind, also insgesamt 65536 Bildpunkte enthalten.

Ein einfaches Beispielprogramm, das Ihnen den Umgang mit solchen Bildern näherbringen soll, finden Sie in der Datei /opt/cad/Prakt/ACS07/TestData/brighten.c (im Kapitel 5 als Listing 5.5). Diese Anwendung hellt ein gegebenes Bild auf, indem auf alle Grauwerte der Wert 100 aufaddiert wird. Zur Erprobung kopieren Sie die Datei in eines ihrer Arbeitsverzeichnisse und übersetzen Sie es mit dem Kommando make brighten (lauffähig auf dem ML310 ACS). Ein Beispielbild liegt mit dem Namen lena256.pgm im selben Verzeichnis. Durch das Kommando xv lena256.pgm können Sie es sich anzeigen lassen. Mit der Anweisung ./brighten lena256.pgm lena256b.pgm wird in der Datei lena256b.pgm eine hellere Version des Bildes erzeugt. Betrachten Sie auch dieses mit xv und beurteilen Sie das Ergebnis der Aufhellung.

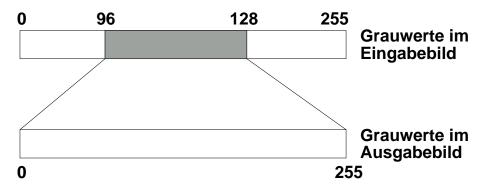

Abbildung 2.1: Idee der Kontrastspreizung

Aber zurück zu unserer Aufgabe: Es gibt eine Vielzahl von Algorithmen, die verwaschene Bilder aufbereiten können. Wir schauen uns hier den einfachsten an: Die Aufspreizung des Kontrasts, der folgende Idee zu Grunde liegt.

- Der dunkelste Punkt des Eingabebilds wird immer auf den Grauwert 0 (=schwarz) im Ausgabebild abgebildet (unabhängig von seinem Ursprungswert).

- Der hellste Punkt des Eingabebilds wird immer auf den Grauwert 255 (=weiß) im Ausgabebild abgebildet (auch hier unabhängig von seinem Ursprungswert).

- Alle anderen Grauwerte des Eingabebilds zwischen diesen Minima und Maxima werden in aufsteigender Reihenfolge gleichmäßig zwischen den Werten 0 und 255 in das Ausgabebild abgebildet.

Als Ergebnis erhält man also aus einem Eingabebild, das den vollen Wertebereich 0 ... 255 nicht vollständig ausnutzt, ein Ausgabebild, das den ganzen Wertebereich verwendet und so einen verbesserten Kontrast hat.

Im Beispiel aus Abbildung 2.1 wird also der minimale Grauwert 96 des Eingangsbildes auf den dunkelsten Wert 0 des Ausgangsbildes abgebildet. Der hellste Grauwert 128 des Eingangsbildes wird im Ausgangsbild zu 255 (weiß). Die 128-96=32 unterschiedlichen Grauwerte des Eingangsbildes werden nun so aufgespreizt, daß Sie das volle Intervall von 0 bis 255 gleichmäßig ausfüllen. Dies wird dadurch erreicht, daß jeder einzelne Grauschritt im Eingangsbild auf  $255/32\approx 8$  Grauschritte im Ausgangsbild abgebildet wird. Also  $96\to 0$ ,  $97\to 8$ , etc. Auf diese Weise bekommen wir zwar nicht mehr unterschiedliche Graustufen ins Ausgangsbild, aber sie liegen weiter auseinander und sind somit besser voneinander zu unterscheiden (höherer Kontrast).

In dieser Phase des Praktikums sollen Sie eine Kopie von brighten.c nach contrast.c so umbauen, daß die oben beschriebene Kontrastspreizung realisiert wird. Sie können dabei die Ein-/Ausgabeoperationen unverändert übernehmen. Nur die eigentliche Berechnung müssen Sie anpassen. Verwenden Sie xv, um die Ergebnisse Ihrer Transformation auch graphisch betrachten zu können.

Beginnen Sie hier schon die Überlegung, welche Teile Ihres Programmes wie in Hardware ausgelagert werden sollen. Wichtige Punkte sind hier beispielsweise

- Die Bitbreiten der verarbeiteten Daten.

- Die Hardware-Implementierung verschiedener Operatoren. So kann eine Multiplikation mit einer Zweierpotenz in Hardware einfach durch eine Links-Schiebeoperation realisiert werden.

- · Ist Parallelverarbeitung möglich?

**Abgaben:** Das von Ihnen entwickelte C-Programm contrast.c sowie eine Beschreibung Ihrer Ergänzungen. Eine Diskussion der von Ihnen geplanten Hardware-Architektur.

8 2 Praktikumsablauf

#### 2.6 4. Phase: IP-Blöcke (15.05.-28.05.2010)

Für die Hardware-Realisierung Ihres Algorithmus werden Sie einen Dividierer mit variablen Operanden benötigen. Dieser wird nicht automatisch bei der HDL-Synthese erzeugt, sondern muss als sog. IP-Block eingebunden werden. Mit Hilfe des CoreGenerator-Tools von XILINX kann ein solches Modul erzeugt werden. Es kann über das Kommando coregen gestartet werden. Zuerst muss ein neues Projekt angelegt werden. Als Family ist *Virtex2P* auszuwählen, Device ist *xc2vp30*, Package *fg896*, und SpeedGrade 6. Dann kann über den Pipelined Divider der gewünschte Dividierer erzeugt werden. Als Ausgabe erhalten Sie (unter anderem) eine Netzliste (.ngc), die zur Implementierung benötigt wird sowie ein Simulationsmodell (.v).

Sie sollen den Dividierer so in einen Verilog-Testrahmen einbinden, daß zwei variable Operandenregister dividiert werden und Quotient und Rest in Ergebnisregistern abgelegt werden.

Der Dividierer hat unabhängig von den Breiten oder den Datentypen (vorzeichenbehaftet oder -los) seiner Operanden folgende Schnittstelle:

dividend : N-Bit Eingang für den Dividenden.

divisor: M-Bit Eingang für den Divisor.

quot : N-Bit Ausgang für den Quotienten.

remd: M-Bit Ausgang für den Rest der Division.

clk: Takteingang.

ce : Bei einer '1' an diesem Eingang wird der Takt aktiviert, der Dividierer arbeitet.

rfd: Unbenutzt.

Die Schaltung ist derart gepipelined, daß pro Takt ein neuer Satz Operanden an den Eingängen akzeptiert wird. Nach einer bestimmten Anzahl von Takten (Latenzzeit), die von den von Ihnen gewählten Parametern (N und M) abhängt, taucht das entsprechende Ergebnis dann an den beiden Ausgängen auf. Der Dividierer arbeitet immer: Einmal pro Takt werden die an den Eingängen anliegenden Werte eingelesen, und nach der Latenzzeit wechseln die beiden Ausgänge auf die Ergebnisse der Berechnung. Es ist also wichtig, die Ausgänge zum *richtigen* Zeitpunkt auszuwerten.

Gehen Sie zur Bearbeitung dieser Phase wie folgt vor:

- 1. Legen Sie ein neues Slave-Mode-Projekt für diese Phase an.

- 2. Erzeugen Sie sich den gewünschten Dividierer mittels des Werkzeugs CoreGen. Dabei werden Sie zwei Dateien erhalten: Kopieren Sie die .ngc Datei in das Unterverzeichnis Simple des Projektverzeichnisses. Kopieren Sie die .v Datei direkt in das Projektverzeichnis. Letztere enthält die Moduldeklaration der Dividiererzelle, hier können Sie die Schnittstelle im Detail sehen.

- 3. Öffnen Sie user.tcl mit einem Texteditor und entkommentieren Sie die Platzhalter add\_file Zeile für Ihren Dividierer (führendes # löschen). Ändern Sie den Namen der Verilog-Datei auf den von Ihnen tatsächlich verwendeten Dateinamen und speichern Sie user.tcl ab.

- 4. Instanzieren Sie Ihre Dividiererzelle in user.v.

- 5. Erweitern Sie user.v um die Realisierung der beiden schreibbaren Register für Dividend und Divisor und die beiden lesbaren Register für Quotient und Rest. Dabei müssen Sie die Adressdekodierung ergänzen. Hinweis: Der Dividierer-Ausgang muss an ein eigenes Register angeschlossen werden, er darf nicht über den Multiplexer direkt an DATAOUT angeschlossen werden.

- 6. Fügen Sie nun die Steuerung hinzu. Diese muß kontrollieren, *wann* genau die Ergebnisregister ihre Werte von den Dividiererausgängen übernehmen. Hier müssen Sie die Latenz beachten: Latchen Sie die Ausgangswerte zu früh, ist die Berechnung noch nicht abgeschlossen. Sind sie zu spät, überschreiben die durch die Pipeline nachrückenden Werte das gewünschte Ergebnis.

- 7. Die Software-Schnittstelle muss so ausgelegt sein, daß pro Operand je ein Schreibzugriff zur Übertragung der Daten von der CPU an die RC benutzt wird. Je ein einzelner Lesezugriff holt dann die Ergebnisse (Quotient und Rest) von der RC wieder ab. Wahrscheinlich müssen Sie bei dieser Betriebsart zwischen dem Schreiben und Lesen in Software etwas Zeit vergehen lassen (die Rechenzeit des Dividierers). Hierzu reicht beispielsweise ein einfaches printf("Waiting ...\n"); aus.

- 8. Simulieren Sie Ihr Verilog Modell auf RT-Ebene. Testen Sie dabei unbedingt auch, ob das Pipelining funktioniert.

- 9. Schreiben Sie einen kleinen Software-Testrahmen in main.c, in dem zwei Zahlen im Slave-Mode zur Division an die RC übertragen werden. Quotient und Rest sollen dann aus der Hardware ausgelesen und dem Benutzer angezeigt werden.

- 10. Implementieren Sie die ganze Anwendung mit make linux. Testen Sie Ihr Programm durch Ausführen von ./main.

**Abgaben:** Das HDL-Modell und C-Programm mit Beschreibung und Simulationsergebnissen (RTL und Post-Layout) als kommentierte Waveforms.

#### 2.7 5. Phase: Slave-Mode Version (29.05.-11.06.2010)

Nun realisieren Sie Ihre in Phase 3 geplante Hardware-Architektur unter Verwendung des in der vorigen Phase erprobten Dividierer IP-Blocks. Dabei soll die Hardware in dieser Phase im Slave-Mode arbeiten: Die CPU überträgt die zu verarbeitenden Daten an die RC, diese führt die Berechnung aus und die CPU holt das Ergebnis ab. Sie müssen dazu das C-Programm auch entsprechend anpassen. Simulieren und erproben Sie Ihren Entwurf auf dem ML310. Führen Sie auch wie in Phase 2 Zeitmessungen an Ihrem Design durch (Effizienz der Kommunikation und Ausführungszeit). Achten Sie schon hier auf eine möglichst gute Parallelisierung der Anwendung!

**Tipp**: Falls Sie mehrere Schleifen in eine Slave-Mode RC auslagern wollen, packen Sie alle Funktionen in *einen* Hardware-Block und wählen Sie mittels eines von der Software beschreibbaren Registers aus, welche Operation aktuell ausgeführt wird.

**Hinweis**: Wir empfehlen Ihnen *dringend*, sich an die hier vorgeschlagene Lösung mittels des Dividierers zu halten. Abweichungen dürfen nur nach Rücksprache und Genehmigung durch den betreuenden Assistenten erfolgen. Analoges gilt für Phase 6!

**Abgaben:** Das HDL-Modell und C-Programm mit Beschreibung, kommentierte Simulationsergebnisse als Tabelle (\$monitor()), Ergebnisse der Zeitmessungen.

10 2 Praktikumsablauf

#### 2.8 6. Phase: Master-Mode Version (12.06.-09.07.2010)

Stellen Sie nun Ihre Lösung (Hard- und Software) wie im Skript gezeigt auf den Master-Mode Betrieb um. Die RC soll nun also lediglich Startparameter von der CPU entgegennehmen und ansonsten die gesamte Verarbeitung selbständig durchführen. Erst am Ende wird der CPU der erfolgreiche Abschluß durch einen Interrupt signalisiert. Die CPU soll dann das Ergebnisbild in die entsprechende Ausgabedatei schreiben. Wie üblich nehmen Sie auch hier die Effizienz- und Zeitmessungen vor.

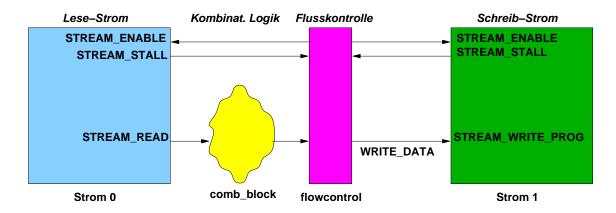

Entscheidend für den Aufbau dieser Schaltung ist die Einbindung Ihrer Berechnung in den Datenstrom, insbesondere in die Flußkontrolle (siehe Abbildung 4.12). Nachdem Sie ein neues Master-Mode-Projekt mit mkmaster angelegt haben, finden Sie in user.v an der Instanz FC des flowcontrol Moduls eine mit dem Kommentar /\*\* Ändern \*/ markierte Stelle. Hier ist der Ausgangs-Port des Lese-Stroms als Eingangs-Port für den Schreib-Strom angeschlossen. Um Ihre Berechnung einzubinden, müssen Sie diese Verbindung auftrennen. Ihre Schaltung muß dann Eingangsdaten aus STREAM\_READ akzeptieren. Der Ausgang Ihrer Schaltung muß dann an die ehemals von STREAM\_READ belegte Stelle des flowcontrol Moduls angeschlossen werden.

Auch die bisher in user. v mit FC verbundenen Flußkontrollsignale müssen in analoger Form aufgetrennt und Ihre eigene Schaltung eingefügt werden. Das zu verwendende Protokoll sieht wie folgt aus. Zum besseren Verständnis sei hier an die Signalverläufe einer Master-Mode-Anwendung erinnert, die Sie ja in Phase 1 studiert haben.

STREAM\_ENABLE: Dieser Eingang dient zur Steuerung des Datenstromes. Beim Lesestrom bedeutet eine '1' auf diesem Port, daß Ihre Schaltung mit der *übernächsten* positiven Taktflanke ein Eingangsdatum von STREAM\_READ in ein Register übernehmen möchte. Beim Ausgangsstrom bedeutet die '1', daß Ihre Schaltung gültige Daten schreiben möchte, die mit der nächsten positiven Taktflanke in den Ausgangsstrom übernommen werden. Eine '0' zeigt entsprechend an, daß zur übernächsten bzw. nächsten positiven Taktflanke keine neuen Daten gelesen bzw. geschrieben werden sollen.

STREAM\_STALL: Eine '1' auf diesem Ausgang zeigt an, daß die Benutzerschaltung zwar Daten lesen bzw. schreiben möchte (STREAM\_ENABLE=1), aber der Strom leider unterbrochen ist. Beim Lesestrom bedeutet dies, daß Daten nur zu solchen positiven Taktflanken von Ihrer Schaltung übernommen werden dürfen, wenn zur vorherigen positiven Taktflanke STREAM\_STALL=0 war. Im anderen Fall muß Ihre Schaltung warten. Beim Schreibstrom wird nur bei einer positiven Taktflanke das Datum tatsächlich übernommen, wenn zur selben Taktflanke STREAM\_STALL=0 ist. Wenn das Signal '1' ist, muß Ihre Schaltung das Ausgangsdatum solange stabil an den Schreibstrom anlegen, bis die Übernahme tatsächlich erfolgt ist. Anderenfalls geht das Datum einfach verloren.

Da Ihre Schaltung wegen des verwendeten Dividierers nun nicht mehr rein kombinatorisch ist, müssen Sie auch die STREAM\_ENABLE und STREAM\_STALL Signale sequentiell verarbeiten. Hier einige (aber nicht alle!) Anhaltspunkte

- Sie dürfen den Schreibstrom erst starten, wenn tatsächlich Ergebnisse aus Ihrem Dividierer vorliegen.

- Sie dürfen den Schreibstrom erst anhalten, wenn tatsächlich alle Eingangsdaten in den Dividierer als Ergebnisse am Dividiererausgang vorliegen (Pipelining!) und erfolgreich geschrieben wurden.

- Sie müssen den Dividierer und den Lesestrom anhalten, wenn der Schreibstrom abreisst (STREAM\_STALL=1).

- Sie müssen den Dividierer und den Schreibstrom anhalten, wenn der Lesestrom abreisst (STREAM\_STALL=1).

Die Systemsimulation provoziert solche Stromunterbrechungen künstlich. Sie können also das Verhalten Ihrer Anwendung schon zur Simulationszeit untersuchen.

**Abgaben:** Das HDL-Modell und C-Programm mit Beschreibung, kommentierte Simulationsergebnisse als Waveforms und/oder Tabelle (\$monitor()), Ergebnisse der Messungen.

An diese Endabgabe werden in der Form weitergehende Anforderungen gestellt. Hier sind keine Ansammlungen von Einzeldateien mehr erwünscht, sondern es wird ein *homogenes* Dokument gefordert, das alle Angaben enthält. So sollen hier beispielsweise auch die Waveforms als EPS-Dateien direkt in den Textfluß eingebunden sein (Ankreuzen von Encapsulated PostScript (EPSF) beim Drucken in VirSim) Auch reichen hier stichpunktartige Erklärungen nicht mehr aus, die endgültige Lösung soll umfassend (auch anhand von Zeichungen) beschrieben werden. Dazu gehört auch eine Kommentierung der Waveforms:

- Was soll gezeigt werden?

- Wie wird sich das in den Signalverläufen niederschlagen?

- Wo (Zeitpunkt) findet man diese Verläufe tatsächlich in den Diagrammen?

Bei dieser Abgabe ist mit einem Gesamtumfang von ca. 15-20 Seiten zu rechnen. Das Abgabeformat dafür ist PDF.

In ihrem Arbeitsverzeichnis sollten Sie ein Unterverzeichnis angelegt haben, in dem alle für den Entwurf benötigten Quellen, Testdaten, ggf. Skripte o.ä. abgelegt werden. Bitte stellen Sie durch ein make clean sicher, daß hier keine unnötigen Dateien mehr existieren und beschreiben Sie in einer kleinen README Datei den Inhalt dieses Verzeichnisses. Seinen Namen teilen Sie bitte in der Abgabe-Mail mit, er wird für unsere abschliessende Datensicherung gebraucht.

#### 2.9 7. Phase: Nacharbeiten (10.07.-16.07.2010)

Die Pflichtaufgaben sollten vor dieser Phase erfolgreich abgearbeitet worden sein. Nach Rücksprache mit dem Betreuer kann aber auch eine Nacharbeit vereinbart werden.

12 2 Praktikumsablauf

## 3 Werkzeugfluß

Um sich mit der ACS-Umgebung vertraut zu machen, sollten Sie zunächst mit sehr einfachen Anwendungen experimentieren. Dazu stehen zwei Musterprojekte für den Slave- und Master-Mode zur Verfügung.

#### 3.1 Anlegen von neuen Projekten

Zum schnellen Start in die Arbeit können Sie auf bereits lauffähige Musteranwendungen zurückgreifen. Durch ein einzelnes Kommando wird ein Unterverzeichnis angelegt und mit allen nötigen Dateien versehen. Sie müssen dann lediglich Ihre Änderungen an den passenden Stellen einbauen.

Das zu verwendende Kommando unterscheidet sich nach dem Typ der zu erstellenden Anwendung: Für die Slave-Mode Betriebsart verwenden Sie das Kommando mkslave, für Master-Mode das Kommando mkmaster. In beiden Fällen folgt dem Kommando der von Ihnen gewünschte Name für das anzulegende Projekt.

Beispiel: Mit dem Kommando mkslave simsel wird im aktuellen Verzeichnis ein Unterverzeichnis namens simsel angelegt. In diesem befinden sich alle für eine Slave-Mode-Anwendung nötigen Dateien. Die Beispielanwendung realisiert ein einzelnes 32b-Register auf der RCU, das durch die CPU geschrieben und wieder ausgelesen werden kann. Nach einem Reset des Systems hat das Register den schon bekannten, leicht wiedererkennbaren Wert 0xDEADBEEF. Andere Teile des RCU-Speicherbereiches, die nicht dieses Register enthalten, liefern beim Lesen den Wert 0xC0FFEE11. Sie kann durch entsprechende Ergänzung leicht an die tatsächlichen Erfordernisse Ihres Entwurfs angepasst werden. Dazu bearbeiten Sie lediglich drei im folgenden Abschnitt beschriebene Dateien. Die Master-Mode Beispielanwendung kopiert einen Speicherbereich durch die RCU auf einen anderen, die CPU ist also beim eigentlichen Kopiervorgang nicht involviert.

#### 3.2 Dateistruktur

Beim Anlegen eines Slave-Mode-Projektes erhalten Sie für Ihre ersten Experimente im wesentlichen drei interessante Dateien:

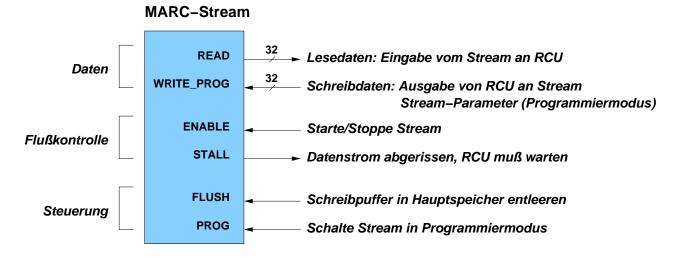

- user.v ist die Beschreibung der Slave-Mode-RCU in Verilog. Hier erkennt man die typische Slave-Mode-Schnittstelle sowie die eigentliche Anwendung im Rumpf des Moduls. Die Beispielanwendung erlaubt den Zugriff auf bis zu vier unterschiedliche Register (Dekodierung der letzten beiden Bits der Wortadresse ADDRESS, also die Möglichkeiten 00, 01, 10 und 11). Davon ist momentan nur die Teiladresse 00 belegt (hier wird das Register outreg an die CPU ausgegeben). In den drei anderen Fällen wird die gut erkennbare Konstante 0xC0FFEE11 ausgegeben. Das Register outreg wird im always-Block auf 0xDEADBEEF zurückgesetzt. Bei Schreibzugriffen auf die Register-Adresse 00 übernimmt es den von der CPU an den Eingabe-Bus DATAIN angelegten Wert. Die Master-Mode-Version enthält zusätzlich noch die Schnittstelle für die MARC-Streams (siehe Abschnitt 4.3.3).

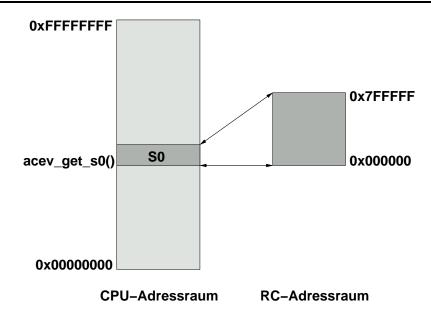

- main.c ist der Software-Teil der Anwendung, der auf der PowerPC-CPU des ML310 ACS ausgeführt wird. Nach den üblichen Vorbereitungen (Initialisierung, bestimmen der Basisadresse des RCU-Bereiches) wird der 32b-Wert an der RCU-Wortadresse 0 (rcu ist als Zeiger auf unsigned long, also auf 32b Werte deklariert) gelesen und ausgegeben. Dies führt also zu einem Zugriff auf das RCU-Register outreg. Danach wird ein Schreibzugriff auf die gleiche Adresse vorgenommen, gefolgt von einem Auslesen des neuen Wertes.

- stimulus.v Zum Testen der RCU in der Simulation müssen die Zugriffe der CPU auf Adressen im RCU-Speicherbereich nachgeahmt werden. Dazu können in dieser Datei vordefinierte Verilog-Funktionen aufgerufen werden. Solche Funktionen stehen für das Starten und Herunterfahren der Simulationsumgebung ebenso bereit, wie für das Nachahmen von Lese- (via Read32) und Schreibzugriffen (via Write32). Beide Funktionen akzeptieren als ersten Parameter die *CPU*-Adresse für den Zugriff. Zum Test der RCU muß hier als Basisadresse des RCU-Adressbereiches die Konstante SLAVE\_BASE angegeben werden. Dazu relativ kann nun die Adresse *innerhalb* des *RCU*-Adressraums angegeben werden. Die Funktion Write32 erwartet als zweiten Parameter den zu schreibenden 32b-Wert, die Funktion Read32 liest einen 32b-Wert von der RCU in ein als zweiten Parameter übergebenes Register (32b breit, im Beispiel heisst das Register data). Die Systemfunktion \$display arbeitet ähnlich wie printf in C, indem sie einen Wert entsprechend der Formatangabe (hier: %h steht für hexadezimale Darstellung) als Text auf der Simulatorkonsole ausgibt.

Zur Simulation von Master-Mode-Anwendungen können in stimulus.v zwei weitere Kommandos zum Umgang mit dem simulierten Speicher verwendet werden. Mit dem Kommando

```

ReadMemFile("infile.mem")

```

wird der Inhalt der Datei infile.mem zur Simulationszeit in den Speicher geschrieben. Die Eingabedatei (hier infile.mem) hat folgendes Format: Die Kopfzeile enthält die Adresse des ersten Bytes und die Anzahl der folgenden 32b Worte. Nun folgen die vorher angegebene Anzahl von 32b Worten, eines pro Zeile. Dann ist die Datei zu Ende, oder es folgt eine weitere Kopfzeile. Alle Zahlen werden hexadezimal dargestellt. Eine Beispieldatei infile.mem könnte wie folgt aussehen:

Nach ReadMemFile("infile.mem") würde auf Adresse 4096 (dezimal) das Wort 0x12345678 beginnen, auf Adresse 4100 das Wort 0x87654321, auf Adresse 4104 das Wort 0xDEADBEEF. Der zweite Block weist Adresse 8192 das Wort 0x10101010 und Adresse 8196 das Wort 0x01010101 zu. Man beachte hier, daß alle Adressen als Byte-Adressen angegeben sind und ein 32b Wort vier Bytes an Speicherplatz benötigt.

Um einen Speicherauszug des simulierten Speichers in eine Datei zu schreiben kann das Kommando WriteMemFile("outfile.mem", 32'h1000, 3) verwendet werden. Mit den hier gezeigten Parametern werden drei 32b Worte beginnend bei Byte-Adresse 4096 (dezimal) in die Datei outfile.mem geschrieben. An das vorige Beispiel anschließend hätte diese dann den folgenden Inhalt:

Um bestehende Dateien nach und von diesem Format zu wandeln stehen zwei Hilfsprogramme bereit. Bei Eingabe von bin2mem <lena256.pgm >lena256.mem auf Unix Kommandoebene wird die Graustufenbilddatei lena256.pgm als hexadezimaler Speicherauszug in die Datei lena256.mem geschrieben. Wichtig: Die Kopfzeile (Startadresse und Anzahl von 32b Worten) fehlt noch und muß manuell mit einem Texteditor in der Datei lena256.mem nachgetragen werden. Der umgekehrte Schritt ist mit mem2bin <lena256contrast.mem >lena256contrast.pgm möglich. Hier sind keine manuellen Schritte mehr nötig. lena256contrast.pgm enthält genau die Daten aus lena256contrast.mem, die Kopfzeile wurde automatisch entfernt. mem2bin ist auf die Bearbeitung von Eingabedateien beschränkt, die nur einen Speicherbereich enthalten.

#### 3.3 Simulation auf Registertransferebene (RTL)

Nach dem Sichten der Eingabedateien können Sie die Funktion der Slave-Mode-RCU im Verilog-Simulator erproben. Dabei werden die in der Stimulus-Datei beschriebenen Zugriffe auf die RCU ausgeführt und währenddessen verschiedene Signale der RCU aufgezeichnet. Diese Signale können bei Ende der Simulation graphisch in Form von Signalverlaufsdiagrammen (waveforms) dargestellt werden. Gegenüber den ebenfalls möglichen Textausgaben auf der Simulatorkonsole haben die Waveforms der Vorteil, dass hier leichter zeitliche Zusammenhänge zwischen parallelen Signalverläufen erkannt werden können.

Das Unix-Kommando

make rtlsim

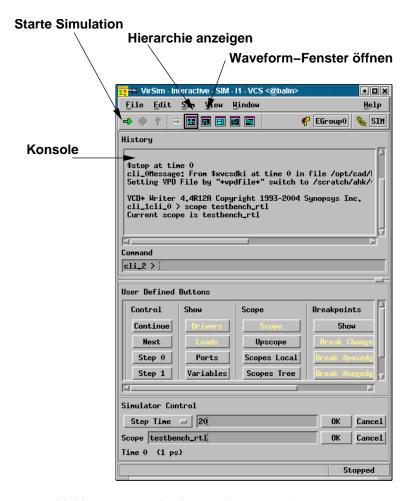

übersetzt die Verilog-Beschreibungen für die Simulation. Sollten hierbei keine Fehler aufgetreten sein (diese würden den Vorgang abbrechen und müssten erst in den Quelldateien behoben werden), wird das Visualisierungswerkzeug für die Signaldiagramme gestartet (siehe Abbildung 3.1).

Man könnte die Simulation schon jetzt starten, würde dann aber nur die Textausgaben durch die \$display-Aufrufe im Verilog auf der Simulatorkonsole sehen. In der Regel ist man aber eher an Waveforms interessiert. Dazu muß dem Simulator *vor* der Simulation mitgeteilt werden, welche Signale tatsächlich aufgezeichnet werden sollen. Der Einfachheit halber werden wir den Simulator anweisen, *alle* Signale unserer im Verilog-Modul user definierten Slave-Mode RCU

14 3 Werkzeugfluß

Abbildung 3.1: Graphische Simulationsumgebung VirSim

Abbildung 3.2: Auswahl der Signale zur Waveform-Anzeige

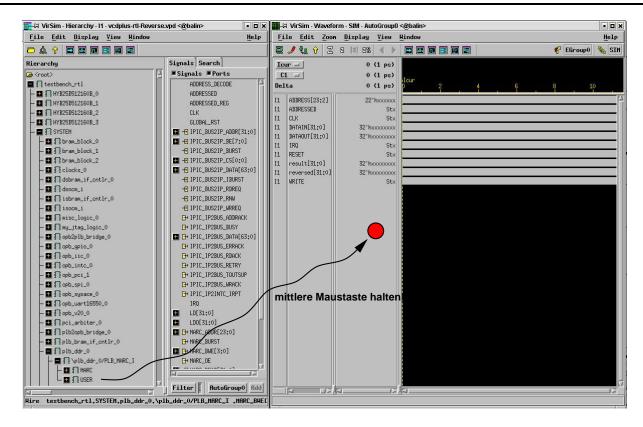

anzuzeigen. Dies schließt sowohl die Schnittstelle zum Restsystem als auch eventuelle interne Register ein. Um diese Auswahl vorzunehmen, lassen wir uns zunächst die komplette Schaltungshierarchie (Klick auf entsprechendes Icon aus Abbildung 3.1) sowie ein leeres Waveform-Fenster öffnen (ebenfalls in entsprechendes Icon klicken). Dieser Zustand ist in Abbildung 3.2 gezeigt.

Im Hierarchy-Abschnitt des Hierarchie-Fensters öffnet man jetzt Hierarchie-Stufen durch Klicken auf das +-Icon, bis das Modul USER im Pfad

```

testbench_rtl.SYSTEM.plb_ddr_0.\plb_ddr_0/PLB_MARC_I.USER

```

sichtbar wird. Mit gehaltener **mittlerer** Maustaste ziehen wir nun das Modul **USER** auf den leeren grauen Bereich im linken Teil des Waveform-Fensters. Der Cursor ändert bei einem akzeptablen Abwurfpunkt die Form und wird grün. Nach dem Loslassen der mittleren Maustaste tauchen nun die Signalnamen im Waveform-Fenster auf. Die Waveforms selber sind grau (Verilog-Wert X = undefiniert).

Nun kann die Simulation durch Klicken des Rechtspfeil-Icons (gezeigt in Abbildung 3.1) gestartet werden. Da auch die vergleichsweise schnelle RTL-Simulation hier ein komplettes System inklusive Speicher-Controller und verschiedener On-Chip-Busse zu bearbeiten hat, dauert es einige Minuten, bis sie durchgelaufen ist. Der Abschluss der Simulation wird durch eine Konsolen-Meldung ähnlich zu

angezeigt. Sie entdecken hier auch die beiden Meldungen, die Ihre \$display-Aufrufe in stimulus.v produziert haben (ggf. im Konsolenbereich einige Zeilen nach oben scrollen). Hier wird zuerst der korrekte Wert beim Lesen des Initialzustands

16 3 Werkzeugfluß

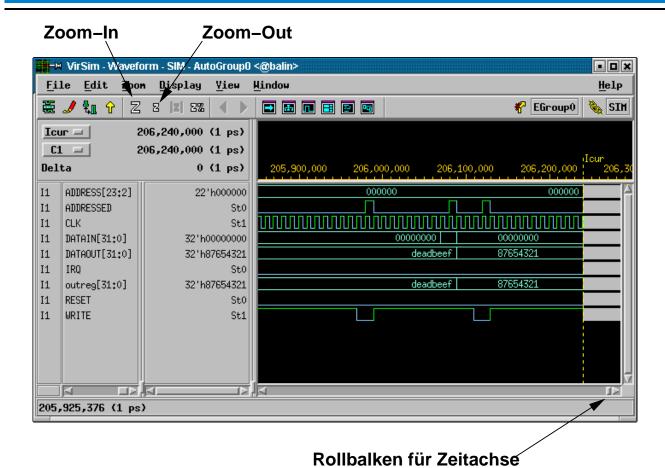

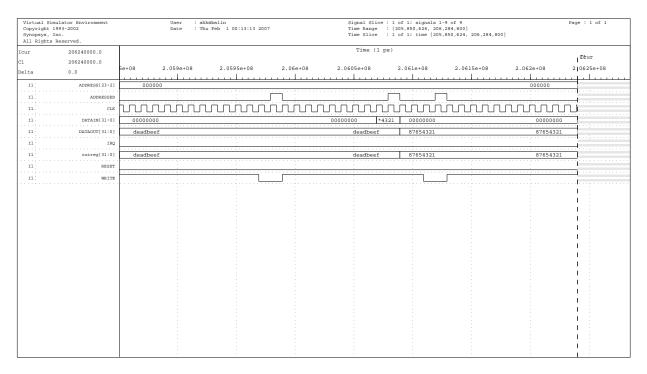

Abbildung 3.3: Waveform-Darstellung der Simulationsergebnisse

(0xDEADBEEF) von outreg ausgegeben. Darauf folgt dann die Ausgabe des neuen Wertes (0x87654321) von outreg nach dem Schreibzugriff.

Scrollen Sie nun horizontal mit dem Rollbalken für die Zeitachse ans rechte Ende des Waveform-Fensters und verkleinern Sie den Maßstab solange durch Klicken auf das kleine Zoom-Out-Icon (kleines z-Symbol) der Menüleiste, bis Sie für das Taktsignal CLK eine ganze Reihen von Taktflanken erkennen können. Machen Sie nun die drei Zugriffe (Lesen, Schreiben, Lesen) ausfindig. Achten Sie jeweils auf die Korrelation zwischen den Signalen CLK, ADDRESSED und WRITE: Wenn bei einer steigenden Flanke von CLK das Signal ADDRESSED auf 1 liegt, liegt ein Zugriff der CPU (hier vertreten durch die Stimulus-Datei) auf die RCU vor. Wenn zu dieser steigenden CLK-Flanke nun WRITE den Werte 1 hat, liegt ein Schreibzugriff vor, sonst ein Lesezugriff. Hinweis: Die Formulierung "zu dieser steigenden Flanke" bedeutet, dass das betreffende Signal unmittelbar vor der steigenden Flanke den entsprechenden Wert hat (Erinnerung TGDI2: Die Zeit vor der steigenden Flanke ist die Setup-Zeit, die nach der Flanke die Hold-Zeit. Die Hold-Zeit kann bei uns mit 0 angenommen werden, relevant ist also nur der Wert eines Signals vor der Flanke).

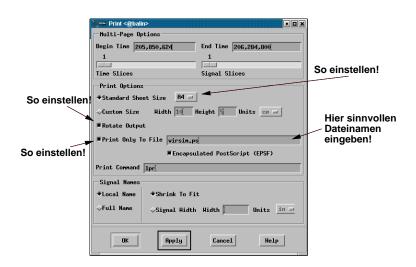

Um eine solche Waveform-Darstellung aus dem Simulator zu exportieren (z.B. für Einbindung in eigene Dokumentation) wählen Sie aus dem Menü File des Waveform-Fensters den Punkt Print... aus und füllen den nun angezeigten Druck-Dialog wie in Abbildung 3.4 aus. Nach dem Klicken von Apply wird die Ausgabe dann in die angegebene Datei geschrieben. Die Grafik in dieser ist allerdings häufig ungeschickt auf der Druckseite angeordnet. Durch das Unix-Kommando

ps2epsi virsim.ps

(geeignet angepasst für den von Ihnen in den Druckdialog eingetragenen Ausgabedateinamen) wird eine neue Datei mit der Endung .epsi, hier also virsim.epsi erzeugt. Diese kann dann leicht, beispielsweise in LATEX, eingebunden werden (Abbildung 3.5).

Beenden können Sie den Simulator durch den Menüpunkt File, Exit.

Falls Sie eigene Experimente mit dem bisherigen Werkzeugfluß machen möchten: Führen Sie beispielsweise die Leseund Schreibzugriffe nicht Wortadresse 0 der RCU (wie in der ursprünglichen Stimulus-Datei), sondern auf Wortadresse 1 aus. Überprüfen Sie das von Ihnen jetzt erwartete Verhalten mit einer geeigneten RTL-Simulation.

Abbildung 3.4: Export von Waveforms in EPS-Datei

Abbildung 3.5: Beispiel für in LATEX eingebundene Waveforms

18 3 Werkzeugfluß

#### 3.4 Erzeugen der RCU-Hardware

Nachdem die Simulation nun den prinzipiellen Nachweis der Funktion der RCU geliefert hat, kann die Verilog-Beschreibung jetzt auf die echte FPGA-Hardware des ML310 ACS abgebildet werden. Dies geschieht durch das Unix-Kommando

#### make bits

Dieser Schritt ist sehr rechenaufwendig und schließt beispielsweise neben einer Kompilierung der Verilog-Quelltexte in digitale Schaltungen (sogenannte Logiksynthese) auch Platzierungs- und Verdrahtungsschritte für mehr als 7300 Logikblöcken und mehr als 47000 Zwei-Terminal-Nets ein. Die Laufzeit dieses Vorgangs liegt je nach Variation der Schaltung bei ca. 35-40 Minuten. An dieser Stelle wird offensichtlich, dass der Test einer in Entwicklung befindlichen Schaltung weitgehend durch Simulation und nicht durch einfaches Ausprobieren auf der ACS-Hardware geschehen sollte!

#### 3.5 Hardware-Test der Slave-Mode-RCU

Bei Slave-Mode-RCUs kann die eigentliche RCU nach erfolgreicher Simulation auch gezielt in echter Hardware erprobt werden, selbst wenn der Software-Teil der Anbindung noch nicht bereitsteht. Dieser Vorgang kann durch das Unix-Kommando

#### make download

gestartet werden. Hier sollten am Ende Meldungen ähnlich zu

```

INFO:iMPACT:579 - '2': Completed downloading bit file to device.

INFO:iMPACT:580 - '2':Checking done pin ....done.

'2': Programmed successfully.

```

ausgegeben werden. Der Bitstrom, der das FPGA mit dem Gesamtsystem einschliesslich Ihrer RCU definiert, ist nun korrekt in den FPGA-Baustein übertragen worden und Sie können jetzt durch interaktive Kommandos Zugriffe auf die Hardware durchführen. Dazu geben Sie ein weiteres Unix-Kommando ein:

xmd

Nun wird als Prompt XMD% angezeigt. Hier geben Sie nun folgendes Kommando ein, um die Kommunikation mit der Hardware aufzubauen:

connect ppc hw

Einige Zwischenmeldungen sollten hier mit den Zeilen

```

Connected to "ppc" target. id = 0

Starting GDB server for "ppc" target (id = 0) at TCP port no 1234

```

enden und der Prompt wieder erscheinen. Lösen Sie jetzt einen systemweiten Reset aus, um die gesamte ACS-Hardware in einen definierten Anfangszustand zu bringen. Hierzu geben Sie das Kommando:

rst

Die Basisadresse der RCU auf dieser XMD-Sicht ist 0x10000000. Diese Adresse ist nun eine *Byte-Adresse*, keine Wort-adresse (wie noch im Verilog) mehr. Das heisst also, dass Sie um z.B. auf das zweite 32b Register der RCU zuzugreifen, die Adresse 0x10000004 ansprechen würden. Dies würde zu einem Wert des ADDRESS-Eingangs der RCU von 0x000001 führen (dort RCU-relative Adresse, Adressbasis 0x10000000 im CPU-Speicherbereich entfällt, Zugriff auf Byte 4 (CPU) entspricht Zugriff auf Wort 1 (RCU), da ein Wort vier Bytes hat).

Zum Auslesen des Registers auf Wortadresse 0 (dort liegt ja outreg) geben Sie jetzt den Befehl:

#### mrd 0x10000000

Hier erfolgt hoffentlich die erwartete Ausgabe (0xDEADBEEF), die angibt, das das Register auf RCU-Adresse 0 in der Tat korrekt initialisiert worden ist.

Jetzt schreiben wir den Wert 0x87654321 in das Register mit dem Kommando:

mwr 0x10000000 0x87654321

Zur Überprüfung lesen wir nun den Wert erneut aus:

#### mrd 0x10000000

Wenn unsere RCU auch in Hardware richtig arbeitet, wird nun der neu geschriebene Wert (0x87654321) auch wieder ausgelesen. Um das Verhalten zu testen, dass von den Wortadressen 1, 2 und 3 immer der in user vorgegebene Wert geliefert wird, machen wir die Probe auf's Exempel und lesen von den entsprechenden Byte-Adressen im CPU-Adressraum:

mrd 0x10000004 mrd 0x10000008 mrd 0x1000000C

In allen drei Fällen wird 0xC0FFEE11 geliefert, unser Marker für ein noch nicht benutztes RCU-Register. Da wir nur auf die letzten beiden Bits der Wortadresse achten, wiederholt sich diese Registeranordnung alle vier Worte. Auf der RCU-Wortadresse 4 findet sich also wieder outreg (die beiden untersten Bits der Wortadresse sind 00, genau hier liegt outreg). Das Kommando

#### mrd 0x10000010

beweist diese These, es wird wieder der derzeit aktuelle Wert von **outreg** (0x87654321) geliefert. Beenden Sie die Sitzung nun durch das Kommando

exit

und kehren wieder zur Unix Kommandozeile zurück.

#### 3.6 Hardware-Test des Gesamtsystems

Nachdem jetzt Ihre RCU selbst bereits korrekt in Hardware läuft, ist es nun an der Zeit, auch das Gesamtsystem zu überprüfen. Durch das Kommando

#### make linux

wird auch der Software-Teil der Anwendung (aus der Datei main.c) für den PowerPC 405 Prozessor auf dem FPGA des ML310 ACS übersetzt, sowie ein bootfähiges Linux zusammengestellt. Dieses wird dann auf die Hardware übertragen und gestartet. Nach dem Durchlauf vieler Zwischenmeldungen (bei denen gelegentliche Pausen von 5-10s normal sind) kommt schliesslich ein vertrauter Anmeldeprompt, bei dem Sie sich mit Ihrem normalen Login-Namen (gruppe01 oder ähnlich) und Password anmelden können. Nach erfolgreicher Anmeldung hier arbeiten Sie nun nicht mehr auf Ihrem Arbeitsplatzrechner, sondern auf dem ML310 ACS!

Dies äußert sich zum einen durch den Inhalt Ihres HOME-Bereichs. Auf dem ACS steht *nicht* mehr Ihr normaler HOME-Bereich aus dem Netz des FG ESA zur Verfügung. Sie befinden sich nun in einem dedizierten Netz, nur bestehend aus Ihrem Arbeitsplatzrechner und dem nebenstehenden ACS. Dabei wird das Verzeichnis

#### /scratch/gruppe01

des Arbeitsplatzrechners (wobei gruppe01 nur ein Beispiel für Ihren Login-Namen ist) als HOME-Bereich für diesen Login-Namen dem ACS zugänglich gemacht. Wenn Sie also eine Datei foo.txt vom Arbeitsplatzrechner auf das ACS übertragen wollen, geben Sie auf dem Arbeitsplatzrechner das Kommando

#### cp foo.txt /scratch/gruppe01

ein. Die Datei foo.txt taucht damit in Ihrem HOME-Bereich auf dem ACS auf. In umgekehrter Richtung, also vom ACS zum Arbeitsplatzrechner lautet das Kommando für eine Datei bar.txt auf dem Arbeitsplatzrechner analog

#### cp /scratch/gruppe01/bar.txt .

Die Datei bar.txt taucht nun im aktuellen Verzeichnis auf dem Arbeitsplatzrechner auf. Da der /scratch-Bereich nicht Bestandteil der Datensicherung ist und auch bei Platzknappheit jederzeit gelöscht werden kann (siehe Leitfaden zum Rechnernetz des FG ESA), sollten Sie alle nicht automatisch wiederherstellbaren Dateien regelmäßig in Ihren HOME-Bereich auf dem Arbeitsplatzrechner kopieren.

Aber schauen wir uns an, was durch das Kommando make linux noch geschehen ist: Auf unserem ACS-HOME-Bereich liegt jetzt auch eine Datei main. Es handelt sich dabei um das auf dem Arbeitsplatzrechner übersetzte Software-Programm unserer ACS-Anwendung, das automatisch bereits in den ACS-HOME-Bereich kopiert wurde. Eventuelle Dateien mit Namen beginnend mit vcdplus-... können Sie ignorieren. Es handelt sich dabei um Zwischendateien einer früheren Simulation auf dem Arbeitsplatzrechner, die dieser aus Platz- und Rechenzeitgründen auch auf Ihrem /scratch-Unterverzeichnis abgelegt hat. Sie sind für die Arbeit auf dem ACS aber bedeutungslos.

20 3 Werkzeugfluß

Nicht bedeutungslos sind allerdings eventuelle Eingabedateien, die Ihre spezielle ACS-Anwendung möglicherweise noch benötigt. Da diese Dateien zwischen unterschiedlichen Applikationen variieren können, kann sie der ACS-Werkzeugfluß nicht automatisch vom Arbeitsplatzrechner auf den ACS-HOME-Bereich kopieren. Falls Ihre Anwendung also Eingabebilder etc. benötigt, kopieren Sie diese durch Absetzen geeigneter Kommandos (siehe oben!) *selber* in den HOME-Bereich auf dem ACS.

Wenn alle benötigten Dateien vorhanden sind (im Fall unserer einfachen Beispielanwendung hier mit dem les- und schreibbaren Register sind keine weiteren erforderlich), kann nun die vollständige ACS-Anwendung, bestehend aus RCU- und CPU-Teil (unserem übersetzten C-Programm) gestartet werden. Dazu wird einfach der Name des übersetzten Programmes, hier also

./main

als Unix-Kommando gegeben. Das nun ablaufende Programm initialisiert die RCU, stellt die Kommunikation her und führt die Lese- und Schreibzugriffe aus. Die printf-Funktionen geben die Registerwerte vor (0xDEADBEEF) und nach dem Schreiben des neuen Wertes (0x87654321) aus.

Tipp: Falls make linux länger als ca. 20s ohne weitere Ausgabe hängen sollte, tippen Sie die Tastenfolge Control-A Control-A. Dann sollten Sie wieder einen Unix-Prompt auf dem Arbeitsplatzrechner bekommen. Geben Sie dann einfach das Kommando make linux erneut ein. Sollte auch nach dem dritten Versuch der Start des ACS-Linux fehlschlagen, halten Sie am blauen ACS-Gehäuse den Reset-Taster (an der Gehäusefront unter dem größeren Einschaltknopf) ca. 2-3s gedrückt, um einen echten Hardware-Reset des ACS auszulösen. Warten Sie dann, bis sich die LEDs auf der ML310 Leiterplatte beruhigt haben, und probieren Sie make linux noch einmal. Wenn nun auch noch drei weitere Versuche fehlschlagen, greifen Sie auf die Rückseite des ACS-Gehäuses und unterbrechen mit dem dort gelegenen Netzschalter die Stromzufuhr für ca. 1 Minute, bevor Sie das ACS wieder einschalten. Warten Sie nun ebenfalls auf stetig leuchtende LEDs (bis sich das System grundinitialisiert hat), und versuchen dann wieder make linux. Wenn alle diese Versuche fehlschlagen, kontaktieren Sie bitte Ihren Betreuer für diese Lehrveranstaltung.

Falls bis hierher alles geklappt hat, haben Sie gerade erfolgreich alle Schritte von der Formulierung getrennter RCU- und CPU-Teile bis hin zur Ausführung der vollständigen Anwendung auf einem modernen ACS absolviert. Nun ist es Zeit für Ihre eigenen Entwicklungen! Dazu modifizieren Sie die main.c, user.v und stimulus.v-Dateien der Materialsammlung entsprechend den aktuellen Anforderungen.

# 4 Adaptive Rechensysteme - Eine praktische Einführung

#### 4.1 Rechnen mit rekonfigurierbarer Hardware

FPGAs können nicht nur als preiswerter ASIC-Ersatz oder für das ASIC-Prototyping verwendet werden. Eine gerade erst im Anfang befindliche Bewegung propagiert die Verwendung von FPGAs und anderen Bauelementen mit ähnlich flexibler Struktur zur Bewältigung von Rechenaufgaben. Auf diese Weise lassen sich gegenüber Standardprozessoren teilweise erhebliche Leistungssteigerungen erzielen.

In diesem Abschnitt werden die Grundlagen des rekonfigurierbaren Rechnens vorgestellt sowie teilweise schon früher behandelte Konzepte (wie FPGAs) in neuem Licht betrachtet.

#### 4.1.1 Anwendungen

Bevor wir uns eingehender mit der Materie beschäftigen, sollen hier als Motivation einige recht erfolgreiche Anwendungen rekonfigurierbarer Hardware zum Lösen verschiedenster Probleme beschrieben werden.

- Ein Algorithmus zum Vergleichen von Gensequenzen lief auf der FPGA-basierten SPLASH Plattform fast 200x schneller als auf Supercomputern (Connection Machine CM-2<sup>1</sup> und Cray-2).

- Der Weltrekord (2001) für die schnellste Entschlüsselung nach dem RSA-Verfahren wird von einem rekonfigurierbaren Rechner vom Typ PAM gehalten (600Kb/s mit 512b langen Schlüsseln).

- Auch im Bereich der DES-Verschlüsselung wird der Rekord 2001 von einer FPGA-Implementierung gehalten (10.7 Gb/s)

- Im Bereich der Signalverarbeitung (Filteralgorithmen etc.) sind rekonfigurierbare Lösungen konventionellen DSPs in der Geschwindigkeit bei einigen Anwendungen um ein bis zwei Größenordnungen überlegen.

- Einige Anwendungen der automatischen Bilderkennung laufen auf einem mit 25 MHz Taktfrequenz betriebenen FPGA mehr als 15x schneller als auf einem mit 450 MHz getakteten Standardprozessor.

Eine Unzahl von weiteren Erfolgen liegen beispielsweise in den Bereichen Arithmetik, Physik, Optimierung, Bild- und Videoverarbeitung, Audio- und Sprachverarbeitung sowie Datennetz-Infrastruktur vor. In allen Fällen werden die betrachteten Probleme deutlich schneller oder ökonomischer auf einer rekonfigurierbaren Plattform gelöst.

Eine weitere, immer wichtiger werdende Größe, ist der Energieverbrauch für eine Berechnung. So stellen moderne mobile Kommunikationssysteme immer höhere Anforderungen an Rechenleistung bei minimalem Stromverbrauch. Nach ersten Untersuchungen können auch in diesem Bereich Architekturen mit einer rekonfigurierbaren Komponente Standardprozessoren (auch in Low-Power-Versionen!) um eine Größenordnung überlegen sein.

#### 4.1.2 Idee

Was unterscheidet nun das Rechnen mit rekonfigurierbarer Hardware vom Rechnen mit Standardprozessoren? Schließlich könnte man doch einfach einen der gängigen Prozessoren auf dem FPGA realisieren. Außer einer deutlich langsameren und sehr viel teureren Implementierung der bekannten Prozessorarchitektur hätte man dadurch aber nichts erreicht.

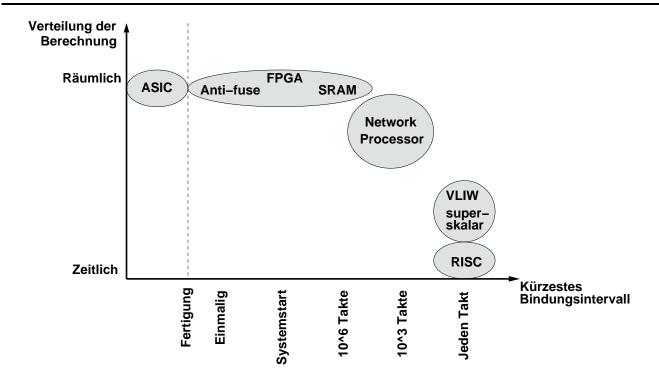

Der wesentliche Unterschied zwischen den beiden Ansätzen besteht darin, dass mit rekonfigurierbarer Hardware eine Berechnung *räumlich* verteilt wird, während sie in Standardprozessoren *zeitlich* verteilt wird. Das folgende Beispiel soll diese recht abstrakte Aussage verdeutlichen.

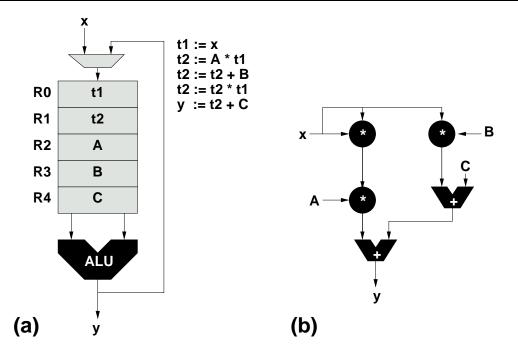

Nehmen wir an, das Polynom  $y = Ax^2 + Bx + C$  soll für verschiedene Werte von x berechnet werden. Bild 4.1.a zeigt die Realisierung auf einem (sehr einfachen) Standardprozessor: Ein Registerfeld R0...R4 speichert Zwischenergebnisse und Konstanten. Für die Arithmetik steht eine ALU mit zwei Eingängen zur Verfügung. Die gesamte Berechnung wird durch

Wie im Film Jurassic Park zu sehen . . .

Abbildung 4.1: Zeitliche und räumliche Verteilung von Berechnungen

das nebenstehende Programm kontrolliert: Pro Zeitschritt wird eine Teiloperation auf der immer gleichen Hardware (nämlich der ALU) ausgeführt. Nach fünf Schritten kann das Endergebnis schließlich ausgegeben werden.

In Bild 4.1.b wird die räumlich verteilte Lösung gezeigt, wie sie auf rekonfigurierbarer Hardware verwendet würde. Zur besseren Darstellung sind in der Abbildung alle aktiv rechnenden Hardware-Teile schwarz unterlegt. Hier wird auf das Registerfeld, die flexible ALU und das sequentielle Steuerprogramm verzichtet. Stattdessen werden direkt fünf Hardware-Operatoren in geeigneter Weise verschaltet. Die gesamte Berechnung wird in einem Zeitschritt ausgeführt, dabei finden aber Teiloperationen auf räumlich verschiedenen Hardware-Schaltungen statt.

Diese letztbeschriebene Vorgehensweise ist für effizienten Hardware-Entwurf allgemein üblich. Aber erst die Verwendung rekonfigurierbarer Logikbausteine erlaubt ihren Einsatz auch zur Realisierung von Universalrechnern. Es wäre ja wenig praktikabel, bei Wunsch nach Ausführung einer anderen Berechnung einen anderen ASIC entwerfen und fertigen zu müssen. In rekonfigurierbare Hardware wird lediglich eine an die neuen Anforderungen angepasste Konfiguration geladen.

In der Realität sind die Grenzen zwischen Standard- und rekonfigurierbaren Prozessoren weniger deutlich. So können moderne superskalare CPUs auch pro Zeitschritt mehrere Operationen auf eigenen Recheneinheiten durchführen. Und auch auf rekonfigurierbaren Architekturen kann es notwendig und sinnvoll sein, eine Teiloperation in mehreren Zeitschritten oder unter Wiederverwendung desselben Hardware-Operators durchzuführen.

#### 4.1.3 Terminologie

Nach diesem ersten Einblick in das rekonfigurierbare Rechnen soll hier die auf diesem Gebiet verwendete Terminologie etwas genauer betrachtet werden.

Rekonfigurierbarkeit (manchmal auch Adaptionsfähigkeit genannt) bezeichnet hier die Fähigkeit, die logische Struktur (Recheneinheiten und ihre Verbindungen untereinander) eines Bausteins bzw. Rechners (als System betrachtet) ohne Chip-Fertigungsprozesse oder Hardware-Umbauten rein durch Programmierung speziell an die Anforderungen von Anwendungen anpassen zu können.

Mit dynamischer oder Laufzeit-Rekonfiguration wird der Vorgang bezeichnet, einen rekonfigurierbaren Rechner auch noch während der Ausführung des Algorithmus zu rekonfigurieren.

Partielle Rekonfiguration liegt vor, wenn nur Teile der rekonfigurierbaren Komponenten eines Bausteins oder Systems rekonfiguriert werden. Diese Funktion wird nicht von allen Bausteinen unterstützt und ist orthogonal zur dynamischen Rekonfiguration.

Feinkörnige Parallelität besagt hier, dass sowohl die Funktion der Recheneinheiten als auch ihre Verbindungsstruktur auf der Ebene einzelner Bits konfigurierbar sind. Auf konventionellen Prozessoren werden zumeist ganze Worte (8b, 16b, 32b) betrachtet.

Spezialisierung nennt man die Fähigkeit, auf rekonfigurierbaren Rechnern auch noch jeden einzelnen Hardware-Operator an die Erfordernisse der Anwendung anpassen zu können. Beispielsweise sind so kompakte und schnelle Multiplizierer implementierbar, die mit genau einem konstanten Wert multiplizieren. Analoges gilt für Addierer und andere arithmetische und logische Operationen.

Im Beispiel aus Abschnitt 4.1.2 können bei der rekonfigurierbaren Realisierung zwei der drei Multiplizierer auf die Konstanten *A* und *B* spezialisiert werden. Auch einer der Addierer kann auf die Addition von *C* spezialisiert werden. Die beiden anderen Komponenten (ein Addierer und ein Multiplizierer) können nicht spezialisiert werden, da sie nur variable Eingänge haben.

#### 4.1.4 Abstufungen von Rekonfigurierbarkeit

Der 'Grad' der Rekonfigurierbarkeit eines Chips oder Systems wird im wesentlichen durch zwei Größen bestimmt.

#### Granularität

Die *Granularität* beschreibt die 'Größe' oder den Funktionsumfang der konfigurierbaren Elemente (Funktionsblöcke und Verbindungsnetze) . Hier einige Beispiele für Funktionsblöcke in der Reihenfolge von feinerer zu gröberer Granularität:

Einzelne Transistorpaare Diese sind mittlerweile nicht mehr üblich, wurden aber früher z.B. auf FPGAs der Fa. Crosspoint verwendet

Look-Up Tables Sehr geläufig, beispielsweise in den FPGAs von Xilinx oder Lucent.

PLD-artige Strukturen Auch weit verbreitet. Anbieter sind z.B. Altera und Vantis.

ALUs Weniger weit verbreitet, benutzt für arithmetische Anwendungen. Einige Anbieter sind Elixent (4b ALUs) und PACT (24b ALUs). Solche Bausteine werden auch gelegentlich als *network processors* bezeichnet, da sie auf den Einsatz in Netzwerk- und Kommunikationssystemen ausgelegt sind.

Komplette Prozessoren Stark im Kommen. Ein Beispiel ist die MIT RAW Architektur (jeder Funktionsblock ist ein MIPS-artiger RISC mit FPU und eigenen Caches). Kommerzielle Beispiele sind Silicon Hive und Pico Chip. Diese Bausteine werden häufig für drahtlose Kommunikation (Funknetze etc.) verwendet.

Die Granularität der Verbindungsnetze hängt damit unmittelbar von der Granularität der Funktionsblöcke ab. So werden auf den grobkörnigeren Architekturen keine Einzelbitsignale mehr verdrahtet, sondern gleich Multibit-Busse (4b, 8b, 32b) geführt.

#### Bindungsintervall

Das *Bindungsintervall* charakterisiert die Mindestzeit (auch abstrakt), die zwischen zwei Änderungen der Hardware-Funktion liegen muß. Wie im folgenden beschrieben *kann* es sich dabei um Rekonfiguration handeln, dies ist aber nicht zwingend erforderlich (man beachte die beiden Extrema).

Einmalig in der Herstellung In dieses Extrem fallen klassische ASICs und MPGAs. Ihre Hardware-Funktion kann hinterher nur noch stark eingeschränkt variiert werden (in der Regel durch Eintragen von Parameter in Chip-Register).

Einmalig nach der Herstellung Hier werden 'leere Chips' erworben, die genau einmal konfiguriert werden können (z.B. Anti-Fuse basierte FPGAs). Ansonsten gelten die gleichen Einschränkungen wie für ASICs und MPGAs.

Beim Systemstart Bei dieser Variante und allen folgenden Fällen handelt es sich um Lösungen, bei der die Hardware-Funktion durch eine in RAM-ablegbare Beschreibung charakterisiert wird. In dieser Variante ist zum Wechsel der Funktion ein kompletter Neustart des Systems erforderlich. In der Regel wird ein Bindungsintervall dieser Länge für das Aufspielen von Software-Updates oder der Änderung der kompletten Systemfunktion (z.B. verschiedene exklusive Betriebsarten wie *entweder* WLAN-Access Point *oder* Router) genutzt.

$10^6$  Prozessortakte Hier sind auch im laufenden Betrieb Anpassungen möglich. Es kann praktikabel werden, für jedes Programm ein oder mehrere angepasste Hardware-Funktionen bereitzustellen.

Abbildung 4.2: Berechnungsverteilung und Bindungsintervalle

$10^3 - 10^2$  Prozessortakte Bei der Kürze dieses Intervalls können auch für einzelne Programmteile (Unterprozeduren, einzelne Schleifen) jeweils angepasste Hardware-Funktionen bereitgestellt werden. Diese Bindungsintervalle markieren den interessantesten Bereich für rekonfigurierbare Rechner.

Jeden Prozessortakt Dieses Extrem wird von klassischen Prozessoren besetzt: Bei einer Instruktion pro Takt ändert sich die von der Hardware ausgeführte Funktion einmal pro Takt. Eine ähnliche Vorgehensweise ist zwar auch bei rekonfigurierbarer Hardware denkbar (Änderung der kompletten Konfiguration jeden Takt), aber impraktikabel: Für jede Neukonfiguration müssen Millionen von Transistoren umgeschaltet werden. Bei der heute in der Regel verwendeten für FPGAs verwendeten CMOS-Technologie fließt zum Zeitpunkt des Umschaltens ein kleiner Strom. Bei Millionen von gleichzeitig schaltenden Transistoren summieren sich diese 'kleinen Ströme' derart auf, dass die Bausteine (ohne exotische Gehäuse und Kühlung) schlicht zu schmelzen beginnen . . .

#### Praktische Auswirkungen

Die Granularität und das Bindungsintervall sind in der Praxis voneinander abhängig. So benötigen grobkörnigere Bausteine deutlich weniger Konfigurationsinformationen als feinkörnigere. Diese veringerte Menge kann dann auch schneller geladen werden (führt also zu kürzeren Bindungsintervallen).

Durch kürzere Bindungsintervalle kann die zur Verfügung stehende Chip-Fläche besser ausgenutzt werden: Man bezahlt schließlich einen hohen Preis (in der Anzahl der nötigen Transistoren), um die Rekonfigurierbarkeit zu erreichen. Dann sollte man sie auch möglichst effizient ausnutzen! Wie oben angedeutet erlauben kürzere Bindungsintervalle die Anpassung der Hardware selbst auf einzelne Programmteile. So können beispielsweise jeweils die Operationen einzelner Schleifen durch individuell angepasste Logik beschleunigt werden.

Letztlich hängt aber die Auswahl eines Bausteines vom Anwendungsgebiet ab: Wenn die gesamte Applikation beispielsweise nur aus einer einzelnen Kernschleife besteht (z.B. einem einfachen Filter), ist ein kurzes Bindungsintervall nicht notwendig. Hier kann die Konfiguration einmal beim Systemstart erfolgen, die Vorteile (kleinerer Standardprozessor beschleunigt durch rekonfigurierbare Komponente) werden aber trotzdem realisiert. Auch ist eine grobe Granularität nicht immer die beste Wahl: Diverse Anwendungen aus dem Krypto- und Netzwerkbereich arbeiten auf einzelnen Bits oder kleinen Bit-Gruppen. Hier würde man also zweckmäßiger feinkörnigere Bausteine einsetzen, die diese direkt (ohne Schiebe- und Maskierungsoperationen) verarbeiten können.

#### 4.1.5 Aufbau adaptiver Rechensysteme

Nachdem wir nun festgestellt haben, dass rekonfigurierbare Rechner eine sinnvolle Alternative zu klassischen Computern darstellen können, gilt es nun zu überlegen, wie ein solches System tatsächlich aufgebaut werden könnte.

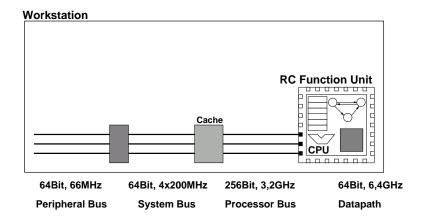

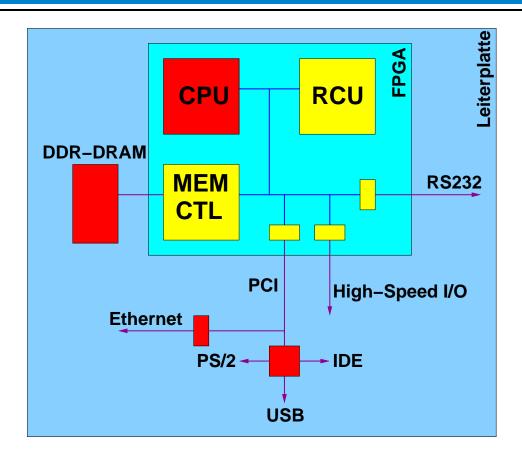

Im allgemeinen bestehen Programme zur Lösung praktischer Probleme nicht ausschließlich aus den wenigen Teilen, die das Gros der Rechenintensität ausmachen. Dazu kommen in der Regel noch administrative Aufgaben wie beispielsweise Ein-/Ausgaben, Speicherverwaltung und Fehlerbehandlung. Die rekonfigurierbare Hardware könnte zwar auch diese Aufgaben übernehmen, dies ist aber nicht besonders effizient: Diese Tätigkeiten sind überwiegend nicht besonders zeitkritisch, müssen aber in ähnlicher Form für viele Anwendungen bereitgstellt werden. Anstatt nun einen größere Menge an rekonfigurierbaren Elementen für ihre allgemeine Implementierung zu ver(sch)wenden, läßt man sie doch lieber gleich auf einem Standardprozessor ablaufen. Dieser muß noch nicht einmal besonders leistungsfähig sein, da für die 'Spitzenlast' an Rechenleistung ja die rekonfigurierbare Recheneinheit (im folgenden *RCU* genannt) verwendet wird. Unser adaptives Rechensystem wird also einen Standardprozessor (ab jetzt mit *CPU* bezeichnet) mit rekonfigurierbarer Hardware kombinieren. Wie die nächsten Abschnitte zeigen werden, kann dies aber auf verschiedene Arten geschehen. Die Bilder 4.3 bis 4.7 stellt einige der möglichen Varianten dar.

#### Freistehende RCU

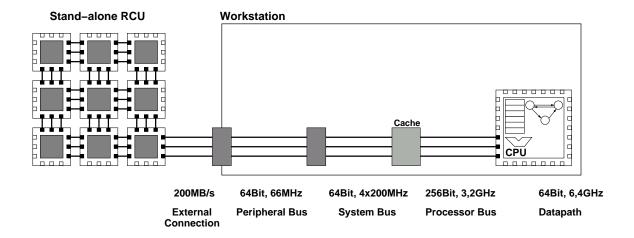

Abbildung 4.3: Freistehende RCU

System mit sehr großem RCU Anteil haben diesen außerhalb des eigentlichen Rechners untergebracht (Bild 4.3). Die Kommunikation erfolgt über eine *externe I/O-Schnittstelle*. Dieser Aufbau wird auch als freistehende RCU ('stand-alone unit') bezeichnet.

Ein typischer Vertreter dieser Gattung wird im wesentlichen für die ASIC-Emulation und als Beschleuniger für HDL-Simulationen genutzt. Eine RCU Kapazität von bis zu 256 Millionen Gatter steht zur Verfügung. Die Anbindung an die CPU erfolgt über das auch bei Festplatten verwendete FibreChannel-Protokoll.

Auf diese Weise lassen sich zwar sehr große rekonfigurierbare Flächen realisieren, aber (neben den anderen praktischen Nachteilen ...) beschränkt die hohe Latenz der Kommunikation zwischen CPU und RCU die Art der realisierbaren Anwendungen, wie das folgende hypothetische Beispiel zeigen soll: Angenommen, die RCU kann pro Takt die Arbeit von 40 Prozessorbefehlen leisten. Falls aber jeder Datentransfer zwischen RCU und CPU 100 Takte braucht, lohnt sich dies nur für Algorithmen, die, relativ zu ihrer Gesamtlaufzeit gesehen, nur wenig mit der CPU kommunizieren müssen. Solche Anwendungen existieren zwar, sie stellen aber nur einen kleinen Teil der Gesamtheit der interessanten Applikationen dar.

#### Angeschlossene RCU

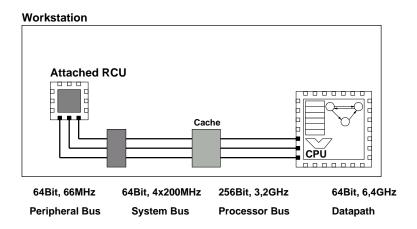

Es ist daher sehr sinnvoll, die Kommunikationslatenz zwischen RCU und CPU so gering wie möglich zu halten. Auf diese Weise könnten auch kleinere (kürzere) Programmteile noch effektiv ausgelagert werden. Die heute gängige Lösung (Bild 4.4) verlagert die RCU direkt in den Rechner und schließt sie dort an den *Peripheriebus* (oft PCI, vereinzelt schon PCI-X oder PCI Express, aber noch sind auch ältere Bussysteme wie SBus oder VME in Gebrauch) an. So sind bei dem derzeit gängigen 32b PCI Bus getaktet mit 33 MHz theoretische Datenübertragungsraten von 132 MB/s erreichbar. Aber auch hier sind die Latenzen noch nennenswert: Ein Schreibzugriff vom PCI Bus auf den Hauptspeicher dauert circa 10 Bustakte

Abbildung 4.4: Angeschlossene RCU

(330ns), ein Lesezugriff gar über 30 Bustakte (>  $1\mu$ s). Der Vorteil dieser Anbindung ist der problemlose Anschluß an die leicht handhabbaren Peripheriebusse von Standardrechnern mittels einer einfachen Steckkarte. Bei dieser Lösung wird von einer angeschlossenen RCU ('attached processing unit') gesprochen.

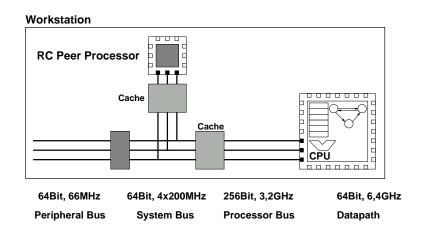

#### RCU in Multiprozessorsystem

Abbildung 4.5: Multiprozessoren: RCU gleichberechtigt mit der CPU

Der Aufbau von adaptiven Rechnern mit noch engerer Kopplung von RCU und CPU wird nun zunehmend schwieriger. Eine Möglichkeit sieht die RCU und die CPU als *gleichberechtigte Partner* auf dem Prozessorbus an (Bild 4.5). Eine solche Anordnungen von gleichberechtigten Prozessoren wird als symmetrischer Multiprozessor (SMP) bezeichnet. Der Geschwindigkeitszuwachs gegenüber Peripheriebussen ergibt sich aus dem sehr viel höheren Bustakt (beispielsweise mit 800 MHz) und den kürzeren Latenzen (im Bereich von 4-40 Takten). Die Protokolle für die Interprozessorkommunikation sind zwar nicht trivial (es müssen unter anderem die unabhängigen Caches von RCU und CPU kohärent gehalten werden), lassen sich aber mit der nötigen Geschwindigkeit auch noch in FPGAs realisieren. Mittlerweile gibt es Trends, Prozessorbusse wie HyperTransport mittels gut handhabbarer Steckverbinder (HTX) zu nutzen, um verschiedenste Recheneinheiten (z.B. Kryptobeschleuniger, aber auch RCUs) leicht auf kommerziell erhältlichen PC-Motherboards einzusetzen.

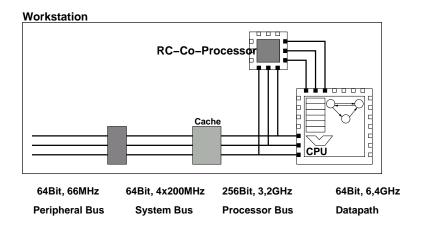

#### **RCU-Koprozessor**

Die Anbindung der RCU zusammen mit der CPU an einen gemeinsamen Cache verkürzt die Latenzen in der Regel noch weiter (Bild 4.6). Bei dieser Kombination agiert die RCU als echter Koprozessor für die CPU. Die Kommunikation zwischen RCU und CPU kann dann in 10 Prozessortakten vorgenommen werden, ein Speicherzugriff über den Cache kann im Erfolgsfall (cache hit) in ähnlicher Zeit bewältigt werden. Solche Architekturen lassen sich zwar noch nicht mit den in PCs üblichen CPUs realisieren (diese sehen schlicht keine RCU auf dem Chip vor). Aber spezielle konfigurierbare Prozessoren wie die Tensilica Xtensa IP-Blöcke werden auch heute schon mit RCUs auf einem Chip kombiniert (z.B. in der Stretch S5000 Architektur). Verschiedene sogenannte System-FPGAs (z.B. Xilinx Virtex II Pro, 4FX und 5FX) enthalten

Abbildung 4.6: RCU als Koprozessor

bereits einen oder mehrere Prozessoren auf dem Chip und erlauben so den Koprozessorbetrieb von RCU und CPUs. Hier dreht sich dann der Spiess um, indem die CPU nun in die RCU eingebettet wird.

#### **RCU-Funktionseinheit in CPU**

Abbildung 4.7: RCU als Funktionseinheit in CPU

Auch eine noch engere Integration ist denkbar: Die RCU könnte als Funktionseinheit (RFU) direkt in den Prozessorkern hineinintegriert werden (Bild 4.7). Ähnlich wie eine ALU mit festen Funktionen würde dann auch eine rekonfigurierbare Funktionseinheit bereitstehen. Im akademischen Bereich sind solche Chips bereits realisiert worden. Bei den ersten Ansätzen zeigte sich aber, dass die Anbindung zwar mit niedriger Latenz (1 Prozessortakt), aber auch mit nur niedriger Übertragungsgeschwindigkeit benutzbar war: Ähnlich wie bei den anderen CPU-Befehlen konnten auch an die RCU nur einzelne Register (in der Regel also 32b Worte) übergeben werden. Auch das Ergebnis der Berechnung wurde in einem einzelnen Zielregister abgelegt. Obwohl also in der RCU deutlich aufwendigere Berechnungen realisierbar waren, wurden diese durch die sehr niedrige Kommunikationsbandbreite 'ausgehungert' (bekamen nicht genug Daten). Neuere Experimente mit RCU-Funktionseinheiten versuchen, dieses Problem durch Bereitstellen RCU-eigener Speicherschnittstellen zu umgehen. Dabei müssen aber die Interaktionen zwischen den Speicherzugriffen des Prozessors und der RCU-Funktionseinheit sorgfältig koordiniert werden. Kommerziell ist allerdings noch kein Vertreter dieser Gattung von adaptivem Rechner verfügbar. In einer anderen Spielart (z.B. den Stretch S5000 Chips) werden die RFUs über spezielle, breitere Register mit Daten versorgt, welche durch geeignete LOAD/STORE-Anweisungen der CPU gehandhabt werden. Zwar können hier in einer Instruktion auch größere Datenmengen als die üblichen 32b ausgetauscht werden (nämlich 128b), die Kommunikationsanweisungen sind aber oft eingeschränkt (erlauben beispielsweise wohl einen Datentransfer aus einem CPU in ein breites RCU-Register, aber nicht in die Gegenichtung). Als weiteres Problem erweist sich in der Praxis, die langsamere Taktfrequenz der rekonfigurierbaren Einheiten mit dem Takt der hochgezüchteten festen ALUs (die teilweise mit über 7 GHz Takt arbeiten) des Prozessors in Einklang zu bringen. RFUs kommen daher in der Regel nur auf ohnehin langsameren Prozessoren für eingebettete Systeme zum Einsatz. Hier fallen die Taktdifferenzen weniger extrem aus (z.B. 300 MHz CPU-Takt zu 100MHz RFU-Takt).

#### Weitere Systemkomponenten

Obwohl wir uns an dieser Stelle nur auf die Hardware-Aspekte konzentriert haben, besteht ein adaptives Rechensystem natürlich auch noch aus Software. Und damit sind hier noch nicht die Werkzeuge gemeint, um ein solches System zu programmieren (siehe dazu Abschnitt 4.2), sondern nur die für den Betrieb erforderlichen.

Auch ein adaptiver Rechner benötigt ein Betriebssystem auf der CPU, das im einfachsten Fall nur den Zugriff auf verschiedene Peripherie bereitstellt und in der Lage ist, Benutzerprogramme zu starten. Häufig werden noch weitere Funktionen wie die Speicherverwaltung und das schnelle Umschalten zwischen mehreren Anwendungen (Multitasking/-threading) vom Betriebssystem übernommen.

Bei adaptiven Rechnern kommt zu diesen Standardaufgaben auch noch die Interaktion zwischen CPU und RCU hinzu. Beispiele für solche Operationen sind:

- Aufbau einer Kommunikationsverbindung zur RCU.

- Laden einer Konfiguration in die RCU.

- Übertragen von Daten in die RCU.

- Starten der Berechnung auf der RCU.

- Überprüfen des Berechnungsstatus der RCU.

- Übertragen von Daten von der RCU.

- Abbau der Kommunikationsverbindung zur RCU.

Bei sehr engen Kopplungen werden viele dieser Aufgaben direkt in Hardware realisiert. So genügt dort in der Regel ein einzelner CPU-Befehl, um Daten in die RCU zu übertragen.

In jedem Fall sollte die Komplexität des Software-Aspekts nicht unterschätzt werden. Selbst wenn die Hardware schon länger fehlerfrei vorliegt, ist es noch häufig ein längerer Weg, bis das ganze *System* erfolgreich arbeitet. Und viele Probleme tauchen erst bei der Systemintegration (dem ersten Zusammenbau und gemeinsamen Test der einzelnen Komponenten) auf.

#### 4.1.6 Auswirkungen auf die Architektur von Prozessoren

Nach den ganzen vorangegangen Erläuterungen mag der Leser argumentieren: "Das ist ja alles gut und schön, aber ich warte einfach 18 Monate, und dann ist auch mein Prozessor von der Stange so schnell ('ganz viele Gigahertz'), dass sich der ganze rekonfigurierbare Aufwand gar nicht lohnt". Leider ist das nicht mehr selbstverständlich: Wahr ist, dass sich derzeit circa alle 18 Monate die Zahl der auf dem Chip realisierbaren Transistoren verdoppelt (Moores Gesetz). Aber eine Verdoppelung der Transistorzahl führt nicht zwangsläufig zu einer Verdoppelung der Rechenleistung.

Daneben darf nicht vergessen werden, dass natürlich auch FPGAs von den Fortschritten der Fertigungsprozesse profitieren. Die sehr reguläre Struktur moderner FPGAs schlägt sich auch in einem sehr regulären Chip-Layout nieder. Es müssen also nur vergleichsweise kleine Blöcke 'von Hand' an die Design-Rules eines neuen Prozesses angepaßt werden. Das gesamte FPGA wird dann im wesentlichen durch Vervielfältigen dieser Tiles (=Kacheln) in Schachbrett-Manier aufgebaut. Durch diese schnelle Anpassbarkeit gehören FPGAs häufig zu den ersten Schaltungen, die auf neuen Prozessen gefertigt werden. Sie treiben also deren Entwicklung voran und agieren so als 'process drivers'.

Beispiel: Wir betrachten hier die Intel Pentium-III Familie. Diese ist zwar nicht mehr ganz taufrisch, aber im Gegensatz zu aktuellen Prozessoren können wir hier die Effekte bei Vervielfachung von Transistoranzahl und Taktfrequenz bei gleichbleibender Basisarchitektur über einen längeren Zeitraum beobachten. Ein Intel Pentium-III Prozessor (9.5 Millionen Transistoren, externer L2 Cache) mit 500 MHz Taktfrequenz erreicht die Werte 20.6 und 14.7 im SPEC Benchmark (für Integer und Floating Point-Operationen). Eine neuere Pentium-III Variante mit 28.5 Millionen Transistoren (jetzt mit dem L2 Cache direkt auf dem Chip) und sagenhaften 1000 MHz Taktfrequenz erreicht nun die Werte 46.8 und 32.2. Das sieht auf den ersten Blick gut aus (Beschleunigung um den Faktor 2.3 bzw. 2.2). Aber: Neben einer Verdoppelung des Taktes war für das Erreichen dieser Werte auch eine Verdreifachung der Transistorzahl erforderlich. Für immer weniger Gewinn an Rechenleistung ist immer mehr Aufwand erforderlich. Man sollte sich also nach Alternativen zu diesen Holzhammermethoden umsehen . . .

Die Möglichkeit, die Struktur eines variablen FPGA-basierten Prozessors speziell auf das aktuelle Problem abzustimmen, eröffnet ganz neue Perspektiven für die Architektur von leistungsfähigen Prozessoren. Aber ist ihr Einsatz auch praktikabel?

| Anwendung                    | Anzahl Gatter |

|------------------------------|---------------|

| JPEG Encoder                 | 75K           |

| MPEG-2 Decoder               | 105K          |

| MPEG-2 Codec                 | 1.5M          |

| UMTS Basisstation Modem      | 4.5M          |

| Einfacher 3D Grafikprozessor | 20M           |

Tabelle 4.1: Gatterkomplexitäten einiger Anwendungen

Heutige Fertigungsprozesse erlauben die Herstellung von Prozessoren bis hin zu 681 Millionen (Nvidia G80 Grafikbeschleuniger) oder 1,7 Milliarden Transistoren (Intel Montecito). Was aber wird bisher mit dieser gewaltigen Chip-Fläche angefangen? Die klassische Prozessor-Architektur zeigt sich hier wenig erfinderisch: Immer größere Caches (z.B. 1.5MB L1 beim HP PA-8700, damit läuft der SPEC Benchmark komplett aus dem Cache, oder 26MB in L1...L3 auf dem Montecito), höhere Integration (z.B. Speicher-Controller on-chip) oder gar mehrere ausgewachsene Prozessoren auf dem gleichen Chip (HP PA-8800 = 2x PA-8700). Immer häufiger wird aber die Frage gestellt, ob diese traditionellen Denkweisen in Anbetracht der immer weiter wachsenden Chip-Flächen noch sinnvoll sind.