## **Bachelorarbeit:**

## Auslagerung von FPGA Laufzeitdaten in nicht-volatilen Speicher

Um *Field-Programmable Gate Arrays* (FPGAs) effizient als eingebettete Systeme mit begrenztem Energie-Budget einzusetzen, müssen diese abgeschaltet werden, solange sie keine Daten verarbeiten. Manche FPGAs unterstützen zwar einen Schlafmodus mit reduzierter Leistungsaufnahme, im Vergleich zu modernen Mikrocontrollern benötigen diese dann aber immer noch etwa die 100-fache Leistung, um die Daten in ihren verteilten SRAMs zu halten. Oftmals ist aber nur ein kleiner Teil dieser Daten (bspw. aggregierte Messwerte) für den weiteren Betrieb des FPGAs nach dem Aufwachen notwendig. Wenn man diese in einen nicht-volatilen Speicher (NVM) außerhalb des FPGAs auslagert, dann kann man das FPGA auch vollständig abschalten. Da das Auslagern (und spätere wieder Einlesen) der Laufzeitdaten zusätzliche Energie benötigt, lohnt sich dieser Swapping-Mechanismus erst ab einer bestimmten Schlafdauer, die unter anderem abhängig von der Menge der relevanten Laufzeitdaten ist. Im Rahmen einer Bachelorarbeit soll dieser Trade-off analysiert werden. Dafür sind folgende konkrete Aufgaben zu realisieren:

- Analyse und Vergleich verschiedener NVM-Typen (bspw. Flash, FRAM, PCM)

- Theoretische Analyse der minimalen notwendigen Schlafzeit für verschiedene FPGAs und NVMs.

- Analyse verschiedener WSN- und IoT-Anwendungen bezüglich auszulagernder Datenmenge und typischer Schlafdauer

- Auswahl des für das Auslagern von Laufzeitvariablen am besten geeigneten NVM-Typs

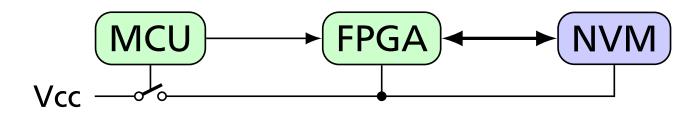

- Prototypische Implementierung eines NVM-Boards, das neben dem Speicher auch durch einen Mikrocontroller (MCU) steuerbare Schalter zum Unterbrechen der Spannungsversorgung von FPGA und NVM sowie Abgriffe zum Messen der Leistungsaufnahme bereit stellt

- HDL-Implementierung (VHDL oder Verilog) zur Ansteuerung des NVM durch das FPGA. Diese sollte möglichst generisch (FPGA- und Anwendungs-unabhängig) und effizient sein. So sollten keine Daten ausgelagert werden, die sich seit dem letzten Aufwachen nicht geändert haben.

- Validierung der minimal notwendigen Schlafzeit für ein Microsemi IGLOO FPGA durch Leistungsmessungen am NVM-Board mit und ohne Auslagerung von Laufzeitdaten

Der Arbeitsfortschritt ist durch regelmäßiges Einpflegen der Quelldateien in ein Versionsverwaltungssystem (Git) nachzuweisen. Die Quelldateien müssen angemessen dokumentiert werden.

Benötigte Kenntnisse: Verilog/VHDL, C

Bei Interesse melden Sie sich bei: Andreas Engel (engel@esa.informatik.tu-darmstadt.de), S2 | 02 E106