# Implementierung und Analyse einer digitalen Signalsynthese auf einer rekonfigurierbaren Recheneinheit

Implementation and Analysis of a Digital Signal Synthesis on a Reconfigurable Computing Unit

Bachelor-Thesis von Konrad Stahlschmidt aus Limburg a.d. Lahn Oktober 2011

Fachbereich 20 (Informatik) FG Eingebettete Systeme und ihre Anwendungen Implementierung und Analyse einer digitalen Signalsynthese auf einer rekonfigurierbaren Recheneinheit

Implementation and Analysis of a Digital Signal Synthesis on a Reconfigurable Computing Unit

Vorgelegte Bachelor-Thesis von Konrad Stahlschmidt aus Limburg a.d. Lahn

1. Gutachten: Prof. Dr. Andreas Koch

2. Gutachten: Dipl.-Inform. Andreas Engel

Tag der Einreichung:

# **Erklärung zur Bachelor-Thesis**

Hiermit versichere ich, die vorliegende Bachelor-Thesis ohne Hilfe Dritter nur mit den angegebenen Quellen und Hilfsmitteln angefertigt zu haben. Alle Stellen, die aus Quellen entnommen wurden, sind als solche kenntlich gemacht. Diese Arbeit hat in gleicher oder ähnlicher Form noch keiner Prüfungsbehörde vorgelegen.

| Darmstadt, den    | 24. Oktober 2011 |

|-------------------|------------------|

|                   |                  |

|                   |                  |

| (K. Stahlschmidt) |                  |

# Inhaltsverzeichnis

| 1.1. Motivation                                             | . 4 <b>5</b> . 5 |

|-------------------------------------------------------------|------------------|

|                                                             | <b>5</b><br>. 5  |

| 2 Verfahren zur Sinuserzeugung                              | . 5              |

| 2. Venamen zur Smuserzeugung                                |                  |

| 2.1. LC-Schwingkreis                                        |                  |

| 2.2. RC-Oszillator                                          | . 6              |

| 2.3. Rechteck als Grundfunktion                             |                  |

| 2.4. Direct Digital Synthesis                               |                  |

| 2.4.1. Prinzip                                              |                  |

| 2.4.2. Bewertung                                            |                  |

| 3. DDS Implementierung                                      | 13               |

| 3.1. Modulhierarchie                                        |                  |

| 3.2. Erzeugung des Phasensignals                            |                  |

| 3.3. Umsetzung zwischen Phase und Amplitude                 |                  |

| 3.3.1. LUT                                                  |                  |

| 3.3.2. CORDIC                                               |                  |

| 3.3.3. Lineare Interpolation                                |                  |

| 3.4. Ansteuerung des Digital-Analog-Wandlers                |                  |

| 3.5. Tiefpassfilter                                         |                  |

| 3.6. Schnittstellen                                         |                  |

| 4. Analyse                                                  | 31               |

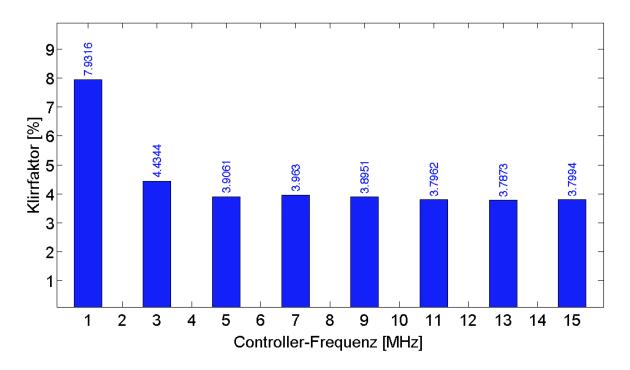

| 4.1. Controller-Frequenz                                    |                  |

| 4.2. Anzahl der erzeugten Ausgabekanäle                     |                  |

| 4.3. RAM Initialisierungsalternativen                       |                  |

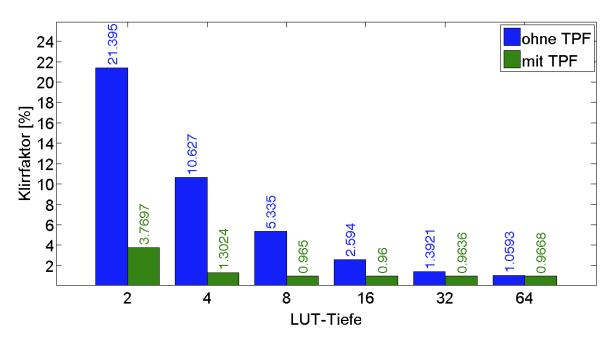

| 4.4. Auswirkung der LUT-Tiefe                               |                  |

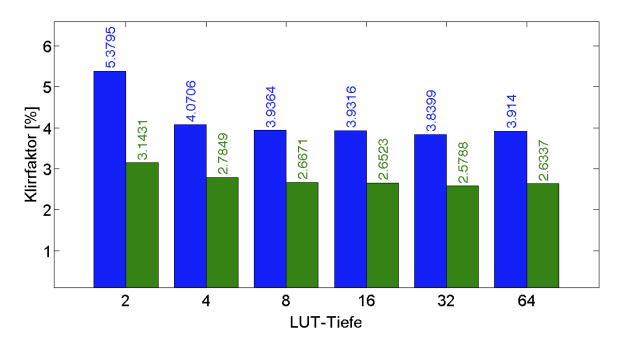

| 4.5. Interpolation zwischen Stützstellen                    |                  |

| 4.6. Auswirkung der LUT-Breite                              |                  |

| 4.7. Auswirkungen der Anzahl der CORDIC-Iterationen         |                  |

| 4.7.1. Genauigkeit der berechneten Amplituden               |                  |

| 4.7.2. Auswirkungen der Iterationsanzahl auf die Signalgüte |                  |

| 4.7.3. Amplitudenberechnung zur Laufzeit                    |                  |

| 4.8. Tiefpassfilter                                         |                  |

| 4.9. Genauigkeit der Ausgangsfrequenz                       |                  |

| 5. Zusammenfassung und Ausblick                             | 47               |

| Literaturverzeichnis                                        | 49               |

| Αk | bildungsverzeichnis                                           | 52 |

|----|---------------------------------------------------------------|----|

| Α. | Anhang                                                        | 53 |

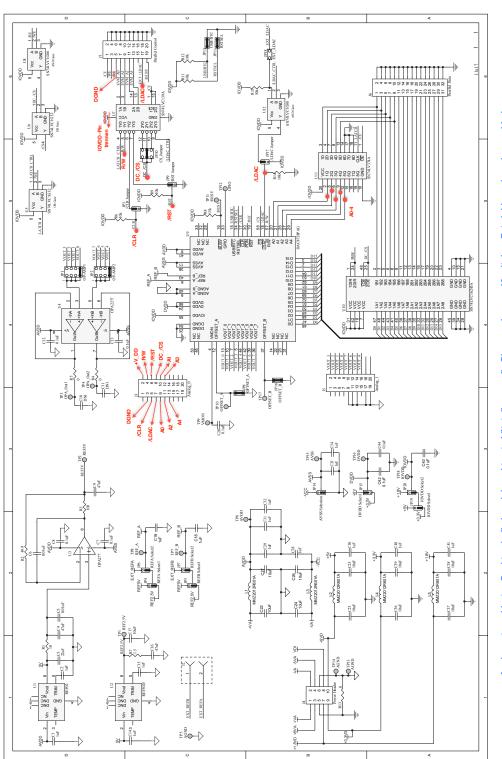

|    | A.1. Modifiziertes DAC Entwicklungsboard                      | 53 |

|    | A.2. Matlab Skripte                                           | 54 |

|    | A.2.1. Klirrfaktorbestimmung aus Messdaten eines Sinussignals | 54 |

|    | A.2.2. Frequenzbestimmung aus Messdaten eines Sinussignals    | 55 |

## 1 Einleitung

### 1.1 Motivation

Im Rahmen dieser Bachelorarbeit wurde eine digitale Signalsynthese auf einer rekonfigurierbaren Recheneinheit implementiert und analyisiert. Bei der Signalsynthese handelt es sich um die *Direct Digital Synthesis* (DDS). Die Signalsynthese ist ein wichtiges Thema in der Elektrotechnik und Informationstechnik. Durch die zunehmende Verwendung digitaler Komponenten gewinnt die digitale Signalsynthese an Bedeutung.

Auf dem Elektronikmarkt sind bereits fertige DDS Implementierungen auf einem Chip zu kaufen. [Anal99] Dennoch lohnt es sich, eine DDS auf einer rekonfigurierbaren Recheneinheit zu implementieren, weil sich damit Hardware-Kosten sparen lassen und eigene Anforderungen besser anpassen lassen. Ein bereits bestehendes System kann um eine DDS erweitert werden, sodass die Signalerzeugung parallel zur eigentlichen Anwendung läuft.

Diese DDS Implementierung soll verwendet werden, um Piezo-Elemente anzutreiben. Durch den piezoelektrischen Effekt wird eine Verformung von Materialien ermöglicht, wenn eine elektrische Spannung angelegt wird. [Aure01] Mithilfe der Piezo-Elemente sollen Motoren angetrieben werden.

### 1.2 Anforderungen

Die DDS soll auf einem Field Programmable Gate Array (FPGA) implementiert werden. Mithilfe einer DDS können beliebige periodische Signalformen dargestellt werden. Gefordert wird ein Sinussignal. Dabei sollen die Frequenz, Amplitude und Phasenverschiebung zur Laufzeit einstellbar sein. Eine Ausgangsspannung von -10 V bis +10 V wird gefordert. Der Frequenzbereich soll variierbar sein. Für das Schwingen der Piezo Elemente wird eine Frequenz zwischen 130 kHz und 150 kHz benötigt. Die Frequenzauflösung soll beliebig einstellbar sein. Die DDS soll eine beliebige Anzahl an Kanälen betreiben können. Für die Motoransteuerung werden drei Kanäle benötigt. Eine Klirrfaktor-Minimierung wird angestrebt.

# 2 Verfahren zur Sinuserzeugung

Es gibt verschiedene Verfahren zur Erzeugung eines Sinussignals. Im Folgenden werden grundlegende Prinzipien vorgestellt, um dieses elementare Signal zu generieren. Die unterschiedlichen Verfahren weisen allesamt sowohl Vor- als auch Nachteile auf und sollten je nach Anwendung eingesetzt werden.

# 2.1 LC-Schwingkreis

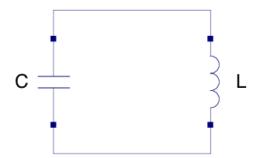

Ein LC-Schwingkreis stellt eine einfache Variante mit sehr geringem Aufwand dar, um ein Sinussignal zu erzeugen. In der Theorie werden lediglich zwei Bauteile gebraucht. Ein LC-Schwingkreis wird durch eine Schaltung realisiert, die aus einer Spule (L) und einem Kondensator (C) besteht. Die Bauteile können sowohl in Reihe, als auch parallel geschaltet werden. In Abbildung 2.1 ist die Schaltung eines LC-Parallelschwingkreises

Abbildung 2.1.: LC-Parallelschwingkreis

dargestellt. Die Schaltung stellt das theoretische Prinzip dar und beachtet dabei keine Verluste.

In dem Schwingkreis wird periodisch Energie zwischen dem magnetischen Feld der Spule und dem elektrischen Feld des Kondensators ausgetauscht, wodurch eine periodische Schwingung entsteht. Die Frequenz, mit der die Schaltung schwingt, ist die Resonanzfrequenz, die mithilfe der Thomsonschen Schwingungsgleichung

$$f_R = \frac{1}{2\pi\sqrt{LC}}\tag{2.1}$$

berechnet werden kann. [Ohmb11]

In der Praxis haben alle Bauteile Verluste. Kondensatoren und Spulen besitzen ohmsche Widerstände, die Verluste verursachen. Leitungen und Kontaktflächen sind die Ursachen für diese Widerstände. Bei Spulen wird der ohmsche Widerstand durch die vorhandenen Drahtwindungen stark beeinflusst. Außerdem werden Verluste durch abgestrahlte elektromagnetische Wellen erzeugt. Diese entstehen durch eine nicht vollständig isolierende Außenschicht an den Bauteilen. Die Verluste beeinflussen das Verhalten der Komponenten. Sie verursachen eine abweichende Ausgangsfrequenz.

Des Weiteren haben alle Bauteile Toleranzen, die vom Hersteller angegeben werden. Je nachdem, welche Fertigungsqualität verwendet wurde, können die Toleranzen zwischen 1 % und 10 % betragen. Die abweichenden Bauteilwerte beeinflussen ebenfalls die Resonanzfrequenz.

Neben den Bauteiltoleranzen und den Verlusten kann auch die Temperatur das Verhalten der Komponenten beeinflussen. Bei hohen oder niedrigen Temperaturen weisen die Bauteile in der Regel andere Werte auf, als bei Zimmertemperatur. Gerade die Eigenerwärmung der Bauteile kann während des laufenden Betriebs die Ausgangsfrequenz verändern.

Des Weiteren würde der Schwingkreis, wenn er einmal eingeschwungen ist, wegen der Dämpfung bzw. der ohmschen Widerstände, nur eine bestimmte Zeit schwingen und dabei abklingen. Aus diesem Grund werden aktive Verstärkerschaltungen verwendet, um dem Schwingkreis die benötigte Energie zu liefern, sodass die Verluste der ohmschen Widerstände kompensiert werden. [Brau04]

Für eine veränderbare Resonanzfrequenz ist ein variabler Kondensator und/oder eine variable Spule erforderlich. Für einen variablen Kondensator kann z.B. ein Drehkondensator verwendet werden. Bei einer Spule wird ein veränderlicher Wert erreicht, indem ein frei beweglicher Kern benutzt wird, der in die Spule hinein- und hinausgeschoben werden kann. Dadurch lässt sich die Kapazität und/oder Induktivität verändern. Die Frequenz wird innerhalb einer bestimmten Bandbreite einstellbar.

### 2.2 RC-Oszillator

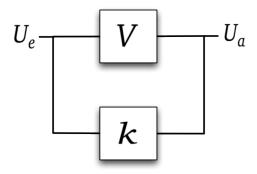

Um ein Sinussignal zu erzeugen, kann ein Oszillator verwendet werden. Ein Oszillator kann mit einem Verstärker V (Verstärkung  $\underline{V}$ ) und einer Rückkopplung k (Verstärkung  $\underline{k}$ ) aufgebaut werden. Das System muss eine Selbstregelung beinhalten, mit der Verluste ausgeglichen werden. Abbildung 2.2 zeigt das Blockschaltbild eines Oszillators.

Abbildung 2.2.: Oszillator System

V und k sind beliebige Übertragungsfunktionen mit frequenzabhängiger Amplitudenverstärkung und Phasenverschiebung. Für ein schwingungsfähiges System muss die Schleifenverstärkung  $\underline{k} \cdot \underline{V} \geq 1$  sein (Schwingbedingung). Wenn die Phasenverschiebung für einen Schleifenumlauf bei einer Frequenz  $\phi_k + \phi_V = 0$  bzw. ein Vielfaches von 360° ist (Phasenbedingung), entsteht eine eigenständige Schwingung in genau dieser Frequenz (Oszillatorfrequenz).

Um die Oszillatorfrequenz zu bestimmen, werden frequenzabhängige Netzwerke in dem rückgekoppelten System eingesetzt. Diese Netzwerke erfüllen die Phasenbedingung bei genau einer Frequenz. Es können z.B. RC-Glieder, Schwingkreise oder Quarze eingesetzt werden. [Schm11b]

Abbildung 2.3 zeigt die Schaltung eines RC-Oszillators. (Vgl.: [Hein11], [Schm11b], [Lehw11])

Abbildung 2.3.: RC-Oszillator Schaltung

Jedes RC-Glied erzeugt eine Phasenverschiebung zwischen 0° und 90°. Somit sind in dem RC-Phasenschiebernetzwerk mindestens drei gleich dimensionierte RC-Glieder notwendig, um die Phase um 180° zu drehen. Jedes RC-Glied dreht die Phase dann um 60°. [Miet11] Bei  $\phi_k = -180^\circ$  wird die Phasenbedingung erfüllt, weil der Operationsverstärker durch den invertierenden Anschluss die Phase um  $\phi_V = 180^\circ$  dreht. [Schm11b]

Die Oszillatorfrequenz ergibt sich nach [Lehw11] zu:

$$f_O = \frac{\sqrt{6}}{2\pi \cdot RC} \tag{2.2}$$

Der Verstärker muss die Abschwächung durch den Rückkopplungskreis ausgleichen. Der theoretische Verstärkungsfaktor muss nach [Miet11] bei  $\underline{V}=29$  liegen. Schaltungssimulationen haben gezeigt, dass der Faktor etwas über 29 liegen muss ( $\underline{V}\geq 31$  bei  $R_1=10$  M $\Omega$ ), damit eine ungedämpfte Schwingung erzeugt wird. Die Zeit, bis die Amplitude des Signals 95 % des Maximums erreicht hat (Einschwingzeit [Stef07]), beläuft sich in der Simulation auf ca. 200 ms.

RC-Oszillatoren benötigen keine Spulen, weshalb sie in tieferen Frequenzbereichen bis zu einigen MHz verwendet werden. Andere Oszillatoren benötigen bei diesen Frequenzen hohe Induktivitäten, welche viel Platz verbrauchen und teuer sind. [Meli07]

### 2.3 Rechteck als Grundfunktion

Ein Sinussignal lässt sich auch mit einem Rechtecksignal als Grundfunktion generieren. Das hat den Vorteil, dass die Frequenz leicht einstellbar ist, weil ein Rechtecksignal mit einfachen Mitteln und mit einer variierbaren Frequenz erzeugt werden kann. Das Rechtecksignal lässt sich z.B. mit einem astabilen Multivibrator erzeugen. Dabei wechselt die Ausgangsspannung der Schaltung periodisch zwischen den Zuständen High und Low. Neben Transistor-Entwürfen gibt es kommerzielle ICs (Integrated Circuits), die dieses Verhalten aufweisen. Bekannt ist vor allem der Timerbaustein NE555.

Bei dieser Methode zur Generierung eines Sinussignals wird ein Tiefpassfilter (TPF) benötigt. Dieser ist zwingend notwendig und entscheidet maßgebend die Qualität des Ausgangssignals. Es folgt ein kleiner Einblick in die Frequenztheorie, um zu erläutern, wieso ein TPF ein Rechtecksignal in ein Sinussignal wandeln kann.

Ein ideales, zeitsymmetrisches Rechtecksignal weist unendlich viele Frequenzanteile auf. Je höher die Oberwelle, desto kleiner ist die Amplitude dieser Welle. Die Wellen (Grundwelle, Oberwellen) in einem Frequenzspektrum sind einzelne Sinussignale, die in einem Rechteck überlagert vorkommen. Wir betrachten die Fouriertransformierte eines Rechtecksignals in Gleichung 2.3. [KrSk08]

$$F(t) = \frac{4A}{\pi} \cdot \sum_{k=0}^{\infty} \frac{\sin((2k+1)\omega t)}{2k+1}$$

(2.3)

Die Variable *A* bestimmt die Amplitude des Rechtecksignals, *k* den Grad der Oberwelle. Die Gleichung verdeutlicht, dass ein ideales Rechtecksignal durch unendlich viele Sinussignale dargestellt werden kann. Ein steigendes *k* verursacht einen kleineren Funktionswert, was die kleinere Amplitude bei höheren Oberwellen erklärt.

Für die Erzeugung eines Sinussignals ist nur die Grundwelle von Interesse und man versucht, die Oberwellen zu unterdrücken. Dazu wird ein Tiefpassfilter verwendet. Bei einem Tiefpassfilter wird die sogenannte Grenzfrequenz  $f_g$  angegeben. Als Grenzfrequenz wird die Frequenz bezeichnet, bei der die Amplitude des Signals um das  $\frac{1}{\sqrt{2}}$ -fache gedämpft wird. Dies entspricht etwa -3 dB. Der Phasenwinkel beträgt bei der Grenzfrequenz 45 Grad. [Herb02] Frequenzen unterhalb der Grenzfrequenz gelten als durchgelassen. Frequenzen oberhalb von  $f_g$  gelten als gesperrt.

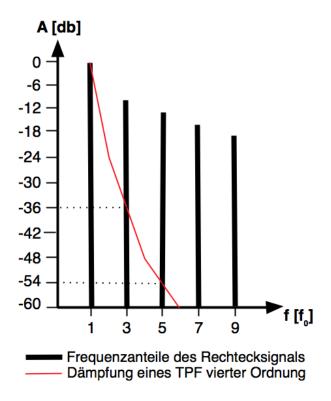

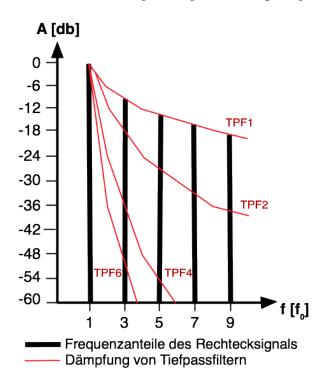

Abbildung 2.4 zeigt das Frequenzspektrum eines Rechtecksignals mit einer Grundfrequenz  $f_0$ .

Die Grundwelle liegt bei  $1 \cdot f_0$ . Die erste Oberwelle befindet sich bei einem idealen Rechtecksignal bei  $3 \cdot f_0$ . Die weiteren Oberwellen liegen bei  $5 \cdot f_0$ ,  $7 \cdot f_0$ , usw. Die rote Linie in der Abbildung stellt exemplarisch die Dämpfung eines Tiefpassfilters dar und beträgt 80 dB pro Dekade. Die Grundwelle wird nicht bzw. nur sehr wenig gedämpft. Die erste Oberwelle dagegen wird bereits um 36 dB gedämpft und die Amplitude der zweiten Oberwelle wird mit 54 dB stark gedämpft. Alle Amplituden der höheren Oberwellen kommen sehr stark gedämpft im Ausgangssignal vor. Da die Grundwelle des Rechtecksignals bereits ein ideales Sinussignal darstellt, wächst die Signalqualität mit steigender Flankensteilheit des Tiefpassfilters. [Weiß05] [Herb02]

Die Theorie von Tiefpassfiltern und wie die Flankensteilheit verbessert werden kann, wird in Kapitel 3.5 erläutert.

Abbildung 2.4.: Frequenzspektrum eines Rechtecksignals

Wenn ein Sinussignal mit einer variablen Frequenz erzeugt werden soll, ist dies mithilfe eines Tiefpassfilters nur bedingt möglich. Zwischen der Grundwelle und der ersten Oberwelle liegt eine Bandbreite von  $\Delta f$  (bei einem Rechtecksignal  $\Delta f = 2 \cdot f_0$ ). In dieser Bandbreite muss die Grenzfrequenz des TPF liegen. Wenn eine größere Bandbreite benötigt wird, wäre entweder eine variable Grenzfrequenz oder mehrere Tiefpassfilter nötig. Bei dem Einsatz von mehreren TPFs müsste je nach eingestellter Frequenz der zugehörige TPF verwendet werden.

# 2.4 Direct Digital Synthesis

Die Direct Digital Synthesis ist eine aktuelle Technik zur Erzeugung beliebiger periodischer Signale. Im Unterschied zu den bisher vorgestellten Signalgeneratoren wird das Signal bei der DDS im Wesentlichen durch eine digitale Schaltung generiert.

### 2.4.1 Prinzip

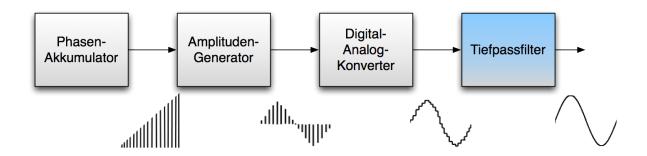

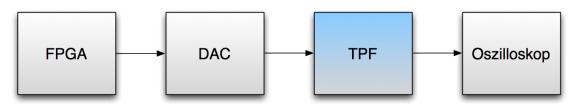

Die Direct Digital Synthesis arbeitet mit einem Akkumulator, einem Amplituden-Generator, einem Digital-Analog-Konverter (engl.: Digital-to-Analog-Converter, DAC) und einem (optionalen) Tiefpassfilter.

Abbildung 2.5 zeigt den schematischen Aufbau. Nach jedem System-Block sind die zugehörigen Ausgangssignale bei der Erzeugung eines Sinussignals skizziert. Durch den im Phasen-Akkumulator gespeicherten Wert wird die Amplitude ausfindig gemacht, welche anschließend an die gewünschte Amplitudenskalierung angepasst und

Abbildung 2.5.: Blockschaltbild der Direct Digital Synthesis

an den Digital-Analog-Konverter weitergegeben wird. Der DAC erzeugt aus dem anliegenden digitalen Wert den dazugehörigen Analogen. Die Werte der Amplituden liegen im Digitalen nur quantisiert vor. Nach einer Umwandlung in ein analoges Signal sind diese Quantisierungsfehler durch die entstandenen Stufen sichtbar. Zur Glättung des Signals kann ein Tiefpassfilter nachgeschaltet werden. Am Ausgang des TPF befindet sich ein Sinussignal mit abgeschwächten Stufen. [Stan11] Das Thema Tiefpassfilter wird in Kapitel 3.5 näher erläutert.

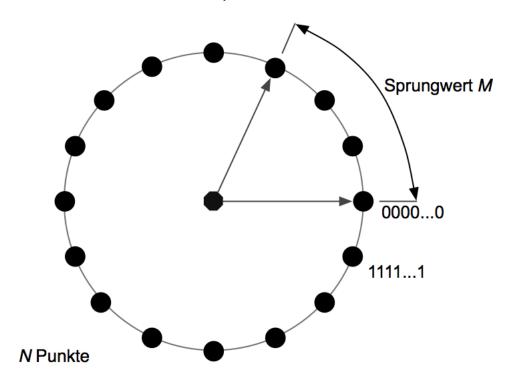

Die Schrittweite des Phasen-Akkumulators entscheidet über die Frequenz des Ausgangssignals. In Abbildung 2.6 ist die Phase eines periodischen Signals in Form eines Kreises dargestellt (Vgl. [Anal99]). Jeder der *N* Punkte entspricht einem Phasenwert. Wenn der Kreis einmal umlaufen wird, ist eine Periode vorüber.

**Abbildung 2.6.:** Periode anhand des Phasen-Kreises

Der Phasen-Akkumulator addiert in jedem Takt einen Sprungwert M, sodass der Kreis umlaufen und die Periode abgearbeitet wird. Bei einem größeren Sprungwert ist die Periode eines Signals schneller beendet. Der Wert M bestimmt damit direkt die

Frequenz des Ausgangssignals. Durch die Anzahl der Phasenwerte wird die mögliche Genauigkeit der Ausgangsfrequenz beeinflusst. Wenn mehr Phasenwerte vorhanden sind, kann eine exaktere Frequenz eingestellt werden.

Die Frequenz des Ausgangssignals  $f_{out}$  lässt sich mithilfe der Akkumulator-Frequenz  $f_{acc}$ , der Anzahl der Stützstellen N (die Anzahl der Punkte bzw. Phasenwerte) und des Sprungwertes M berechnen.  $f_{acc}$  bezeichnet die Frequenz, mit welcher der Akkumulator aktualisiert wird. Die Anzahl der Phasenwerte N ist beliebig. Jedoch bietet es sich auf digitalen Systemen an, eine Zweierpotenz zu wählen. Nur dann werden die verbrauchten Ressourcen vollständig genutzt und es wird keine extra Logik zur Überlauferkennung benötigt. Es ergibt sich  $N=2^{\overline{N}}$ , wobei  $\overline{N}$  die Bitbreite des Akkumulators darstellt. Gleichung 2.4 beschreibt die Berechnung der Ausgangsfrequenz. [Anal99]

$$f_{out} = \frac{f_{acc} \cdot M}{N} = \frac{f_{acc} \cdot M}{2^{\overline{N}}}$$

(2.4)

Wenn eine Ausgangsfrequenz gegeben ist, wird der Sprungwert *M* benötigt. Dieser wird durch Umstellen von Gleichung 2.4 berechnet:

$$M = \frac{f_{out} \cdot 2^{\overline{N}}}{f_{acc}} \tag{2.5}$$

Zu jedem der *N* Phasenwerte muss der Amplituden-Generator den entsprechenden Funktionswert des Ausgangssignals bereit stellen. Dies lässt sich im einfachsten Fall mit einer Look-Up Table (LUT) ermöglichen. In der LUT müssen die Funktionswerte fortlaufend gespeichert sein. Die Quantisierungsfehler können durch breitere und tiefere LUTs reduziert werden.

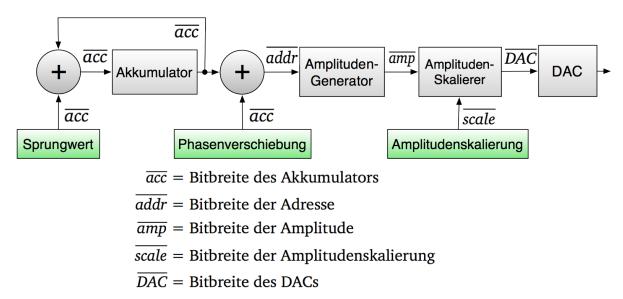

Abbildung 2.7.: Datenpfad der Direct Digital Synthesis

Abbildung 2.7 zeigt den konkreten Datenpfad einer DDS Implementierung mit konfigurierbaren Bitbreiten.

Die Eingangsvariablen Sprungwert, Phasenverschiebung und Amplitudenskalierung sind grün hinterlegt. Der Akkumulator wird durch den rückgekoppelten aktuellen Wert und dem Sprungwert gebildet. Der zweite Addierer addiert die Phasenverschiebung auf den im Akkumulator gespeicherten Wert. Die höchst signifikanten addr Bits werden als Adresse an den Amplituden-Generator gelegt, der den dazugehörigen Funktionswert am Ausgang bereitstellt. Der Amplituden-Generator kann z.B. durch eine LUT realisiert werden. Weitere Möglichkeiten zur Amplitudengenerierung werden in Kapitel 3.3 erläutert. Die restlichen Bits des Akkumulators haben keinen direkten Einfluss auf das Ausgangssignal. Sie werden dennoch benötigt, um die Genauigkeit der Ausgangsfrequenz zu gewährleisten. Der Sprungwert und die Phasenverschiebung haben eine festgelegte Bitbreite von  $\overline{acc}$ . So lassen sich der Sprungwert und die Phasenverschiebung mit einer maximalen Genauigkeit einstellen. Auf die Bestimmung der Bitbreiten wird in Kapitel 3.2 näher eingegangen. Die am Ausgang des Amplituden-Generators anliegenden Daten werden entsprechend der gewünschten Amplitude skaliert. Die Angabe der Amplitudenskalierung erfolgt mit einer einstellbaren Bitbreite von scale. Die angepassten Werte werden an den DAC weitergegeben. Am Ausgang liegt das analoge Signal vor.

# 2.4.2 Bewertung

Eine DDS erlaubt es, die Genauigkeit des zu erzeugenden Signals sehr flexibel einzustellen. Die Genauigkeit der analogen Signalsyntheseverfahren ist hingegen durch die Bauteiltoleranzen der verwendeten Komponenten sowie durch deren temperatur- und alterungsabhänigen Eigenschaften begrenzt. Durch das Einstellen der Frequenz, Phasenverschiebung und Amplitudenskalierung ist die DDS in vielen Bereichen einsetzbar. Komplexe Signalgeneratoren sind bei analoge Verfahren nur mit hohem Schaltungsaufwand möglich.

Ausserdem lassen sich beliebige Signale mit dem selben Schaltungsaufbau realisieren. Hierbei muss lediglich der Amplituden-Generator angepasst werden. [Brau04] [Anal99]

Durch die digitale Kontrolle des Ausgangs lässt sich die DDS sehr gut in andere digitale Systeme einbinden und von diesen nutzen.

Auf einer MCU (Micro-Controller-Unit) wird für die Implementierung einer DDS regelmäßig Rechenzeit benötigt. Dafür wäre die Verwendung von Interrupts nötig, wenn noch etwas anderes auf dieser Recheneinheit berechnet werden müsste. Durch diese andauernden Kontextwechsel ginge viel Zeit verloren. Deshalb ist die Verwendung einer Hardware-Implementierung besser geeignet. Die Genauigkeit bzw. Qualität des Ausgangssignals hängt stark von der Größe der verwendeten Register ab und beeinflusst somit direkt die benötigten Hardware-Ressourcen. Gerade bei beschränkten Hardware-Komponenten muss eine hardwareschonende Implementierung vorhanden sein.

# 3 DDS Implementierung

Die Verilog-Implementierung der DDS, der Ansteuerung eines geeigneten DAC sowie der verwendeten Testumgebung liegt dieser Arbeit bei.

### 3.1 Modulhierarchie

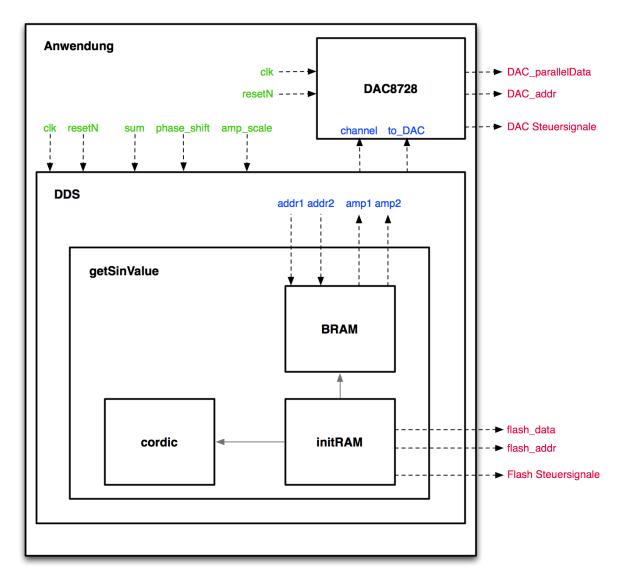

Die Direct Digital Synthesis wurde so aufgebaut, dass Änderungen oder Erweiterungen leicht implementierbar sind. Es gibt ein Hauptmodul *DDS*, das alle nötigen Untermodule instanziiert. Dieses muss mit einem DAC-Controller verbunden werden, der über ausreichend Ausgabekanäle verfügt. Die Modulhierarchie kann in Abbildung 3.1 eingesehen werden.

Abbildung 3.1.: Modulhierarchie

Die Modulhierarchie beinhaltet die wichtigsten Signalbezeichnungen. Alle Signale in grüner Schriftfarbe sind anwendungsspezifisch (Eingangssignale). Die blauen Bezeichner repräsentieren Werte, die von der *DDS* erzeugt bzw. verwendet werden. Die rot dargestellten Signale sind Ausgabewerte, welche mit der Hardware verbunden werden sollten. Die *DDS* selbst ist so aufgebaut, dass sie die Phasenwerte verwaltet und die Adressen an ein Modul *getSinValue* weitergibt. Hier wird der entsprechende Amplitudenwert ermittelt und der *DDS* mitgeteilt. Durch das Separieren des Amplituden-Generators ist es für die *DDS* nicht wichtig, wie die Amplitude ermittelt wurde. Lediglich die Dauer zum Abrufen eines Wertes (Anzahl Taktyzklen) muss bekannt sein. In der abgebildete Modulhierarchie wird ein Block-RAM (BRAM) als LUT genutzt. Kapitel 3.3 erläutert die Möglichkeiten zum Abrufen der Amplituden.

Eine weitere Flexibilität wird durch ein Modul *initRAM* erreicht. Dort wird der BRAM während der Initialisierung mit Amplitudenwerten gefüllt. Das Kapseln dieses Moduls ermöglicht eine leichte Erweiterung von unterschiedlichen Initialisierungsmethoden.

Die angegeben Signale und Module werden im Laufe der Arbeit diskutiert.

# 3.2 Erzeugung des Phasensignals

Der Akkumulator wird im DDS-Modul aktualisiert. Das Phasensignal wird durch die höchst signifikanten  $\overline{addr}$  Bits des Akkumulators dargestellt. Das Akkumulator-Register benötigt eine bestimmte Größe, um die gewünschte Frequenzauflösung zu erreichen.

In dieser Implementierung ist die Anzahl der Ausgabekanäle frei wählbar. Jeder Kanal benötigt seinen eigenen Akkumulator. Bei mehreren aktiven Kanälen werden die Akkumulatoren mit denselben Ressourcen aktualisiert. Dies geschieht gezeitmultiplext alle STEPS\_DAC·CHANNEL\_AMOUNT Taktzyklen. Um weitere Ressourcen zu sparen, werden die notwendigen Registerbreiten der Akkumulatoren und der Sprungwerte berechnet. So lassen sich nur die gewünschten Anforderungen erfüllen und es werden keine Bits bzw. Ressourcen verschwendet.

Bei der Initialisierung wird mit zwei Frequenzen (*FREQ\_OUT\_LOW*, *FREQ\_OUT\_HIGH*) das Frequenzband spezifiziert, innerhalb dessen alle Ausgabekanäle variiert werden sollen. Deshalb werden auf den Akkumulator der Sprungwert, welcher zu der unteren Frequenz *FREQ\_OUT\_LOW* gehört, und der Summand addiert, der individuell für jeden Kanal ist. Über diesen als Eingabeport variierbaren Summanden lässt sich die Ausgangsfrequenz innerhalb der Frequenzbandbreite einstellen.

Die Frequenzauflösung kann per Parameter *FREQ\_OUT\_RESOLUTION* angepasst werden. Diese Konfiguration beeinflusst die Breite der verwendeten Register und Addierer und wirkt sich damit direkt auf die benötigten Hardwareressourcen aus, wie im Folgenden gezeigt wird.

Der Akkumulator (N, Bitbreite des Akkumulators  $\overline{N}$ ) soll so groß sein, dass zu jedem Takt von  $f_{acc}$  eine minimale Auflösung von Q [Hz] addiert werden kann. Diese Größe wird durch die Zuweisung aus Gleichung 3.1 beschrieben. [Xili05]

$$N := \frac{f_{acc}}{O} \tag{3.1}$$

Die Akkumulatorgröße wird in der Implementierung durch Registerbreiten bestimmt. Deshalb sollte der Maximalwert des Akkumulators eine Zweierpotenz sein. Wenn der Akkumulator größer ist, als in Gleichung 3.1 definiert, wird die mögliche Auflösung kleiner. Dies ermöglicht ein genaueres Konfigurieren der Ausgangsfrequenz und erfüllt somit die mindest geforderte Auflösung Q. Die Bitbreite des Akkumulators lässt sich dann folgendermaßen berechnen:

$$N \ge \frac{f_{acc}}{Q} \tag{3.2}$$

$$\overline{N} \ge \log_2(\frac{f_{acc}}{Q}) \tag{3.3}$$

$$\overline{N} = \lceil \log_2(\frac{f_{acc}}{Q}) \rceil \tag{3.4}$$

Die Bitbreite für den übergebenen Summanden (sum, Breite des Summanden  $\overline{sum}$ ) lässt sich mithilfe der bereits bestimmten Akkumulatorgröße berechnen. Dabei wird Gleichung 2.4 aufgegriffen. Der Sprungwert M wird durch den Sprungwert der unteren Grenze des Frequenzbandes (base) und dem individuellen Sprungwert des Kanals bestimmt. Er ergibt sich also zu M:=base+sum.

$$f_{out} = f_{acc} \cdot \frac{base + sum}{2^{\overline{N}}} \tag{3.5}$$

Gleichung 3.5 wird umgestellt, um sum zu bestimmen:

$$sum = \frac{f_{out} \cdot 2^{\overline{N}}}{f_{acc}} - base \tag{3.6}$$

sum muss gerade so groß sein, dass sum + base das gesamte Frequenzband ( $\Delta f_{out} := FREQ\_OUT\_HIGH - FREQ\_OUT\_LOW$ ) abdeckt. Es folgt Gleichung 3.7.

$$sum = \frac{\Delta f_{out} \cdot 2^{\overline{N}}}{f_{acc}} \tag{3.7}$$

Der Wert für *sum* aus Gleichung 3.7 ist die minimal benötigte Größe. Deshalb darf die Größe für die Bitbreite aufgerundet werden und es ergibt sich für den Summanden:

$$\overline{sum} \ge \log_2(\frac{\Delta f_{out} \cdot 2^{\overline{N}}}{f_{acc}}) \tag{3.8}$$

$$\overline{sum} = \lceil \log_2(\frac{\Delta f_{out} \cdot 2^{\overline{N}}}{f_{acc}}) \rceil \tag{3.9}$$

Mit den Gleichungen 3.4 und 3.9 werden aus der konfigurierten Akkumulatorfrequenz, der Frequenzauflösung und dem Zielfrequenzband die minimalen Registerbreiten für den Akkumulator und den zur Laufzeit variierbaren Summanden bestimmt. Die

einstellbare Phasenverschiebung hat ebenfalls eine Bitbreite von  $\overline{N}$ . Damit erreicht die Phasenverschiebung ihre maximal mögliche Einstellgenauigkeit.

Ein typisches Beispiel mit einem Frequenzband zwischen 130 kHz und 170 kHz bei einer Auflösung von 0,01 Hz und einer Akkumulator-Frequenz von 15 MHz würde folgende Bitbreiten liefern:

$$\overline{N} = \lceil log_2(\frac{15 \text{ MHz}}{0.01 \text{ Hz}}) \rceil \approx \lceil 30,4832 \rceil = 31$$

$$\overline{sum} = \lceil log_2(\frac{40 \text{ kHz} \cdot 2^{\overline{31}}}{15 \text{ MHz}}) \rceil \approx \lceil 22,4493 \rceil = 23$$

Die berechneten Bitbreiten sind aufgerundet. Daher kann eine Vollaussteuerung des Summanden eine Frequenz oberhalb des Frequenzbandes erzeugen. Außerdem entspricht eine Veränderung des Summanden um Eins nicht exakt einer Frequenzänderung von FREQ\_OUT\_RESOLUTION, sondern ggf. einer kleineren Frequenzänderung.

# 3.3 Umsetzung zwischen Phase und Amplitude

Diese DDS Implementierung unterstützt verschiedene Methoden, um aus der Phase die Amplitude zu erhalten. Die unterschiedlichen Methoden werden im Modul *getSin-Value* umgesetzt.

Zum Einen lässt sich eine Look-Up Table verwenden. In dieser sind die Amplitudenwerte der geforderten Signalform gespeichert und werden zur Laufzeit ausgelesen. Weitere Details zu der LUT-Methode folgen in Kapitel 3.3.1. Neben der LUT-Methode kann die Amplitude auch zur Laufzeit mithilfe des CORDIC-Algorithmus berechnet werden, welcher in Kapitel 3.3.2 ausführlich behandelt wird.

Wenn die Amplitude zur aktuellen Phase vorliegt (*amp*), erfolgt die Anpassung an die eingestellte Amplitudenskalierung (*amp\_scale*). Gleichung 3.10 beschreibt diese Skalierung.

$$to\_DAC = \frac{amp \cdot amp\_scale}{2^{WIDTH\_AMP\_SCALE}}$$

(3.10)

Zur Reduktion des Speicherbedarfs wird die Symmetrie des Sinussignals ausgenutzt und nur eine Viertelperiode in der LUT abgelegt. Durch Spiegelung dieser Informationen lässt sich das Signal vollständig rekonstruieren. Gleichung 3.11 gibt an, wieviele Stützstellen für eine Periode vorhanden sind.

$$allSamples = samplesInRAM \cdot 4 = 2^{DEPTH\_SAMPLES} \cdot 4$$

(3.11)

Wie sich die unterschiedlichen Umsetzungen zur Generierung der Amplitude auf die Signalgüte und die verbrauchten Ressourcen auswirken, wird im Kapitel 4 behandelt.

### 3.3.1 LUT

Für eine LUT eignet sich z.B. ein ROM (Read Only Memory) oder BRAM, weil diese schnelle Zugriffs- und Antwortzeiten aufweisen. Ein Flash-Speicher sollte nicht als Look-Up Table verwendet werden. Der Stromverbrauch des verwendeten Flashs (ca. 50 mW [Numo07]) ist höher als bei dem FPGA internen BRAM (ca. 75  $\mu$ W [Acte09]), was gerade im Dauerbetrieb einen Nachteil darstellt. Wenn die Taktfrequenz der DDS hoch genug ist, kann der Flash-Speicher die Amplituden nicht schnell genug ausgeben, sodass die DDS auf den Flash warten muss. Die Taktfrequenz müsste bei einem DAC, der zwei Taktzyklen zum Entgegennehmen eines Wertes benötigt, und einem Flash-Speicher, der 75 ns zum Ausgeben eines Wertes braucht, über 26, 6 MHz liegen. Des Weiteren wird für eine später erläuterte Implementierungserweiterung (Kapitel 3.3.3) ein Dual-Port fähiger Speicher benötigt. Aus diesen Gründen wird ein BRAM als LUT genutzt.

Um eine Look-Up Table zu initialisieren, gibt es mehrere Möglichkeiten. Zwei davon werden hier vorgestellt.

Mithilfe eines externen Flash-Bausteins, in dem die Werte bereits vorhanden sind, können die Werte aus dem Flash-Speicher gelesen und in den BRAM geschrieben werden. Der Flash-Baustein speichert Daten dauerhaft auch ohne Stromversorgung und bedarf deshalb nur einer einmaligen Initialisierung, bei der die Werte z.B. auf dem PC berechnet werden können und dann auf den Flash-Speicher gespielt werden.

Außer einer Initialisierung mit einem Flash-Bausteins lässt sich der CORDIC-Algorithmus verwenden. Dabei werden die Amplituden allerdings nur einmal zur Initialisierung generiert und im RAM gespeichert.

### **3.3.2 CORDIC**

Für die Hardware-Realisierung einer Sinus-Funktion ist insbesondere der CORDIC-Algorithmus (*COordinate Rotation DIgital Computer*) geeignet. Es lassen sich zur Laufzeit iterativ Funktionswerte von verschiedenen elementaren Funktionen (z.B. trigonometrische, exponentiale, ...) auf Basis von Vektorrotationen auf dem Einheitskreis berechnen. Dabei verwendet der CORDIC-Algorithmus eine geeignete Schrittweite zum Verschieben des Einheitsvektors, bis der gesuchte Winkel gefunden wird. [GaDS11] [Riss04] Die Funktionsweise wird im Folgenden beschrieben.

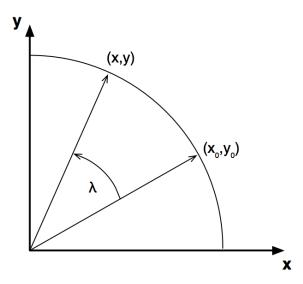

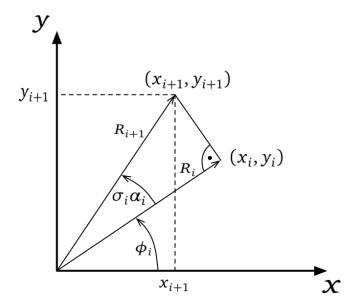

Abbildung 3.2 zeigt die Drehung eines Vektors  $(x_0, y_0)$  um den Winkel  $\lambda$ . Das Resultat ist der Vektor (x, y). Die Vektordrehung lässt sich durch Gleichung 3.12 und 3.13 beschreiben.

$$x = x_0 \cdot \cos(\lambda) - y_0 \cdot \sin(\lambda) \tag{3.12}$$

$$y = y_0 \cdot \cos(\lambda) + x_0 \cdot \sin(\lambda) \tag{3.13}$$

Um die Drehung um  $\lambda$  zu realisieren, wird bei dem CORDIC-Verfahren der Winkel  $\lambda$  durch Teilwinkel angenähert. Die Teilwinkel  $\alpha_i$  sind fest vorgegeben. n bezeichnet

**Abbildung 3.2.:** Drehung eines Vektors um  $\lambda$  Grad

die Anzahl der Teildrehungen (Iterationen). Es ergibt sich der Zusammenhang, wie in Gleichung 3.14 dargestellt.

$$\lambda \approx \sum_{i=0}^{n-1} \sigma_i \alpha_i \qquad \text{mit } \sigma_i \in \{1, -1\}$$

(3.14)

$\sigma_i$  gibt das Vorzeichen für die Teilwinkel an und sollte so gewählt werden, dass der Gesamtwinkel möglichst genau approximiert wird. Die Teilwinkel werden definiert zu:

$$\alpha_i := \arctan(2^{-i}) \tag{3.15}$$

Abbildung 3.3 zeigt die Verschiebung des Vektors  $(x_i, y_i)$  bei einem Teilschritt.

$R_i$  ist der Betrag zu dem Vektor  $(x_i, y_i)$ . Der Winkel des Vektors  $(x_i, y_i)$  wird durch  $\phi_i$  repräsentiert. Der Winkel der Teildrehung beträgt  $\alpha_i$  und besitzt das Vorzeichen  $\sigma_i$ . Durch die neu eingeführten Variablen lässt sich die Vektordrehung in Polar-

Koordinaten angeben, wie die Gleichungen 3.16 und 3.17 zeigen.

$$x_{i+1} = R_{i+1} \cdot \cos(\phi_i + \sigma_i \alpha_i)$$

(3.16)

$$y_{i+1} = R_{i+1} \cdot \sin(\phi_i + \sigma_i \alpha_i)$$

(3.17)

Es gelten außerdem die Beziehungen  $x_i = R_i \cdot \cos(\phi_i)$  und  $y_i = R_i \cdot \sin(\phi_i)$ . Die Gleichungen 3.16 und 3.17 lassen sich mithilfe des Additionstheorems für trigonometrische Funktionen umformen:

$$x_{i+1} = R_{i+1} \cdot \left[\cos(\phi_i)\cos(\sigma_i \alpha_i) - \sin(\phi_i)\sin(\sigma_i \alpha_i)\right]$$

(3.18)

$$x_{i+1} = R_{i+1} \cdot \left[ \frac{x_i}{R_i} \cos(\sigma_i \alpha_i) - \frac{y_i}{R_i} \sin(\sigma_i \alpha_i) \right]$$

(3.19)

$$x_{i+1} = \frac{R_{i+1}}{R_i} \cdot \left[ x_i \cos(\sigma_i \alpha_i) - y_i \sin(\sigma_i \alpha_i) \right]$$

(3.20)

Abbildung 3.3.: Verzerrung der Vektorlänge bei jeder Iteration

Man erhält  $y_{i+1}$  analog und es ergibt sich:

$$y_{i+1} = \frac{R_{i+1}}{R_i} \cdot \left[ y_i \cos \sigma_i \alpha_i + x_i \sin (\sigma_i \alpha_i) \right]$$

(3.21)

Der Vorfaktor wird definiert zu  $\frac{R_{i+1}}{R_i} := k_i$  und man erhält die Iterationsvorschriften:

$$x_{i+1} = k_i \cdot [x_i \cos(\sigma_i \alpha_i) - y_i \sin(\sigma_i \alpha_i)]$$

(3.22)

$$y_{i+1} = k_i \cdot [y_i \cos(\sigma_i \alpha_i) + x_i \sin(\sigma_i \alpha_i)]$$

(3.23)

Durch die Symmetrie des Kosinus ( $\cos(\sigma_i \alpha_i) = \cos(\alpha_i)$ ) und die Spiegelsymmetrie der Sinusfunktion ( $\sin(\sigma_i \alpha_i) = \sigma_i \sin(\alpha_i)$ ) lassen sich die Gleichugen vereinfachen:

$$x_{i+1} = k_i \cos(\alpha_i) \cdot [x_i - \sigma_i y_i \tan(\alpha_i)]$$

(3.24)

$$y_{i+1} = k_i \cos(\alpha_i) \cdot [y_i + \sigma_i x_i \tan(\alpha_i)]$$

(3.25)

Der Zusammenhang  $\sin^2(\alpha_i) + \cos^2(\alpha_i) = 1$  lässt sich mit  $\tan(\alpha_i) = \frac{\sin(\alpha_i)}{\cos(\alpha_i)}$  umstellen:

$$\cos(\alpha_i) = \frac{1}{\sqrt{1 + \tan^2(\alpha_i)}}$$

(3.26)

Damit lassen sich die Gleichungen 3.24 und 3.25 umformen.

$$x_{i+1} = k_i \cdot \frac{1}{\sqrt{1 + \tan^2(\alpha_i)}} \cdot [x_i - \sigma_i y_i \tan(\alpha_i)]$$

(3.27)

$$y_{i+1} = k_i \cdot \frac{1}{\sqrt{1 + \tan^2(\alpha_i)}} \cdot [y_i + \sigma_i x_i \tan(\alpha_i)]$$

(3.28)

Durch die Definition aus Gleichung 3.15 ergibt sich für den Tangens:

$$\tan(\alpha_i) = 2^{-i} \tag{3.29}$$

Die Iterationsvorschriften lassen sich weiter vereinfachen:

$$x_{i+1} = k_i \cdot \frac{1}{\sqrt{1 + 2^{-2i}}} \cdot [x_i - \sigma_i y_i 2^{-i}]$$

(3.30)

$$y_{i+1} = k_i \cdot \frac{1}{\sqrt{1 + 2^{-2i}}} \cdot [y_i + \sigma_i x_i 2^{-i}]$$

(3.31)

Der Skalierungsfaktor  $k_i$  ergibt sich aus Abbildung 3.3 ( $\cos(\alpha_i) = \frac{R_i}{R_{i+1}}$ ):

$$k_i = \frac{1}{\cos(\alpha_i)} = \sqrt{1 + 2^{-2i}}$$

(3.32)

Dann ergeben sich aus den Gleichungen 3.30 und 3.31 die Iterationsvorschriften:

$$x_{i+1} = x_i - \sigma_i y_i 2^{-i} \tag{3.33}$$

$$y_{i+1} = y_i + \sigma_i x_i 2^{-i} (3.34)$$

Der Wert  $x_i$  entspricht dem Sinuswert nach der i-ten Iteration,  $y_i$  dem Kosinus. Die Iterationsvorschriften benötigen keine Multiplikation mehr, sondern lediglich Schiebeoperationen und Additionen.

Während jeder Iteration muss die Drehrichtung  $\sigma_i$  bestimmt werden. Deshalb wird eine zusätzliche Variable eingeführt, die ebenfalls pro Iteration berechnet wird:

$$z_{i+1} := z_i - \sigma_i \alpha_i \tag{3.35}$$

Die Variable  $z_i$  gibt den aktuellen Winkel an. Der gesuchte Anfangswinkel wird mit  $z_0 = \lambda$  definiert. Wenn  $z_i$  negativ ist, soll der nächste Teilwinkel addiert werden, bei positivem  $z_i$  subtrahiert. Weil in den angegeben Gleichungen  $\sigma_i$  subtrahiert wird, gilt:

$$\sigma_i = \begin{cases} -1, & \text{wenn } z_i < 0\\ 1, & \text{wenn } z_i \ge 0 \end{cases}$$

(3.36)

In der Definition von  $z_{i+1}$  werden die Konstanten  $\alpha_i$  verwendet. Diese Konstanten können vorab berechnet werden und verursachen so keinen weiteren Rechenaufwand.

Nach der Durchführung von n Iterationen müssen die Ergebnisse  $x_{n-1}$  und  $y_{n-1}$  aufgrund der fortlaufenden Betragsskalierung mit dem folgenden Faktor zurück auf den Einheitskreis normiert werden:

$$K = \prod_{i=0}^{n-1} k_i = \prod_{i=0}^{n-1} \sqrt{1 + 2^{-2i}}$$

(3.37)

Bei einer Grenzwertbetrachtung von K mit  $n \to \infty$  läuft der Skalierungsfaktor gegen  $K \approx 1,64676$ . Dies entspricht einer Multiplikation mit  $K^{-1} \approx 0,607253$ . Der Skalierungsfaktor ist in dieser Implementierung zur Vereinfachung für alle Iterationsanzahlen gleich und wird durch eine angepasste Fließkommaarithmetik mithilfe von acht Shift Operationen und Additionen berechnet. Dies entspricht in etwa der Genauigkeit einer 16-bit Fließkommaarithmetik.

Mit der hier vorgestellten Version des CORDIC-Algorithmus lässt sich die Sinusund Kosinusfunktion approximieren und wird als *Rotation* bezeichnet. Charakteristisch daran ist die Konvergenz des Winkels  $z_i$  gegen Null. Des Weiteren gibt es noch das *Vectoring*. Dort lässt sich die Phase und der Betrag eines Vektors bestimmen. Die Variable  $y_i$  konvergiert dabei gegen Null. Außerdem lässt sich das CORDIC-Verfahren verallgemeinern, sodass neben den trigonometrischen weitere mathematische Funktionen realisierbar sind. Auf das Prinzip wird hier nicht näher eingegangen, weil es für diese DDS Implementierung nicht benötigt wird.

Das CORDIC-Verfahren erwartet drei Eingabewerte bzw. Anfangswerte. Je nachdem, wie die Anfangswerte gewählt werden, erhält man mit den unterschiedlichen Betriebsarten verschiedene mathematische Funktionen. Für eine Ausgabe von Sinusund Kosinuswerten werden die Anfangswerte im Rotationsmodus mit  $x_0 = 1$ ,  $y_0 = 0$  und  $z_0 = \lambda$  gewählt. Mit diesen Parametern erhält man  $x_n = \sin(z_0)$ ,  $y_n = \cos(z_0)$  und  $z_n = 0$ . Zur Vermeidung aufwändiger Fließkommaarithmetik wird der Wert  $x_0$  auf die geforderte Bitbreite skaliert ( $2^{WIDTH-1} - 1$ ) und man erhält als Ergebnis  $x_n = x_0 \cdot \sin(z_0)$  und  $y_n = x_0 \cdot \cos(z_0)$ . [Hahn91]

Neben dem CORDIC-Algorithmus gibt es weitere Approximationsmethoden, wie z.B. die Taylor-Reihe. Der CORDIC-Algorithmus verbraucht weniger Ressourcen im Vergleich zu Polynomapproximationen und vor allem keine Multiplikationen, wodurch er der Favorit bei einer Implementierung ist. [GaDS11] [Riss04]

Die Iterationen des CORDIC-Algorithmus können in Hardware unterschiedlich implementiert werden. Beim Zeitmultiplexen werden alle Iterationen auf den selben Ressourcen berechnet. Dabei wird zu jedem Takt eine Iteration ausgeführt. Nachdem alle Iterationen durchlaufen sind, liegt das Ergebnis eines Eingangswertes vor. Diese Methode ist ressourcenschonend, benötigt allerdings so viele Taktzyklen, wie Iterationen vorhanden sind, bis ein Ergebnis vorliegt.

Alternativ können die Iterationen in Hardware abgerollt werden. Dabei ist jedoch nur eine niedrige Taktfrequenz möglich, weil die Recheneinheit eine längere Zeit benötigt, bis alle Iterationsstufen durchlaufen sind. Durch das Einfügen von Registern zwischen den Iterationsstufen entsteht eine Pipeline, was eine höhere Taktfrequenz zulässt. Diese Methode liefert das erste Ergebnis nach einer von den Iterationen abhängigen Anzahl an Taktzyklen. Dafür kann die Pipeline zu jedem Takt einen Wert aufnehmen. Nachdem das erste Ergebnis vorliegt, liefert die Pipeline zu jedem Takt ein Ergebnis. Die Latenz der Pipeline muss bei der anschließenden Amplitudenskalierung und Kanalauswahl berücksichtigt werden. Durch die Pipeline lässt sich eine DDS ohne LUT implementieren, die in jedem Takt eine Amplitude berechnen kann. Allerdings benötigt diese Variante mehr Ressourcen als die gezeitmultiplexte Implementierung.

Die gezeitmultiplexte Methodik sollte bei einer CORDIC-Initialisierung der LUT verwendet werden, um den Ressourcenverbrauch zu minimieren. Die Pipeline-Variante ist bei einer Amplitudenberechnung zur Laufzeit sinnvoll.

# 3.3.3 Lineare Interpolation

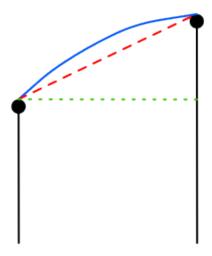

Eine Reduktion der in einer LUT abgelegten Stützstellen verringert zwar den Speicherbedarf und dessen Initialisierungszeit, verstärkt aber gleichzeitig die Quantisierung des erzeugten Signals. Um dem entgegenzuwirken lässt sich zwischen den Stützstellen linear interpolieren. Eine lineare Interpolation ist bei stetigen Funktionen sinnvoll, weil keine Funktionssprünge vorliegen. Sie lässt sich damit bei einer Sinusfunktion anwenden. Nicht förderlich wäre eine lineare Interpolation zum Beispiel bei Rechtecksignalen, wie der Pulsweitenmodulation (PWM).

Abbildung 3.4.: Lineare Interpolation zwischen zwei Stützstellen

Abbildung 3.4 zeigt eine lineare Interpolation (rot) zwischen zwei aufeinanderfolgenden Stützstellen (schwarz) einer Sinusfunktion (blau). Ohne Interpolation (grün) werden nur die zwei Stützstellen als Amplitude verwendet. Der interpolierte Verlauf kann den idealen Verlauf hingegen deutlich besser annähern.

In dieser DDS Implementierung wird der Phasenakkumulator in zwei Anteile aufgeteilt, wie in Abbildung 3.5 gezeigt.

Abbildung 3.5.: Phasen-Akkumulator Aufteilung

Die höchst signifikanten Bits werden als Adresse (*addr*) für den RAM verwendet. Die restlichen Bits haben dabei keinen direkten Einfluss auf die Adresse. Sie geben statt-dessen den *Interpolationsfaktor* an, mit dem zwischen den Stützstellen von *addr1* und

addr1+1=addr2 interpoliert wird. Dieser Faktor repräsentiert die Tendenz, an welcher Stelle sich gerade die Amplitude zwischen den Stützstellen befindet. Hierfür muss ein Amplituden-Generator verwendet werden, der zwei Werte pro Takt liefern kann. Bei einer LUT-Realisierung setzt dies die Verwendung von Dual-Port RAMs voraus. Unter Verwendung des CORDIC-Algorithmus ohne RAM muss dieser zweimal instanziiert werden. Bei der Pipeline-Variante müssen die Interpolationsfaktoren über die Pipelinestufen mitgeführt werden, da die Interpolation erst nach Ablauf der Pipelinelatenz erfolgen kann.

Konkret lässt sich die lineare Interpolation mit Gleichung 3.38 realisieren.

$$to\_DAC = amp1 + \frac{amp2 - amp1}{2^{\overline{Interpolationsfaktor}}} \cdot Interpolationsfaktor$$

(3.38)

*amp1*, *amp2* sind die Amplitudenwerte zu *addr1* und *addr2*. Mit *Interpolationsfaktor* ist die Bitbreite des *Interpolationsfaktors* gemeint.

# 3.4 Ansteuerung des Digital-Analog-Wandlers

Zur Umwandlung der durch die DDS berechneten digitalen Signale in analoge Spannungspegel wurde der Digital-Analog-Konverter DAC8728 [Texa09] von Texas Instruments verwendet. Das zugehörige Entwicklungsboard DAC8728EVM [Texa10] besitzt etliche Einstellungsmöglichkeiten per Jumper und Schnittstellen zur Anbindung externer Systeme.

Der DAC verfügt über acht unabhängige Kanäle mit einer Auflösung von 16 Bit, benötigt aber eine 5 Bit breite Adresse für zusätzliche Konfigurationen. Weitere Steuersignale dienen dem Zurücksetzen des DAC sowie dem Starten der Konvertierungen. Das mit maximal 50 MHz getaktete parallele Interface erlaubt eine schnelle Ansteuerung der Kanäle. [Texa10]

Um einem TI spezifischen Mikrokontroller-Interface gerecht zu werden, fasst das *DAC8728EVM* verschiedene Steuerleitungen zusammen und trennt die Adress- und Datenübertragung durch zwei Latches (*U10*, *U11*) in zwei Schritte. Dies erhöht die Zugriffszeit und erfordert eine vom eigentlichen *DAC8728*-Controller unterschiedliche Ansteuerungslogik.

Aus diesen Gründen wurde das Board so angepasst, dass die Latches und Demultiplexer umgangen werden. Das 16-Bit Latch wird über die  $\overline{OE}$  Pins permanent aktiviert und alle Adressleitungen direkt an eine freie 20-Pin Buchse gelegt. Die Steuersignale wurden ebenfalls an diese Buchse gelegt und die Demultiplexer deaktiviert.

Die neue Ansteuerung benötigt zehn Leitungen, wovon aber fünf Leitungen die Adresse sind. Das Board benötigt nun zwei Leitungen mehr als bei der Lösung von TI, allerdings ist der Datentransfer auch zweimal schneller. Mit dem modifizierten Boards sind zwei Takte nötig, bis ein Wert in den DAC geschrieben wurde. Im ersten Takt werden die Adresse und die Daten auf die Busse gelegt. Im zweiten Takt wird die Steuerleitung  $\overline{CS}$  deaktiviert, damit die Daten in den DAC geschrieben werden. Diese Daten werden mit Triggern des Steuersignals  $\overline{LDAC}$  konvertiert.

Die Ansteuerung des modifizierten Boards ist identisch zur Ansteuerung des DACs ohne das Entwicklungsboard und wurde im Modul *DAC8728* implementiert. Der modifizierte Schaltplan ist im Anhang A.1 zu finden.

Der DAC wird so angesteuert, dass er Daten, die er pro Kanal entgegennimmt, sofort in einen analogen Wert konvertiert. So ist sichergestellt, dass keine ungewollte Phasenverschiebung zwischen den Kanälen vorliegt. Die Alternative zu diesem Vorgehen wäre, alle Werte der Kanäle in den DAC zu schreiben und dann die Konvertierung von allen Kanälen zu starten. Dies würde jedoch eine Phasenverschiebung mit sich führen, weil die Werte zum Konvertierungszeitpunkt nicht mehr aktuell wären.

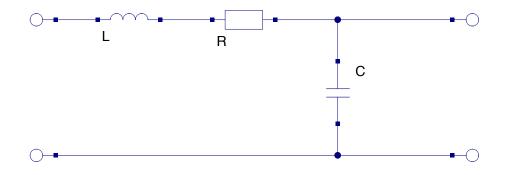

# 3.5 Tiefpassfilter

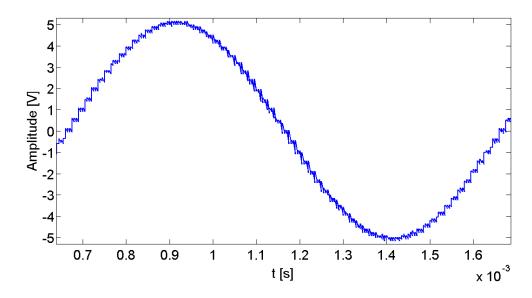

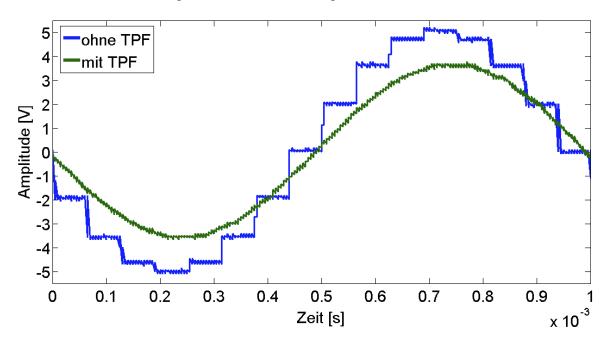

Bei digital erzeugten Signalen hat das Ausgangssignal eine stufige Form, weil im digitalen Bereich mit diskreten Werten gearbeitet wird. Abbildung 3.6 zeigt ein per DDS generiertes Sinussignal bei einer LUT-Tiefe von 16.

Abbildung 3.6.: Sinussignal bei 1 kHZ mit überlagertem Rechtecksignal

Das abgebildete Signal zeigt ein Sinussignal mit einem überlagerten Rechtecksignal. Durch die Rechteck-Anteile ergibt sich ein breiteres Frequenzspektrum. Die Frequenz des Rechtecksignals lässt sich mit Gleichung 3.39 bestimmen.

$$f_{Rechteck} = AnzahlSt \ddot{u}tzstellen \cdot f_{Sinus} = 2^{DEPTH\_SAMPLES} \cdot 4$$

(3.39)

Die Frequenz des überlagerten Rechtecksignals aus Abbildung 3.6 liegt demnach bei 64 kHz. Das Sinussignal kann außerdem Oberwellen durch Ungenauigkeiten in der digitalen Amplitudenerzeugung und der Digital-Analog-Umwandlung aufweisen. Die Frequenzen der Oberwellen eines Sinussignals befinden sich bei dem Vielfachen der Grundfrequenz. Ein dem DAC nachgeschalteter Tiefpassfilter mit einer Grenzfrequenz von  $f_g = f_{Grundwelle}$  kann sowohl die Oberwellen des Sinussignals, als auch die Rechteckanteile dämpfen.

Es gibt aktive und passive Tiefpassfilter. Aktive Tiefpassfilter haben mindestens ein aktives Bauteil in der Schaltung, z.B. einen Operationsverstärker. Passive dagegen greifen nur auf Widerstände, Kondensatoren und Induktivitäten zurück.

Ein Tiefpassfilter besitzt pro Ordnungszahl einen Energiespeicher. Je höher die Ordnungszahl eines Filters ist, desto steiler ist dessen Dämpfung. Zur Realisierung eines TPF höherer Ordnung können Filter erster und/oder zweiter Ordnung hintereinander geschaltet. Dabei müssen die einzelnen Filter unbelastet sein. Das heißt, nachgeschaltete Filter haben keine Rückwirkung auf ihre Vorgänger. Dies wird mithilfe eines aktiven Bauteils erreicht. So kann z.B. ein Operationsverstärker oder Transistor verwendet werden, der zwischen den hintereinander geschalteten Filtern liegt. [Schm11a]

Bei einem Tiefpassfilter n-ter Ordnung beträgt die Dämpfung  $n \cdot 20$  dB pro Dekade.

**Abbildung 3.7.:** Frequenzspektrum eines Rechtecksignals mit Dämpfungskennlinien von unterschiedlichen TPFs

Abbildung 3.7 zeigt den Verlauf der Dämpfung von Tiefpassfiltern unterschiedlicher Ordnung im Frequenzspektrum eines idealen Rechtecksignals mit Grundfrequenz  $f_0$ .

Der Tiefpass erster Ordnung (*TPF1*) dämpft die Oberwellen nur minimal bzw. gar nicht. Ein Tiefpassfilter sechster Ordnung dagegen besitzt eine sehr hohe Flankensteilheit und filtert die Grundwelle des gegebenen Signals besser. Er lässt in dem Beispiel von Abbildung 3.7 die Grundwelle mit einer stark gedämpften ersten Oberwelle und sehr stark gedämpften höheren Oberwellen passieren.

Ein Tiefpassfilter erster Ordnung benötigt genau einen Energiespeicher und muss daher entweder eine Spule oder einen Kondensator beinhalten. In Abbildung 3.8 ist ein solcher RC-Tiefpassfilter abgebildet.

Auf der linken Seite der Schaltung befindet sich die Eingangsspannung  $(U_e)$ , die gefiltert werden soll. Durch den Kondensator, der gegen Masse geschaltet ist, erreichen

Abbildung 3.8.: RC-Tiefpassfilter erster Ordnung

hohe Frequenzen nicht den Ausgang rechts ( $U_a$ ). Ein Kondensator ist für hohe Frequenzen niederohmig, weshalb Signale mit hohen Frequenzen über den Kondensator C leicht die Masse erreichen. Diese Frequenzanteile sind nur noch abgeschwächt im Ausgangssignal vorhanden.

Dieses Verhalten lässt sich an der Impedanzgleichung zur Übertragungsstrecke des RC-Tiefpassfilters aus Abbildung 3.8 erkennen.  $U_a$  fällt über dem Kondensator C ab,  $U_e$  über C und R. Es ergibt sich:

$$\underline{Z}(j\omega) = \frac{\underline{U}_a(j\omega)}{\underline{U}_e(j\omega)} = \frac{\underline{Z}_C}{R + \underline{Z}_C} = \frac{\frac{1}{j\omega C}}{R + \frac{1}{j\omega C}} = \frac{1}{1 + j\omega RC}$$

(3.40)

Die Gleichung wird normiert mithilfe der komplexen Kreisfrequenz  $s = j\omega$ :

$$\underline{Z}(s) = \frac{1}{1 + sRC} \tag{3.41}$$

Wir betrachten für  $\underline{U}_a(s) = \underline{U}_e(s) \cdot \underline{Z}(s) = \underline{U}_e(s) \cdot \frac{1}{1+sRC}$  in Gleichung 3.42 und 3.43 die Grenzwerte für die komplexe Kreisfrequenz s.

$$\lim_{s \to 0} \underline{U}_a = \lim_{s \to 0} \underline{U}_e \cdot \frac{1}{1 + sRC} = \underline{U}_e \tag{3.42}$$

$$\lim_{s \to \infty} \underline{U}_a = \lim_{s \to \infty} \underline{U}_e \cdot \frac{1}{1 + sRC} = 0 \tag{3.43}$$

Bei kleinen Frequenzen bzw. bei Gleichspannung (f=0 Hz) wird die Ausgangsspannung  $\underline{U}_a$  annähernd gleich  $\underline{U}_e$ . Signalbestandteile mit hoher Frequenz werden hingegen nicht vom Eingang auf den Ausgang übertragen..

Durch die Definition der Grenzfrequenz ( $\frac{U_a}{U_e} = \frac{1}{\sqrt{2}}$ ) ergibt sich aus Gleichung 3.40:

$$\frac{1}{\sqrt{2}} = \left| \frac{1}{1 + j\omega_g RC} \right| \tag{3.44}$$

$$\frac{1}{\sqrt{2}} = \frac{1}{\sqrt{1 + (\omega_{\sigma}RC)^2}} \tag{3.45}$$

$$\frac{1}{2} = \frac{1}{1 + \omega_g^2 R^2 C^2} \tag{3.46}$$

$$2 = 1 + \omega_g R^2 C^2 \tag{3.47}$$

Ersetzen der Kreisfrequenz durch die Frequenz ( $\omega_g=2\pi f_g$ ) und Auflösen nach  $f_g$  ergibt schließlich die Grenzfrequenz aus Gleichung 3.48. [Sche08] [Schm11a] [Umni11]

$$f_g = \frac{1}{2\pi RC} \tag{3.48}$$

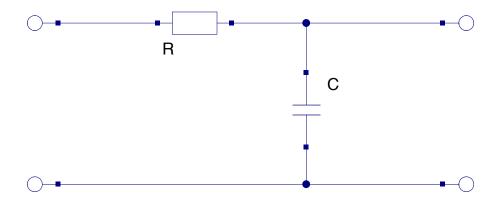

Bild 3.9 zeigt einen Tiefpassfilter zweiter Ordnung.

Abbildung 3.9.: LC-Tiefpassfilter zweiter Ordnung

Die Schaltung besitzt mit der Spule *L* einen weiteren Energiespeicher. Eine Spule ist für hohe Frequenzen hochohmig und lässt deshalb nur kleine Frequenzen passieren. Gleichung 3.49 zeigt die Impedanzgleichung eines LC-Tiefpasses zweiter Ordnung.

$$\underline{Z}(j\omega) = \frac{\underline{U}_a(j\omega)}{\underline{U}_e(j\omega)} = \frac{\frac{1}{j\omega C}}{j\omega L + R + \frac{1}{j\omega C}} = \frac{1}{1 + j\omega RC + (j\omega)^2 LC}$$

(3.49)

Die Gleichung wird wieder mit  $s = j\omega$  normiert und ist in Gleichung 3.50 dargestellt.

$$\underline{Z}(s) = \frac{1}{1 + sRC + s^2LC} \tag{3.50}$$

Eine Grenzwertbetrachung mit  $s \to 0$  und  $s \to \infty$  zeigt, dass hohe Frequenzen blockiert und niedrige Frequenzen durchgelassen werden.

Die Grenzfrequenz lässt sich in diesem Fall nicht mehr so einfach bestimmen. Zur Auslegung komplexer Filter sei daher auf [Schm11a] verwiesen.

Die charakteristischen Eigenschaften passiver Bauteile können vom Nennwert innerhalb einer vom Hersteller spezifizierten Toleranz abweichen. Wie sich die Toleranz auf die Grenzfrequenz bei einem Tiefpassfilter erster Ordnung auswirkt, zeigt Gleichung 3.51. Dabei wird auf Gleichung 3.48 zurückgegriffen.

$$f_g = \frac{1}{2\pi(R + \Delta R)(C + \Delta C)}$$

(3.51)

$\Delta R$  und  $\Delta C$  beschreibt die Abweichung zum angegeben Fertigungswert. Bei einer prozentualen Toleranz ergibt sich:

$$f_g = \frac{1}{2\pi (R + RT_R)(C + CT_C)}$$

(3.52)

Bei derselben Toleranz  $T=T_R=T_C$  resultiert die Grenzfrequenz zu:

$$f_g = \frac{1}{2\pi RC(1+T)^2} \tag{3.53}$$

Die relative Abweichung von der idealen Grenzfrequenz beläuft sich auf  $1 - \frac{1}{(1+T)^2}$ . Es sollten daher Bauteile mit einer kleinen Toleranz verwendet werden, um die bestmöglichen Ergebnisse zu erhalten.

### 3.6 Schnittstellen

Abschließend folgt eine Übersicht über die Parameter und Ports der Module *DDS* und *DAC8728*. Tabelle 3.1 zeigt das Interface der DDS. Alle Signale mit einem "N" am Ende ihres Namens sind active-low.

| Parameter      | In/Out | Beschreibung                                                |

|----------------|--------|-------------------------------------------------------------|

| FREQ_DIGITAL   | In     | Taktfrequenz des clk Signals                                |

| FREQ_OUT_LOW   | In     | Untere Schranke der Ausgabefrequenz                         |

| FREQ_OUT_HIGH  | In     | Obere Schranke der Ausgabefrequenz (we-                     |

|                |        | gen Rundungen kann die Ausgabefrequenz                      |

|                |        | größer sein)                                                |

| FREQ_OUT_RESO- | In     | Maximale Frequenzauflösung in Hz                            |

| LUTION         |        | (wegen Rundungen ggf. kleiner)                              |

| CHANNEL_AMOUNT | In     | Anzahl aktiver Kanäle                                       |

| DEPTH_SAMPLES  | In     | Anzahl Samples bzw. Stützstellen =                          |

|                |        | 2 <sup>DEPTH_SAMPLES</sup> · 4; Bitbreite der Adressleitung |

|                |        | zur LUT oder zum CORDIC-Algorithmus                         |

| WIDTH_SAMPLES  | In     | Bitbreite der Stützstellen                                  |

| WIDTH_DAC   In   Bitbreite des parallelen Bus des DACS   FLASH_DELAY   In   Taktzyklen, die der Flash für die Ausgabe eines Datensatzes benötigt   Taktzyklen, die der DAC für die Konvertierung eines Wertes benötigt   Taktzyklen, die der DAC für die Konvertierung eines Wertes benötigt   Anzahl der Iterationen, die der CORDIC-Algorithmus verwenden soll   Amplitudengenerierung per LUT (1) oder CORDIC_N[0:0]   In   Amplitudengenerierung per LUT (1) oder CORDIC_Algorithmus (0)   Intitalisierung der LUT per Flash-Speicher (1) oder CORDIC (0)   In   Aktivierung der Interpolation zwischen benachbarten Stützstellen   Schaltet die Iterationsstufen des CORDIC-Algorithmus hintereinander, wodurch bei jeder Taktflanke ein Ausgabewert berechnet wird   Schaltet die Iterationsstufen des CORDIC-Algorithmus hintereinander, wodurch bei jeder Taktflanke ein Ausgabewert berechnet wird   Schaltet die Iterationsstufen des CORDIC-Algorithmus hintereinander, wodurch bei jeder Taktflanke ein Ausgabewert berechnet wird   Schaltet die Iterationsstufen des CORDIC-Algorithmus hintereinander, wodurch bei jeder Taktflanke ein Ausgabewert berechnet wird   In   Konstanten für die angegebene Anzahl an Iterationsschritten des CORDIC-Algorithmus Muss bei WIDTH SAMPLES ≠ 16 oder CORDIC_CONSTANTS > 15 angepasst werden. LSB für Iteration Null.   Beschreibung   In   Datenbus eines Flashs (nicht benutzt, wenn der CORDIC-Algorithmus verwendet wird)   In   Individueller Sprungwert   In   Individueller Sprungwert   In   Individueller Sprungwert   In   Amplitudenskalierung   In   Amplitudenskalierung   In   Amplitudenskalierung   In   Amplitudenskalierung   In   Individueller Sprungwert   Individueller Sprungwert   Individueller Sprungwert   Individueller Sprungwert   Individueller Sprungwert   Individu                                                           | WIDTH AMP SCALE                                                                                                                                                                                 | In                               | Bitbreite der Amplitudenskalierung                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLASH_DELAY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | WIDTH DAC                                                                                                                                                                                       | In                               |                                                                                                                                                                                                                                                                                                                                                       |

| Taktzyklen, die der DAC für die Konvertierung eines Wertes benötigt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FLASH_DELAY                                                                                                                                                                                     | In                               | Taktzyklen, die der Flash für die Ausgabe ei-                                                                                                                                                                                                                                                                                                         |

| CORDIC_ITERATIONS       In       Anzahl der Iterationen, die der CORDIC-Algorithmus verwenden soll         RAM_CORDIC_N[0:0]       In       Amplitudengenerierung per LUT (1) oder CORDIC-Algorithmus (0)         FLASH_CORDIC_N[0:0]       In       Initialisierung der LUT per Flash-Speicher (1) oder CORDIC (0)         INTERPOLATION_BET-WEEN_SAMPLES[0:0]       In       Aktivierung der Interpolation zwischen benachbarten Stützstellen         CORDIC_PIPELINED[0:0]       In       Schaltet die Iterationsstufen des CORDIC-Algorithmus hintereinander, wodurch bei jeder Taktflanke ein Ausgabewert berechnet wird         CORDIC_ITERATIONS-WIDTH_SAMPLES:0]       In       Konstanten für die angegebene Anzahl an Iterationsschritten des CORDIC-Algorithmus. Muss bei WIDTH_SAMPLES ≠ 16 oder CORDIC_CONSTANTS > 15 angepasst werden. LSB für Iteration Null.         Port       In/Out       Beschreibung         Ik       In       Taktsignal (steigende Flanke)         resetN       In       Setzt die DDS zurück (asynchroner Reset)         flashData[31:0]       In       Datenbus eines Flashs (nicht benutzt, wenn der CORDIC-Algorithmus verwendet wird)         sum[WIDTH_ADD-LAMOUNT-1:0]       In       Individueller Sprungwert         CHANNEL_AMOUNT-1:0]       Phasenverschiebung         phase shiftWIDTH_AMP_SCALE · CHANNEL_AM-OUNT-1:0]       Amplitudenskalierung         graph scale[WIDTH_AMP_SCALE · CHANNEL_AM-OUNT-1:0]       Amplitudenskalierung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | STEPS_DAC                                                                                                                                                                                       | In                               | Taktzyklen, die der DAC für die Konvertie-                                                                                                                                                                                                                                                                                                            |

| RAM_CORDIC_N[0:0]       In CORDIC-Algorithmus (0)       Amplitudengenerierung per LUT (1) oder CORDIC-Algorithmus (0)         FLASH_CORDIC_N[0:0]       In Initialisierung der LUT per Flash-Speicher (1) oder CORDIC (0)         INTERPOLATION_BET-WEEN_SAMPLES[0:0]       In Aktivierung der Interpolation zwischen benachbarten Stützstellen         CORDIC_PIPELINED[0:0]       In Schaltet die Iterationsstufen des CORDIC-Algorithmus hintereinander, wodurch bei jeder Taktflanke ein Ausgabewert berechnet wird         CORDIC_CONSTANTS       In Konstanten für die angegebene Anzahl an Iterationsschritten des CORDIC-Algorithmus.         WIDTH_SAMPLES:0]       Muss bei WIDTH_SAMPLES ≠ 16 oder CORDIC_CONSTANTS > 15 angepasst werden. LSB für Iteration Null.         Port       In/Out Beschreibung         clk       In Taktsignal (steigende Flanke)         resetN       In Datenbus eines Flashs (nicht benutzt, wenn der CORDIC-Algorithmus verwendet wird)         sum[WIDTH_ADD-CHANNEL_AMOUNT-1:0]       In Individueller Sprungwert         CHANNEL_AMOUNT-1:0]       Phasenverschiebung         CHANNEL_AMOUNT-1:0]       The Amplitudenskalierung         scale [WIDTH_AMP_SCALE-CHANNEL_AM-OUNT-1:0]       Amplitudenskalierung         rdy       Out Zeigt an, ob die Initialisierung abgeschlossen ist         flashHiCeN       Out Chip Enable für den ersten Flash-Baustein flashCoen         flashOoN       Out Output Enable für den Flash         flashOoN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CORDIC_ITERATIONS                                                                                                                                                                               | In                               | Anzahl der Iterationen, die der CORDIC-                                                                                                                                                                                                                                                                                                               |

| FLASH_CORDIC_N[0:0]         In Initialisierung der LUT per Flash-Speicher (1) oder CORDIC (0)           INTERPOLATION_BET-WEEN_SAMPLES[0:0]         In Aktivierung der Interpolation zwischen benachbarten Stützstellen           CORDIC_PIPELINED[0:0]         In Schaltet die Iterationsstufen des CORDIC-Algorithmus hintereinander, wodurch bei jeder Taktflanke ein Ausgabewert berechnet wird           CORDIC_CONSTANTS [CORDIC_ITERATIONS-WIDTH_SAMPLES:0]         In Konstanten für die angegebene Anzahl an Iterationsschritten des CORDIC-Algorithmus. Muss bei WIDTH_SAMPLES ≠ 16 oder CORDIC_CONSTANTS > 15 angepasst werden. LSB für Iteration Null.           Port         In/Out         Beschreibung           clk         In Taktsignal (steigende Flanke)           resetN         In Setzt die DDS zurück (asynchroner Reset)           flashData[31:0]         In Datenbus eines Flashs (nicht benutzt, wenn der CORDIC-Algorithmus verwendet wird)           sum[WIDTH_ADD-CHANNEL_AMOUNT-1:0]         In Individueller Sprungwert           CHANNEL_AMOUNT-1:0]         In Phasenverschiebung           map_scale[WIDTH_AMP_SCALE · CHANNEL_AM-OUNT-1:0]         In Amplitudenskalierung           graph scale[WIDTH_AMP_SCALE · CHANNEL_AM-OUNT-1:0]         Out Zeigt an, ob die Initialisierung abgeschlossen ist           flashHiCeN         Out Chip Enable für den ersten Flash-Baustein           flashWeN         Out Write Enable für den Flash           flashVeN         Out Output Enable für den Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RAM_CORDIC_N[0:0]                                                                                                                                                                               | In                               | Amplitudengenerierung per LUT (1) oder                                                                                                                                                                                                                                                                                                                |

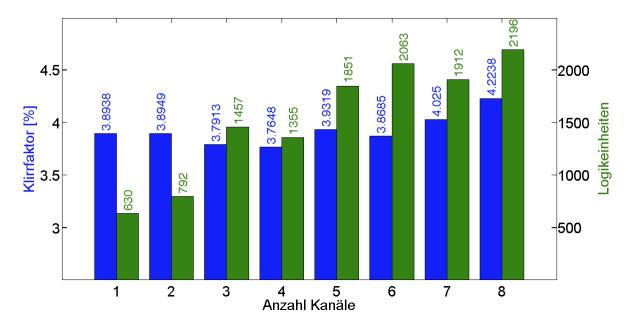

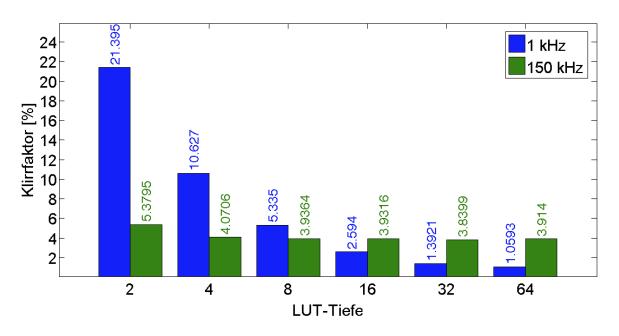

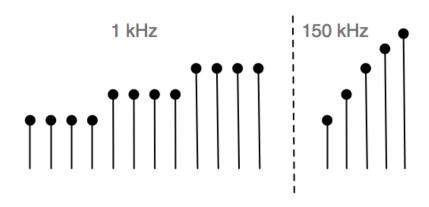

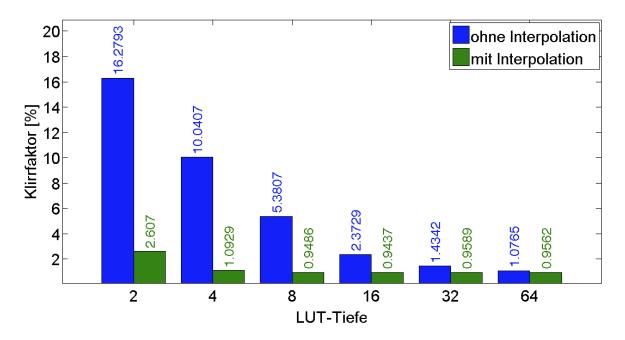

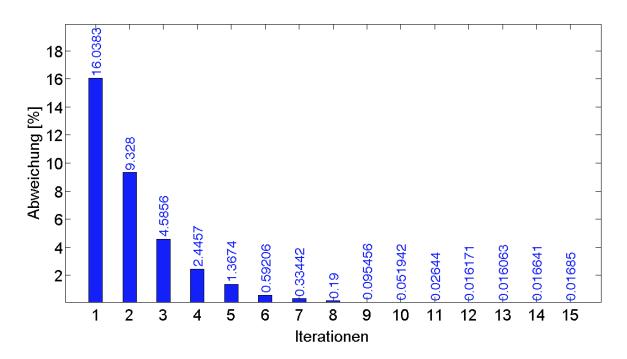

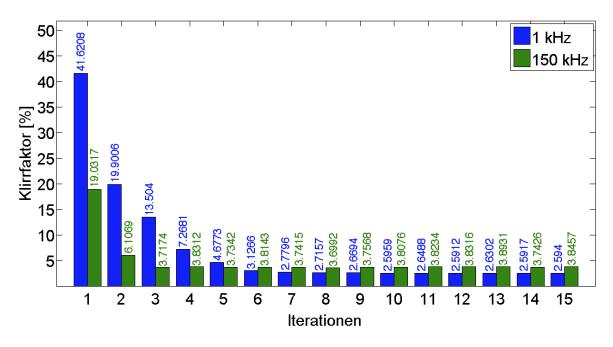

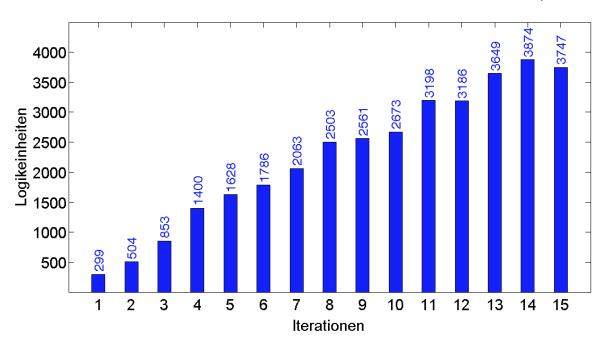

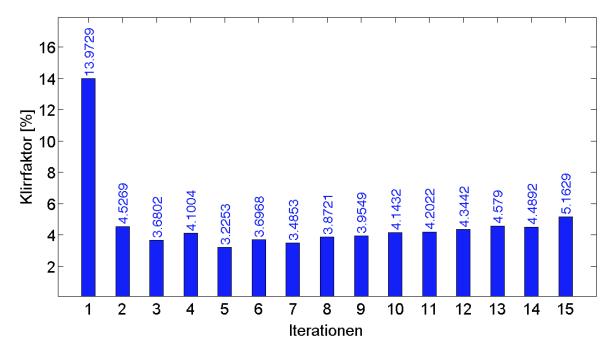

| WEEN_SAMPLES[0:0]       nachbarten Stützstellen         CORDIC_PIPELINED[0:0]       In       Schaltet die Iterationsstufen des CORDIC-Algorithmus hintereinander, wodurch bei jeder Taktflanke ein Ausgabewert berechnet wird         CORDIC_CONSTANTS       In       Konstanten für die angegebene Anzahl an Iterationsschritten des CORDIC-Algorithmus. Muss bei WIDTH_SAMPLES ≠ 16 oder CORDIC_CONSTANTS > 15 angepasst werden. LSB für Iteration Null.         Port       In/Out       Beschreibung         clk       In       Taktsignal (steigende Flanke)         resetN       In       Setzt die DDS zurück (asynchroner Reset)         flashData[31:0]       In       Datenbus eines Flashs (nicht benutzt, wenn der CORDIC-Algorithmus verwendet wird)         sum[WIDTH_ADD-CHANNEL_AMOUNT-1:0]       In       Individueller Sprungwert         CHANNEL_AMOUNT-1:0]       In       Phasenverschiebung         GALE · CHANNEL_AMOUNT-1:0]       In       Amplitudenskalierung         SCALE · CHANNEL_AMOUNT-1:0]       Out       Zeigt an, ob die Initialisierung abgeschlossen ist         flashHiCeN       Out       Chip Enable für den ersten Flash-Baustein         flashVeN       Out       Write Enable für den Flash         flashOeN       Out       Output Enable für den Flash         flashRstN       Out       Reset für den Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FLASH_CORDIC_N[0:0]                                                                                                                                                                             | In                               | Initialisierung der LUT per Flash-Speicher (1)                                                                                                                                                                                                                                                                                                        |