# Hardware-beschleunigte Drehmoment-regelung Ultraschallmotors

eines

adaptive Piezo-

Diplomarbeit von Paul Hildebrand, TU Darmstadt Dezember 2013

Paul Hildebrand

Matrikelnummer: 1314070

Studiengang: Automatisierungstechnik

Diplomarbeit:

Hardware-beschleunigte adaptive Drehmomentregelung eines Piezo-

Ultraschallmotors

Eingereicht: 20. Dezember 2013

Prüfer: Prof. Dr.-Ing. Andreas Koch Betreuer: Dipl.-Inform. Andreas Engel

FG Eingebettete Systeme und ihre Anwendungen

Fachbereich Informatik

Technische Universität Darmstadt

Hochschulstr. 10 64289 Darmstadt

Co-Betreuer: Dr. rer. nat. Peter P. Pott

Institut für Elektromechanische Konstruktion Fachbereich Elektro- und Informationstechnik

Technische Universität Darmstadt

Merckstr. 25

64283 Darmstadt

Ī

## Ehrenwörtliche Erklärung

Hiermit versichere ich, die vorliegende Diplomarbeit ohne Hilfe Dritter nur mit den angegebenen Quellen und Hilfsmitteln angefertigt zu haben. Alle Stellen, die den Quellen entnommen wurden, sind als solche kenntlich gemacht worden. Diese Arbeit hat in gleicher oder ähnlicher Form noch keiner Prüfungsbehörde vorgelegen.

Darmstadt, 20. Dezember 2013

Paul Hildebrand

## Kurzfassung

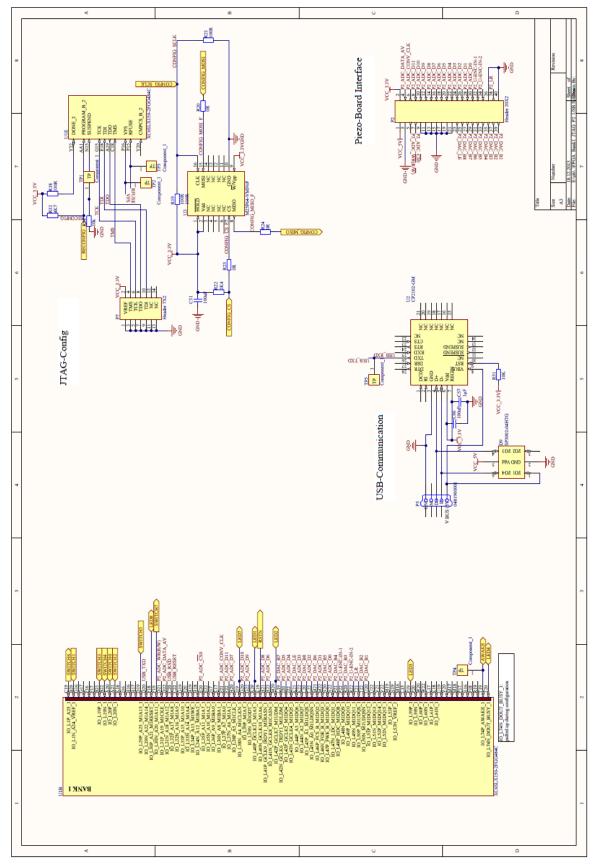

Im Rahmen der vorliegenden Arbeit wurde eine Platine mit einem FPGA als Reglerplattform entwickelt. Diese Platine soll zwei bereits bestehende voneinander unabhängige analoge Platinen (CONBOX und Signalkonditionierungsplatine) ansteuern. Für die CONBOX sollen Test-Module implementiert werden. Diese sind aus Zeitgründen entfallen.

Die zu entwerfende Platine beinhaltet neben dem FPGA die Spannungsversorgung, einen AD-Wandler, mehrere Speicher, einen UART zu USB Wandler, einen Voltage Monitor, einen Oszillator, mehrere LEDs und Schalter zur Benutzerinteraktion sowie Steckverbinder, um die Verbindung zu den analogen Platinen herzustellen. Gefertigt und bestückt wurde sie von einem kommerziellen Anbieter.

Die Signalkonditionierungsplatine wird im Zusammenhang mit einem Piezomotor verwendet. Als Anwendung für die Signalkonditionierungsplatine und den Piezomotor sollen VHDL-Module implementiert werden, die eine virtuelle Rasterung simulieren. Das anliegende Drehmoment soll über eine Messbrücke auf der Signalkonditionierungsplatine ermittelt und eine Drehmomentregelung für eine virtuelle Rasterung implementiert werden. Mit der Messbrücke war das Messen der proportional zum Drehmoment ausgegebenen Spannung nicht möglich. Die Ermittlung des Drehmoments erfolgte daraufhin mit einem externen Drehmomentsensor und es wurde festgestellt, dass das vom Piezomotor erzeugte Drehmoment nicht proportional zu der angelegten Motorspannung ist. Stattdessen wurde als einfachere Alternative eine Drehmomentsteuerung implementiert.

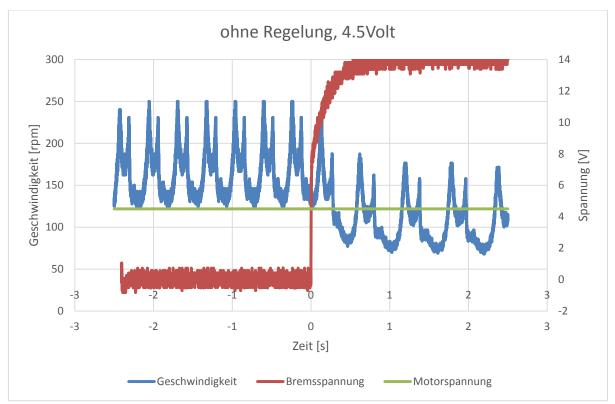

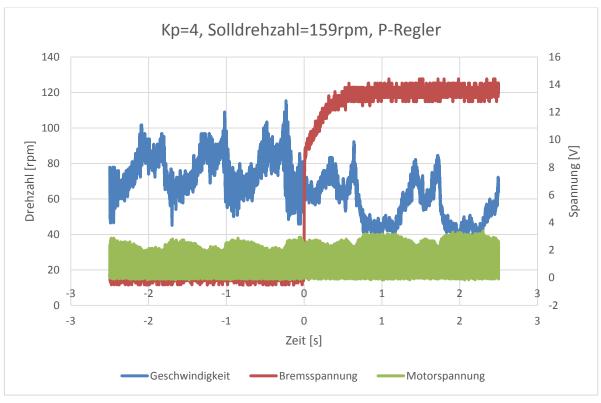

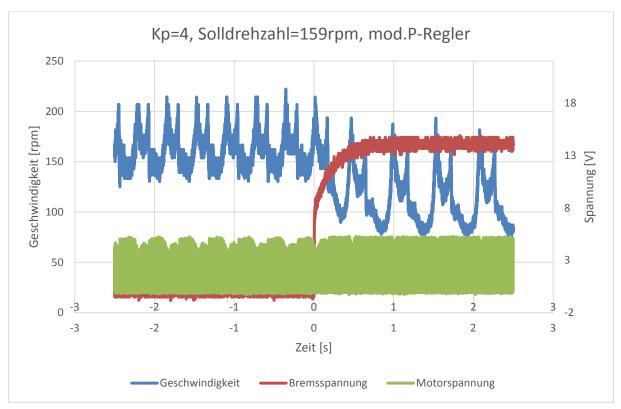

Als weitere Anwendung wurde eine Drehzahlregelung implementiert. Drei verschiedene Regler wurden implementiert, wobei lediglich zwei getestet wurden.

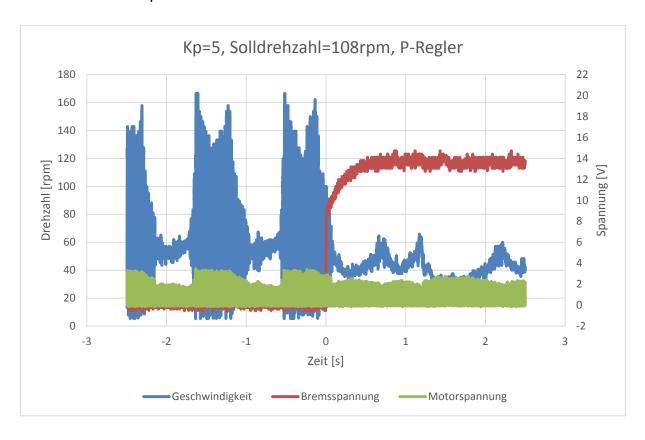

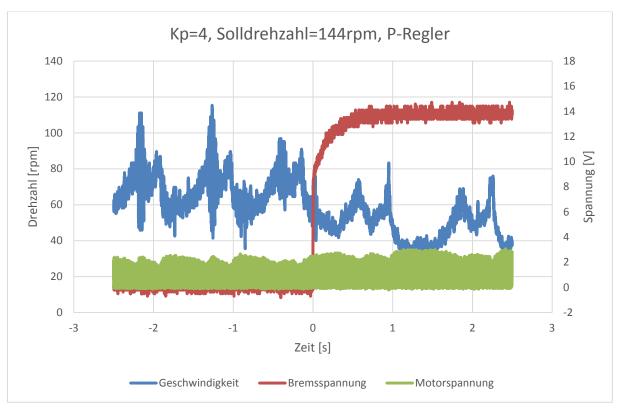

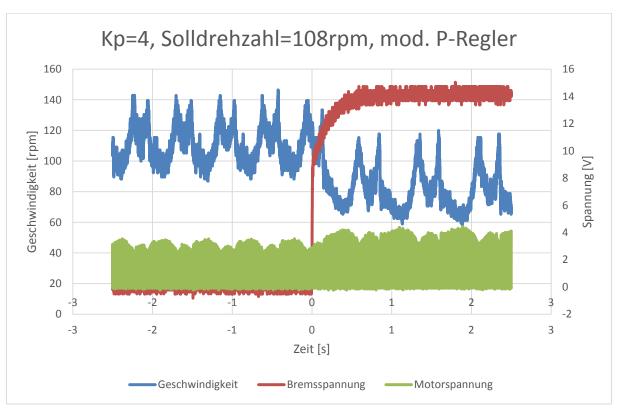

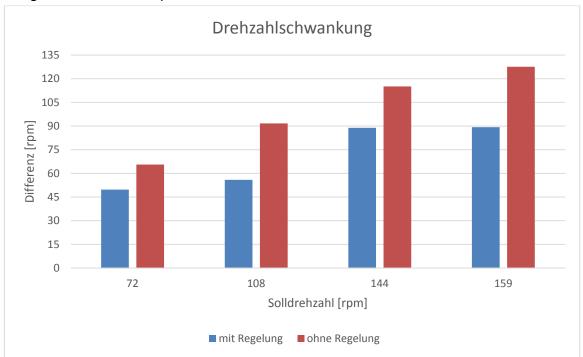

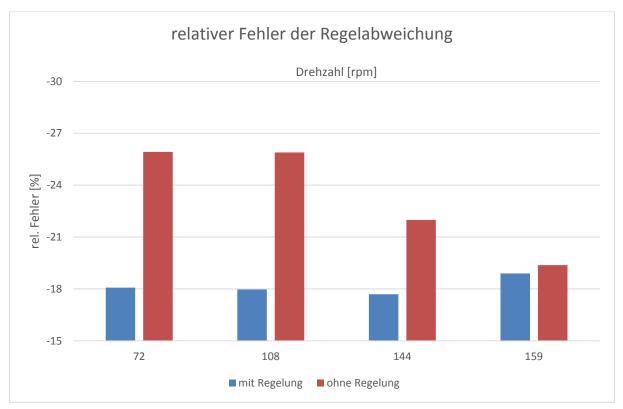

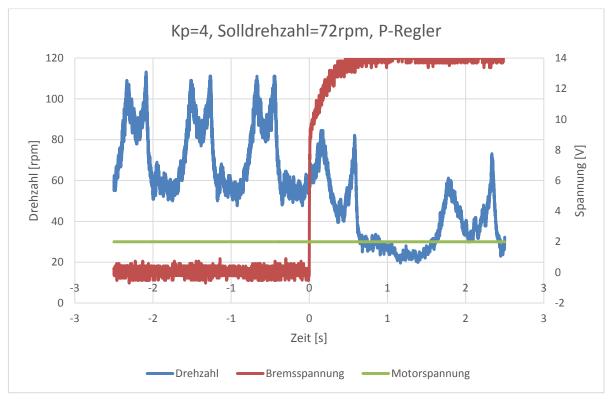

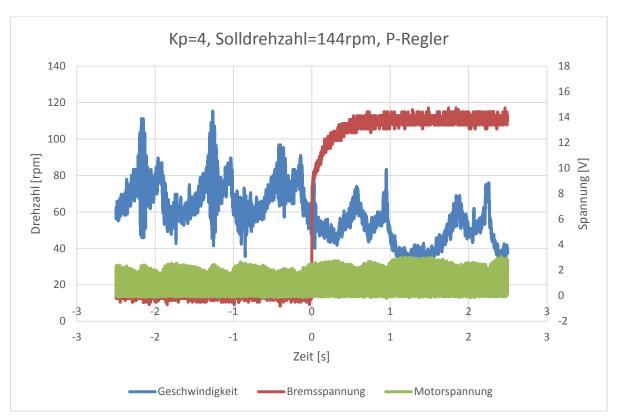

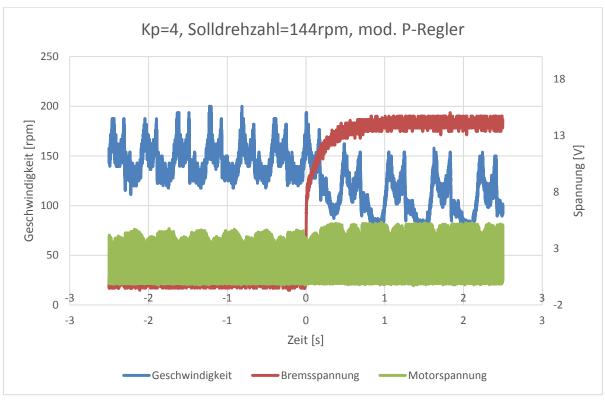

Zur Überprüfung der Wirksamkeit der Regler wurden Messungen durchgeführt. Der Piezomotor wurde mit einem Bremsmoment beaufschlagt und die Regelabweichung ermittelt. Sie betrug beim reinen P-Regler 62,5% bei einer Solldrehzahl von 108 rpm. Der P-Regler wurde modifiziert indem die Stellgröße mit einem Offset addiert wurde. Der Offset beträgt die Motorspannung, bei der Motor mit der Solldrehzahl dreht. Außerdem die der wurde Stellgrößenbeschränkung modifiziert. Die Regelabweichung der bei Solldrehzahl 108 rpm beträgt lediglich noch 18 %.

Die Parametrierung des PI-Reglers ist aus Zeitgründen entfallen.

# Inhaltsverzeichnis

| 1 | Ein  | leitung                                          | . 1 |

|---|------|--------------------------------------------------|-----|

| 2 | Klä  | rung der Aufgabenstellung                        | . 5 |

|   | 2.1  | PCB-Entwurf einer FPGA-basierten Reglerplattform | . 5 |

|   | 2.2  | Hardware-Beschreibung der Regleranwendungen      | . 7 |

| 3 | Ver  | wandte Arbeiten                                  | 9   |

| 4 | Auf  | bau der Leiterplatte                             | 11  |

|   | 4.1  | FPGA                                             | 11  |

|   | 4.2  | Spannungsversorgung                              | 13  |

|   | 4.3  | AD-Wandler                                       | 15  |

|   | 4.4  | Speicher                                         | 17  |

|   | 4.5  | USB                                              | 17  |

|   | 4.6  | Voltage Monitor / Power on Reset                 | 18  |

|   | 4.7  | Oszillator                                       | 19  |

|   | 4.8  | Steckverbinder, LEDs, Taster                     | 21  |

| 5 | FP   | GA Hardware-Design2                              | 24  |

|   | 5.1  | Haptisches Feedback                              | 24  |

|   | 5.2  | Testmodule für CONBOX                            | 39  |

| 6 | Erg  | ebnisse und Diskussion der Arbeit                | 41  |

|   | 6.1  | Inbetriebnahme                                   | 41  |

|   | 6.2  | Messungen mit Drehmomentsensor                   | 45  |

|   | 6.3  | Steuerung für virtuelle Rasterung                | 47  |

|   | 6.4  | Messungen mit Drehzahlregelung                   | 48  |

|   | 6.5  | Ergebnisse der Hardware-Synthese                 | 57  |

| 7 | Zus  | sammenfassung und Ausblick                       | 59  |

|   | 7.1  | Platinen                                         | 59  |

|   | 7.2  | FPGA Hardware-Design                             | 60  |

| A | Lite | raturverzeichnis6                                | 32  |

| В | Sch  | naltplan und Platinenlayout6                     | 33  |

| С | Ste  | ckerbelegungen/Positionen                        | 71  |

| D | Pin  | beleauna FPGA                                    | 76  |

| Ε | Messungen Drehzahlregelung | 79 |

|---|----------------------------|----|

| F | Abbildungsverzeichnis      | 84 |

| G | Tabellenverzeichnis        | 87 |

## Abkürzungsverzeichnis

AdRIA Adaptronik-Research, Innovation, Application

AD-Wandler Analog/Digital-Wandler ADC Analog Digital Converter

BGA Ball Grid Array

CAD computer-aided design CCL CMOS configurable latch

CMOS Complementary Metal Oxide Semiconductor

CONBOX Controller Box DATAV\_AV Data available

DA-Wandler

DDS

Direct Digital Synthesis

DIP

Dual in-line package

DSP

Digitaler Signalprozessor

EMK Institut für Elektromechanische Konstruktionen ESA Eingebettete Systeme und ihre Anwendungen

ESD electrostatic discharge

HACON Hardware-Accelerated Controller

IO input/output

ISE Integrated Software Environment

LED light-emitting diode

LOEWE Landes-Offensive zur Entwicklung Wissenschaftlich-

ökonomischer Exzellenz

LUT Lookup-Tabelle

PC Personal Computer

PCB Printed Circuit Board

PI-Regler Proportional-Intergral-Regler

ppr pulses per round

PWM Pulsweitenmodulation

REFIO Reference input output

rpm rounds per minute

SiKo-Platine Signalkonditionierungsplatine SMD Surface-mounted device

SNS Sense

SRAM Static random-access memory

SW Switch

UART Universal Asynchronous Receiver Transmitter

USB Universal Serial Bus

VHDL Very High Speed Integrated Circuit Hardware Description

Language

## **Symbolverzeichnis**

C Kondensator

$egin{array}{lll} c_0 & & \mbox{Lichtgeschwindigkeit} \\ C_p & \mbox{Piezomotorkapazität} \\ e & \mbox{Regelabweichung} \\ \end{array}$

e<sub>i</sub> summierte Regelabweichung für I-Anteil

e<sub>k</sub> Regelabweichung für P-Anteil

$\varepsilon_r$  Relative Permittivität

I Strom

$K_{i}$  Integrierbeiwert  $K_{p}$  Proportionalbeiwert

L Induktivität

I<sub>krit</sub> kritische Leitungslänge

$\begin{array}{lll} P & & Steckverbinder \\ R & & Widerstand \\ T_a & Abtastzeit \\ t_{rise} & Anstiegszeit \\ U & Spannung \end{array}$

$U_{0,AC}$  Wechselspannung  $U_{0,DC}$  Gleichspannung

$egin{array}{lll} u_1 & & & & & & \\ u_2 & & & & & \\ u_3 & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$

u<sub>max</sub> maximale Spannung u<sub>min</sub> minimale Spannung

u<sub>min,dez</sub> minimaler dezimaler Spannungswert

$\begin{array}{ll} v & & Geschwindigkeit \\ V_1 & & Potential \ an \ Stelle \ 1 \\ V_{Banken} & Spannung \ der \ I/O-B \ddot{a}nke \end{array}$

V<sub>ccaux</sub> Zusatzspannung

V<sub>ccint</sub> Spannung des Prozessorkerns

w Führungsgröße

ω Drehzahl

x aktuelle Drehzahl

y Regelgröße, Drehzahl des Piezomotors

z Störgröße

## 1 Einleitung

Das Institut ESA des Fachbereichs Informatik und das Institut EMK des Fachbereichs Elektro- und Informationstechnik arbeiten im LOEWE-Zentrum AdRIA am Einsatz von Piezomotoren für adaptronische Anwendungen. Ein Ziel dieser Zusammenarbeit ist es eingebettete Systeme mit Aktorik und Ansteuerungselektronik zu realisieren. Im Rahmen dieser Zusammenarbeit wurden bereits die CONBOX und eine Signalkonditionierungsplatine (SiKo-Platine) entwickelt.

Die CONBOX-Platine arbeitet analoge Signale auf und wird mit einem TMS320F28335 eZdsp Starter Kit, auf dem sich ein DSP befindet, verwendet. Das Starter Kit dient als Reglerplattform. Ein Vergleich mit einem FPGA als Reglerplattform soll in Zukunft erfolgen.

Die SiKo-Platine wurde in einer vorhergehenden Arbeit [1] entwickelt und nicht vollständig in Betrieb genommen. Die SiKo-Platine wird verwendet, um die analogen Signale bei der Ansteuerung eines Piezomotors zu konditionieren und für eine Reglerplattform bereitzustellen.

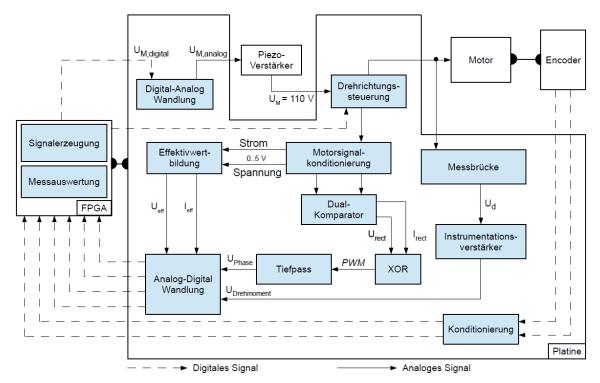

In Abbildung 1.1 ist der Signalverlauf dargestellt. Der DA-Wandler wandelt das von einer Reglerplattform vorgegebene Signal (U<sub>M, digital</sub>) in eine analoge Spannung (U<sub>M. analog</sub>) um. Diese Spannung wird im Piezoverstärker verstärkt und wieder auf die Platine geleitet, um die Höhe der Spannung (Ueff) zu bestimmen und den Strom (Ieff) zu messen. Die Phasenlage zwischen Motorstrom und Motorspannung (UPhase) wird ebenfalls ermittelt. Über eine Messbrücke wird das Drehmoment (U<sub>Drehmoment</sub>) bestimmt. Diese analogen Werte werden vom AD-Wandler gemessen und für eine Reglerplattform bereitgestellt. Die Reglerplattform kann über die Ansteuerung eines Relais die Drehrichtung des Motors verändern. Über den Encoder wird der gedrehte Winkel des Motors bestimmt. Eine detaillierte Beschreibung Signalkonditionierung auf der Platine befindet sich in [1]. Der AD- und der DA-Wandler sowie die Messbrücke werden im Rahmen dieser Arbeit verwendet. wurden jedoch in der Vorarbeit nicht in Betrieb genommen. Die Messung der Effektivwerte und der Phasenlage wird nicht benötigt.

**Abbildung 1.1:** Signalverlauf zur Ansteuerung des Piezomotors auf der SiKo-Platine [1]

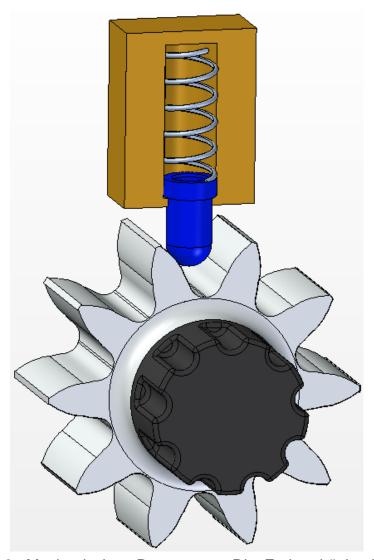

Eine mögliche Anwendung für die SiKo-Platine und den Einsatz eines Piezomotors im Zusammenhang mit einem FPGA als Reglerplattform ist die Realisierung einer virtuellen Rasterung. In Abbildung 1.2 ist der Aufbau einer mechanischen Rasterung abgebildet. Wenn der Drehknopf am Zahnrad gedreht wird, steigt das Drehmoment an, weil die Feder zusammengedrückt wird und eine höhere Kraft benötigt wird, um weiterzudrehen. Sobald die Spitze eines Zahnes überschritten wird, springt der Stift wieder in die Lücke. Falls die Spitze noch nicht überschritten wurde und der Drehknopf losgelassen wird, springt der Drehknopf wieder in die letzte Rasterposition zurück. Der Nachteil dieser mechanischen Rasterung ist die fest vorgegebene Anzahl der Rastpunkte. Für eine Änderung der Anzahl der Rastpunkte bzw. ein anderes Drehmoment, müssen die mechanischen Bauteile gewechselt werden.

**Abbildung 1.2:** Mechanisches Rastsystem. Die Feder drückt den Stift nach unten. Beim Drehen wird der Stift hochgedrückt und das Drehmoment steigt. Nach Überschreiten der Spitze eines Zahnrads springt der Stift in die nächste Rasterung. Wenn der Drehknopf vorher losgelassen wird, dreht sich der Drehknopf zurück und der Stift springt in die letzte Rasterung.

Piezomotoren eignen sich für die eingebettete Realisierung aktorischer Systeme mit integrierter Ansteuerungselektronik. Sie besitzen einen kompakten Aufbau (Werte für den in der Arbeit verwendeten Piezomotor U-164.11 von Physikinstrumente GmbH & Co. KG 44 x 24 x 9 mm) und bieten hohe Werte für Beschleunigung (bis zu 5 g), Geschwindigkeit (500 mm/s) und Präzision (kleinste Schrittweite 0,05 μm) [2]. Ein weiterer Vorteil für einen kompakten Aufbau mit einer Ansteuerelektronik ergibt sich aus der Wirkweise des Piezomotors. Der Piezomotor erzeugt keine elektromagnetischen Felder und wird von diesen auch nicht beeinflusst [3].

Als Reglerplattform bietet sich der Einsatz eines FPGAs an. Neben der reinen Berechnung lassen sich bei FPGAs die Ansteuerung der Sensorik und Aktorik gut parallelisieren.

Der Bericht gliedert sich wie folgt: Kapitel 1 bildet die Einleitung mit einer Motivation und der Vorstellung bisher erstellter Platinen. In Kapitel 2 wird die Aufgabenstellung detailliert beschrieben. Dazu gehören die konkreten Anforderungen sowie die Rahmenbedingungen für die zu entwerfende Platine. Ferner werden die zu implementierenden VHDL-Module erläutert. Kapitel 3 behandelt eine Literaturrecherche, in der verwandte Arbeiten vorgestellt werden, in denen FPGAs zur Ansteuerung von Piezomotoren verwendet werden. Kapitel 4 befasst sich ausführlich mit dem Aufbau der Platine. Dabei auf Besonderheiten beim Platinenentwurf eingegangen und Verschaltung der einzelnen Komponenten erläutert. In Kapitel 5 werden die einzelnen Module und die Implementierung der Zielanwendungen beschrieben. Kapitel 6 befasst sich mit der Inbetriebnahme der verwendeten Platinen und den Ergebnissen der Arbeit, die anschließend diskutiert werden. Es wird u. a. erläutert, wieso eine Implementierung zur Regelung eines Drehmoments mit diesem Piezomotor nicht möglich war. Abschließend gibt eine Zusammenfassung und einen Ausblick in Kapitel 7.

## 2 Klärung der Aufgabenstellung

In diesem Kapitel wird die Aufgabenstellung detailliert beschrieben. Dabei wird eine Gesamtübersicht über die verwendeten Geräte gegeben und die Funktion der bereits vorhandenen analogen Platinen erläutert. Außerdem werden die Rahmenbedingungen für die zu entwerfende Platine genannt.

Die Aufgabenstellung gliedert sich in zwei Abschnitte. Ziel des ersten Teils ist der Entwurf, die Realisierung und die Evaluation einer gedruckten Schaltung, welche einen Xilinx Spartan- 6 FPGA für den Einsatz als Reglerplattform (im Folgenden HACON-Platine genannt) bereitstellt. Der zweite Teil befasst sich mit der Implementierung von Hardware-Modulen für das FPGA, die die analogen Platinen ansteuern.

## 2.1 PCB-Entwurf einer FPGA-basierten Reglerplattform

Konkrete Anforderungen an den Entwurf der HACON-Platine ergeben sich aus zwei Anwendungen, der CONBOX-Platine und der SiKo-Platine.

#### **2.1.1 CONBOX**

Die CONBOX-Platine wurde in früheren Arbeiten mit einem TMS320F28335 eZdsp Starter Kit als Reglerplattform betrieben. Das Starter Kit enthält ein DSP. Die zu entwerfende HACON-Platine muss diese Reglerplattform ersetzen. Dazu muss sie auf die CONBOX-Platine aufsteckbar sein. Die Steckverbinder der beiden Platinen müssen sich deshalb auf derselben Position befinden. Die Pinbelegung der gemeinsam verwendeten Steckverbinder ist vorgegeben. Durch die Position der Steckverbinder sind ebenfalls die minimalen Abmessungen der zu entwerfenden HACON-Platine vorgegeben.

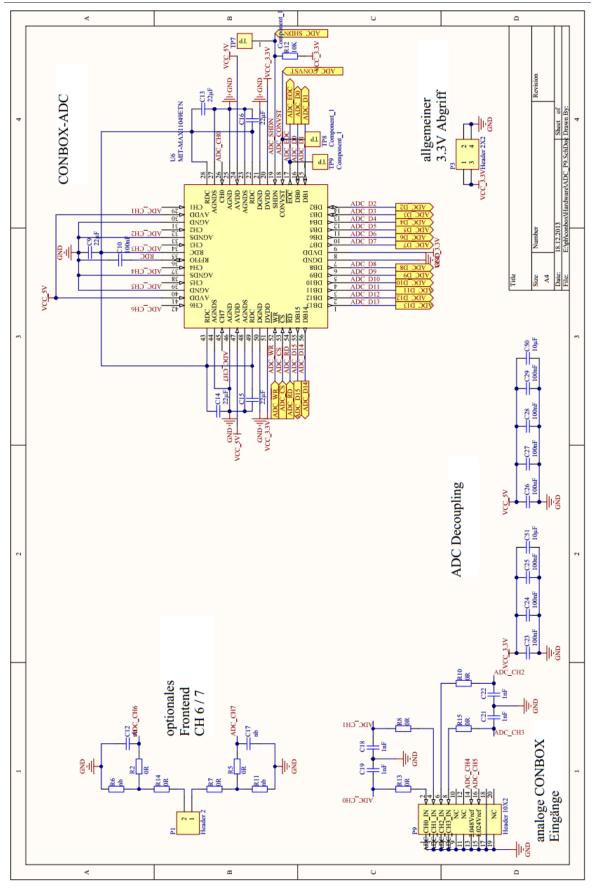

Des Weiteren muss die zu entwerfende HACON-Platine alle Aufgaben des Starter Kits übernehmen. Der DSP auf dem Starter Kit enthält einen internen AD-Wandler. Da das FPGA keinen internen AD-Wandler besitzt, ist ein externer AD-Wandler notwendig.

#### 2.1.2 SiKo-Platine

Die SiKo-Platine wird verwendet um die Signale für eine Steuerung bzw. Regelung des Piezomotors zu konditionieren und für eine Reglerplattform bereitzustellen. Sie wird mit einem 40 pin Flachbandkabel mit der zu entwerfenden HACON-Platine verbunden. Die Position des Steckverbinders ist frei wählbar.

Eine Inbetriebnahme des DA- und AD-Wandlers ist zu erfolgen, ebenso ist die Messbrücke zur Ermittlung des Drehmoments in Betrieb zu nehmen.

Um mit der SiKo-Platine eine Anwendung zu entwickeln, die einen Piezomotor ansteuert, sind folgende Komponenten vorgegeben:

Der Piezomotor (Physikinstrumente GmbH, U-164.11) und der zugehörige Piezoverstärker LE 150/100 EBW von Piezomechanik GmbH, ein Encoder zur Drehwinkelerfassung (HEDS-5600 von Avago Technologies) sowie eine Hysteresebremse zur künstlichen Erzeugung eines Drehzahlunabhängigen Drehmoments am Piezomotor (HB-10M-2DS von mobac).

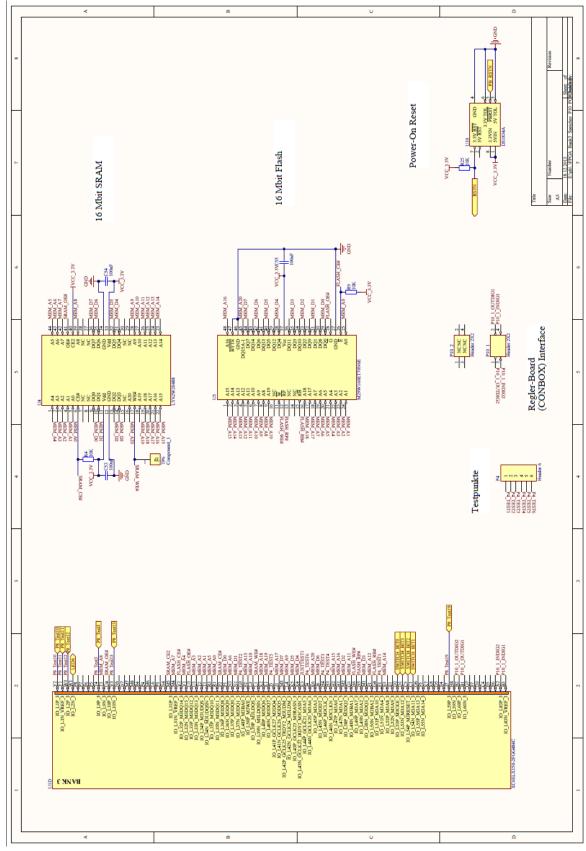

Die Auswahl der zu verwendenden Komponenten für die HACON-Platine war nicht Teil der Aufgabenstellung. Folgende Komponenten wurden in der Aufgabenstellung vorgegeben:

- XC6SLX150-3FGG484C (FPGA),

- CP2102-GM (USB-UART-bridge),

- M25P64-VMF6P (64 Mbit Konfigurationsspeicher),

- BS62LV1600EIP55 (16 Mbit SRAM), ersetzt durch LY62W20488ML-55LLI,

- M29W160ET70N6E (16 Mbit Flash),

- LTC6905CS5-133 (Oszillator),

- LM2853MH-3.3, LM2853MH-1.2 (Spannungswandler),

- MAX11049ETN+ (AD-Wandler) und

- DS1834AS+ (Voltage Monitor).

Der vorgegebene SRAM-Speicher war beim Distributor nicht mehr verfügbar und wurde durch einen gleichartigen Speicher ersetzt.

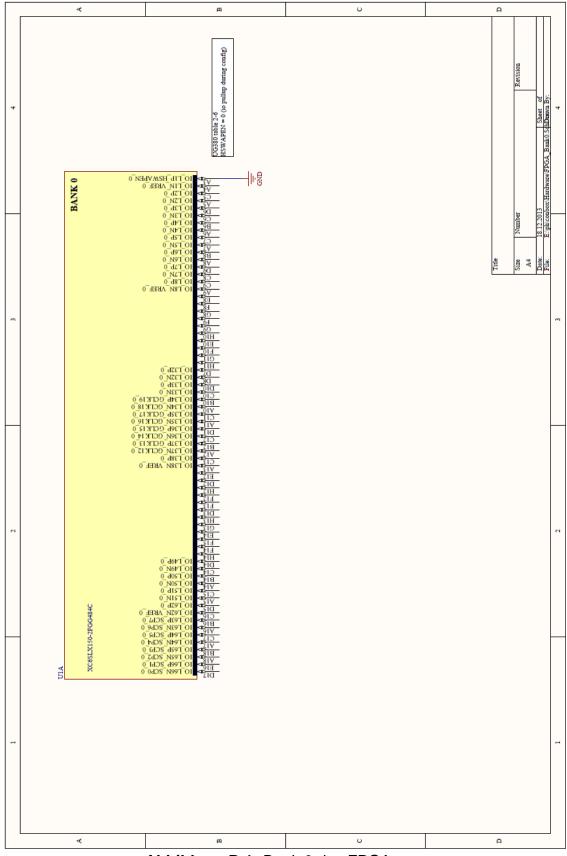

Die Pins des FPGA sind auf vier Bänke verteilt. Es sollen möglichst wenige Bänke verwendet werden. Durch das Abschalten einer unbenutzten Bank wird der Stromverbrauch gesenkt.

Das FPGA gibt es in diversen Varianten, die sich in der Anzahl der verfügbaren Speicher- und Logikeinheiten sowie der verwendbaren Pins unterscheiden. Aus diesem Grund gibt es bei der Verdrahtung die Forderung lediglich die Pins zu verwenden, die ebenfalls in der kostengünstigsten Variante (XC6SLX25) vorhanden sind.

Die HACON-Platine wird mit dem CAD-Programm Altium Designer entworfen. Eine Einarbeitung in die umfangreichen Funktionen der Software ist notwendig.

Mit der Software werden Schaltpläne und die dazugehörige Platine entworfen. Die Software ist besonders gut geeignet für den Platinenentwurf mit mehr als zwei Lagen. Das Routen von Leiterbahnen sowie die Bearbeitung von vielen parallelen Leiterbahnen wird unterstützt.

Die Fertigung und Bestückung der HACON-Platine erfolgt durch den kommerziellen Anbieter PCB-Pool. Dessen Vorgaben (design rules) sind einzuhalten.

## 2.2 Hardware-Beschreibung der Regleranwendungen

Das FPGA auf der zu entwerfenden HACON-Platine wird in der Hardwarebeschreibungssprache VHDL programmiert. Eine Einarbeitung in diese Programmiersprache sowie in die Entwicklungsumgebung Xilinx ISE V14.6 ist notwendig.

#### 2.2.1 Testmodule für CONBOX

Um die Funktionsfähigkeit und Verbindung der CONBOX mit der zu entwerfenden HACON-Platine zu testen, soll ein Testmodul entwickelt werden. Das Testmodul soll den AD-Wandler auf der HACON-Platine ansteuern und einen AD-Kanal abtasten. Das Ergebnis dieser Wandlung soll per UART und als analoges Signal wieder ausgegeben werden. Um das analoge Signal zu realisieren, wird der gemessene Wert über eine PWM ausgegeben. In der CONBOX wird daraus über einen Tiefpassfilter ein analoges Signal generiert.

#### 2.2.2 Haptisches Feedback per Piezomotor

Für die Realisierung eines haptischen Feedbacks ist eine Drehwinkelabhängige Drehmomentregelung für einen Piezomotor auf dem FPGA zu implementieren. Als Anwendung soll eine Rasterung, wie in Abbildung 1.2 dargestellt, simuliert werden. Der Piezomotor soll derart angesteuert werden, dass sich das Drehmoment in Abhängigkeit des gedrehten Winkels erhöht.

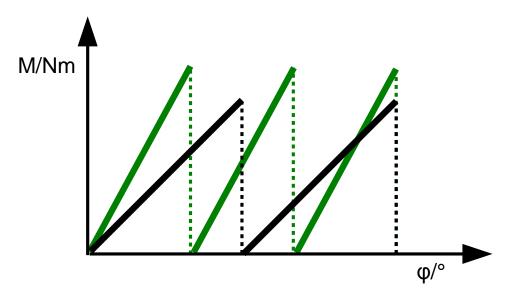

Der AD-Wandler soll angesteuert werden, um die proportional zum Drehmoment ausgegebene Spannung zu messen. Die Signale des Encoders sind für die Bestimmung des Drehwinkels auszuwerten. Diese Informationen werden benötigt, um eine Drehmomentregelung zu implementieren. Dabei soll die Drehwinkel-Drehmoment-Charakteristik zur Laufzeit veränderbar sein, d. h. das entstehende Drehmoment sowie die Anzahl der Rastschritte sollen im Betrieb verändert werden können. In Abbildung 2.1 sind beispielhaft zwei Charakteristiken einer drehwinkelabhängigen Drehmomentregelung dargestellt.

Die schwarzen Linien zeigen eine grobe Rasterung und ein geringeres maximales Drehmoment, die grünen Linien zeigen eine feinere Rasterung und ein höheres maximales Drehmoment. Diese Verläufe simulieren die Rasterung mit einem Zahnrad, das auf einer Seite einen Anstieg hat und auf der anderen Seite steil abfällt. Nach Überschreiten der Spitze des Zahnrads, springt der Stift unverzüglich in den nächsten Rastpunkt.

**Abbildung 2.1:** Zwei mögliche Charakteristiken mit verschieden feinen Rasterungen und verschiedenen maximalen Drehmomenten

## 3 Verwandte Arbeiten

Dieses Kapitel gibt einen Überblick über Arbeiten, in denen eine Drehmomentbzw. Drehzahlregelung für Piezomotoren entwickelt wurde bei denen FPGAs als Reglerplattform zum Einsatz kommen. Eine Vielzahl an Arbeiten beschäftigt sich mit einer Positionsregelung, da in der Industrie ein großer Bedarf danach besteht.

Da sich Eigenschaften wie beispielsweise die optimale Anregungsfrequenz bei Piezomotoren im Laufe der Zeit durch reibungsbedingte Abnutzung verändern, wird in [4] eine Regelung der Läuferposition mit einem neuronalen Netz in einem FPGA implementiert. Das neuronale Netz nimmt Veränderungen wahr und ändert die Regel- und Ansteuerungsparameter. Allerdings ist das Ziel der vorliegenden Arbeit nicht die Adaption langfristiger variierender Betriebsparameter. Ein neuronales Netz wird daher nicht implementiert.

In [5] wird ein FPGA zur Signalerzeugung und Regelung der Geschwindigkeit verwendet. Das FPGA befindet sich auf einem Entwicklungsboard. Ziel der vorliegenden Arbeit ist allerdings die Entwicklung einer Platine mit einem FPGA als Reglerplattform, die die bereits vorhandenen analogen Platinen ansteuern kann. Da die Belegung der Steckverbinder und teilweise sogar die Position fest vorgegeben ist, kann das Entwicklungsboard nicht verwendet werden.

Die Ansteuerung eines Roboterarms mit mehreren Piezomotoren wird in [6] beschrieben. Dazu werden u. a. ein PC und ein Control Board verwendet. Auf dem Control Board befinden sich u. a. ein FPGA und ein Mikrocontroller. Am PC können die Vorgaben über LabView zum Controller Board gesendet werden. Die Vorgaben werden vom Mikrocontroller empfangen. Die Regelung wird ebenfalls mit dem Mikrocontroller durchgeführt. Die Berechneten Stellgrößen werden an das FPGA übergeben. Das FPGA wird lediglich dafür verwendet, um die einzelnen Piezomotoren über einen "High Speed Serial Databus" anzusteuern.

In [7] wird die Ansteuerung eines Piezoaktors mit mehreren Freiheitsgraden erläutert. Für die Signalsynthese wird ein FPGA verwendet. Im FPGA ist ein Array von DDSs (Direct Digital Synthesizer) implementiert. Die einzelnen DDSs arbeiten unabhängig voneinander. Die Amplitude und die Frequenz können für alle Bewegungsrichtungen separat eingestellt werden. Allerdings wird in der vorliegenden Arbeit ein Piezomotor verwendet, der lediglich einen Freiheitsgrad besitzt. Aufgrund der begrenzten Bandbreite des Piezoverstärkers von 70 kHz

wird keine DDS benötigt. Außerdem ist das Ziel der Arbeit die Implementierung einer Regelung und nicht einer Steuerung.

## 4 Aufbau der Leiterplatte

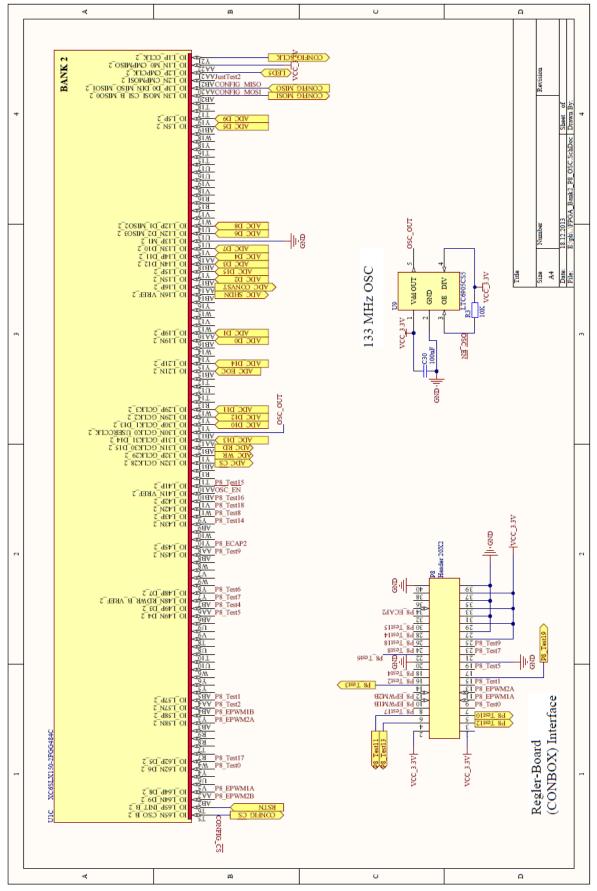

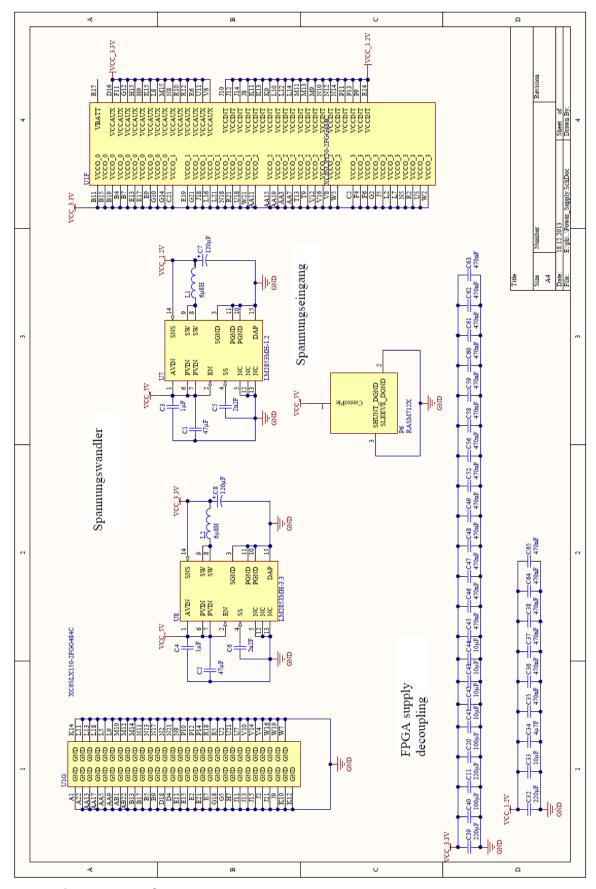

In diesem Kapitel wird der Aufbau der HACON-Platine beschrieben. Diese umfasst das FPGA, die Spannungsversorgung, einen AD-Wandler, diverse Speicher sowie den Oszillator und weitere periphere Komponenten wie LEDs, Steckverbinder und Schalter. Die Schaltpläne und das Layout befinden sich in Anhang B.

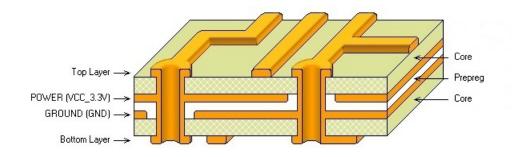

Die Leiterplatte ist vierlagig. Innen befinden sich die beiden Versorgungslagen mit dem Groundpotential und der Versorgungsspannung von 3,3 V. Auf den beiden äußeren Lagen liegen die Signalleitungen. Die Anordnung der Lagen ist in Abbildung 4.1 visualisiert.

**Abbildung 4.1:** Anordnung der Lagen der vierlagigen HACON-Platine. In der Mitte sind die beiden Versorgungslagen 3,3 V und Ground. Außen befinden sich die Signalleitungen. [8]

### 4.1 FPGA

Das verwendete FPGA ist das XC6SLX150 der Spartan-6-Familie von Xilinx. Das FPGA besitzt 484 Pins mit einem 1 mm-Raster in einem BGA-Gehäuse [9]. Die Pins der Bank 0 bleiben vollständig unbeschaltet.

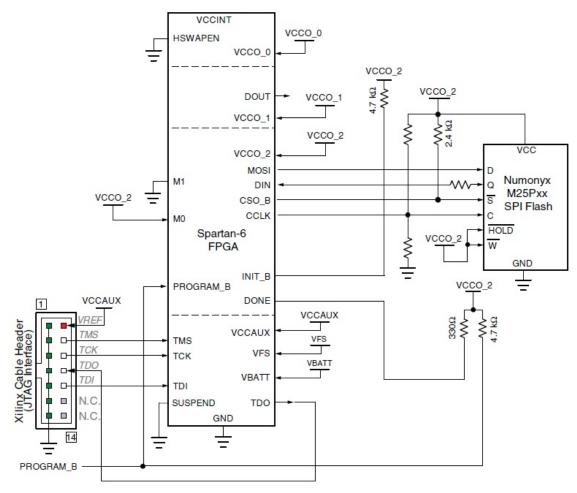

Das FPGA ist CCL-basiert (CMOS configurable latch). Es muss daher nach jedem Ausschalten neu konfiguriert werden. Als Konfigurationsmodus wurde der "Master Serial/SPI configuration mode" gewählt. In diesem Modus werden die Konfigurationsdaten nach jedem Einschalten aus einem Konfigurationsspeicher ausgelesen. Als Konfigurationsspeicher wurde der in [9] empfohlene M25P64-VMF6P von Micron [10] gewählt. Um diesen Modus auszuwählen, muss der Pin M0 an die Versorgungsspannung und der Pin M1 an das Groundpotential angeschlossen werden.

Der Konfigurationsspeicher wurde wie in Abbildung 4.2 zu sehen verschaltet. Die Pins VBATT und DOUT bleiben unbeschaltet. Die Pins VFS und RFUSE sind mit Testpunkten verbunden, um Zugriff auf die Pins zu haben.

**Abbildung 4.2:** Verschaltung für die Konfiguration im "Master Serial/SPI configuration mode" [9]

Widerstand zwischen dem Pin DIN des FPGA Der und Q Konfigurationsspeicher beträgt 0 Ω. An dieser Stelle ist ein Widerstand vorgesehen, um mögliche Überschwinger bei Flankenanstiegen bzw. um Reflexionen zu vermeiden. Vorsichtshalber wurden auch zwischen die Pins MOSI und D, CS0 B und  $\bar{S}$  sowie zwischen CCLK und C 0  $\Omega$ -Widerstände eingefügt. Der Pulldown- bzw. Pullupwiderstand in der Leitung zwischen CCLK und C beträgt nach [9] 100 Ω. Die Pins HSWAPEN, TMS, TCK, TDI, TDO, SUSPEND und DONE sind wie oben zu sehen beschaltet.

Die Anschlüsse für die Versorgungsspannungen (VCCO\_0, VCCO\_1, VCCO\_2, VCCO\_3 und VCCAUX) sind alle mit der Versorgungsspannung 3,3 V verbunden.

Der Pin PROGRAM\_B ist mit einem Taster verbunden. Durch Drücken des Tasters wird dieser Pin mit dem Groundpotential verbunden. Sobald an dem Pin für mindestens 500 ns ein Low-Pegel und anschließend wieder einen High-Pegel anliegt, werden die Konfigurationsdaten erneut aus dem Konfigurationsspeicher ausgelesen.

INIT\_B wurde mit dem Voltage Monitor verbunden (siehe Kapitel 4.6).

## 4.2 Spannungsversorgung

Die Spannungsversorgung der Platine erfolgt über ein 5 V-Netzteil, das bis zu 4 A [11] bereitstellt. Über die HACON-Platine werden ebenfalls die angeschlossenen Platinen (CONBOX, SiKo-Platine) versorgt.

### 4.2.1 Spannungswandler

### a) Verschaltung

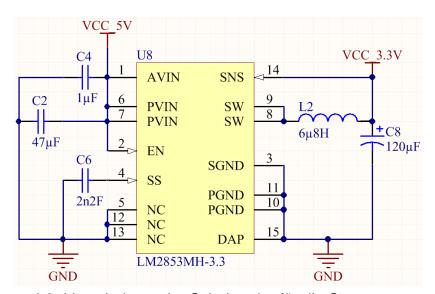

Das FPGA benötigt zwei Versorgungsspannungen. Für die I/O-Bänke werden 3,3 V benötigt, für den Prozessorkern 1,2 V. Um die verschiedenen Spannungen zu realisieren, werden die Schaltregler LM2853MH-1.2 und LM2853MH-3.3 von Texas Instruments eingesetzt, die als Stepdown-Wandler arbeiten. Stepdown-Wandler wandeln die Spannung von einer höheren in eine tiefere Spannung herunter.

In Abbildung 4.3 ist die Verschaltung eines Stepdown-Wandlers für die Konvertierung von 5 V in 3,3 V veranschaulicht. Die Verschaltung für die Erzeugung von 1,2 V ist identisch aufgebaut.

Abbildung 4.3: Verschaltung der Schaltregler für die Spannungsversorgung

Die Eingangspins (1, 6 und 7) sind mit zwei Kondensatoren verbunden (C2 und C4). Als Stützkondensator für den Spannungseingang (C2) wird ein 47 µF Keramikkondensator gewählt. Dadurch wird eine konstante Eingangsspannung garantiert. Ein hierzu parallel verschalteter 1 uF-Kondensator glättet die hochfrequenten Lastspitzen der digitalen Komponenten.

Der Kondensator C6 erzeugt einen "Soft-Start". Damit wird die endgültige Spannung um einige Mikrosekunden verzögert erreicht. Die Dimensionierung der Spule (L2) und des Ausgangskondensators(C8) wurde dem Datenblatt [12] entnommen.

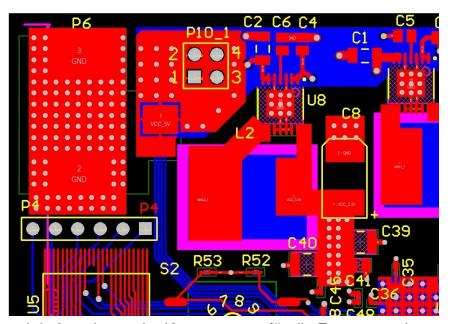

#### b) Layout

Der Stepdown-Wandler ist ein Regelkreis. Aus diesem Grund ist darauf zu achten, die Leiterbahnen möglichst kurz zu halten, um einen Spannungseinbruch möglichst schnell ausregeln zu können. In Abbildung 4.4 ist die Anordnung der einzelnen Komponenten zu sehen. Die Spule (L2) muss mit ihren beiden Anschlüssen möglichst nah an die Pins 8 und 9 ("SW", Switch) und Pin 14 ("SNS", Sense) des Spannungsreglers (U8). Der Ausgangskondensator (C8) muss möglichst nah an die Spule platziert werden.

**Abbildung 4.4:** Anordnung der Komponenten für die Erzeugung der Versorgungsspannung

Die Spulen erzeugen ein Magnetfeld. Um das Induzieren von Strömen und Störungen zu verhindern, wird unter die Spulen auf der Unterseite und in den Versorgungslagen eine Sperrfläche gelegt. Damit können dort keine Leitungen verlegt werden.

### 4.2.2 Entkoppelung des FPGAs

Um eine konstante Spannungsversorgung zu garantieren, werden Entkoppelkondensatoren eingesetzt. Diese dienen dazu bei hochfrequenten Schaltvorgängen von ICs sofort ausreichend Energie bereitzustellen und damit von der Spannungsversorgung der anderen Komponenten zu entkoppeln bzw. andere ICs nicht zu beeinflussen.

Bei FPGAs mit hohen Schaltfrequenzen ist dies besonders wichtig. Deshalb wird die Anzahl der zu verwendenden Kondensatoren vom Hersteller empfohlen. In Tabelle 4.1 stehen die vom Hersteller empfohlenen und die verwendeten Werte und Mengen [13].

| Anschluss\ Kondensator(Bauform)                  | 100 μF   | (1206)     | 4,7 μF   | (0805)    | 470 nF (  | 0402)     |

|--------------------------------------------------|----------|------------|----------|-----------|-----------|-----------|

|                                                  | empf.    | verw.      | empf.    | verw.     | empf.     | verw.     |

| V (4.2.V)                                        |          |            |          | 1x10 µF + |           |           |

| V <sub>ccint</sub> (1,2 V)                       | 2x100 μF | 1x220 μF   | 3x4,7 μF | 1x4,7 μF  | 6x470 nF  | 6x470 nF  |

| V - V (3.3.V)                                    |          | 2x220 µF + |          |           |           |           |

| V <sub>ccaux</sub> + V <sub>Banken</sub> (3,3 V) | 5x100 μF | 2x100 µF   | 6x4,7 μF | 4x10 μF   | 15x470 nF | 13x470 nF |

**Tabelle 4.1:** Übersicht über die benötigten und verwendeten Stütz- bzw. Entkoppelungskondensatoren

Die großen Kondensatoren (100  $\mu$ F bzw. 220  $\mu$ F) werden als Stützkondensatoren verwendet. Die kleineren Kondensatoren werden benötigt, um die Stromversorgung bei hochfrequenten Schaltvorgängen zu garantieren. Laut Datenblatt [13] dürfen zwei 100  $\mu$ F- zu einem 220  $\mu$ F- bzw. zwei 4,7  $\mu$ F- zu einem 10  $\mu$ F-Kondensator zusammengefasst werden. Bei den 470 nF- Kondensatoren wurden lediglich 13 Kondensatoren verwendet, weil Bank 0 nicht beschaltet ist.

#### 4.3 AD-Wandler

Um analoge Signale zu digitalisieren, wird der AD-Wandler MAX11049 von Maxim Integrated verwendet. Der AD-Wandler hat eine Auflösung von 16 Bit und besitzt acht separate Eingänge für analoge Signale [14].

#### a) Verschaltung

In der Konfiguration auf der HACON-Platine verwendet der AD-Wandler die interne Referenzspannung. Aus diesem Grund wird an den Pin REFIO ein 100 nF-Kondensator angebracht.

Die RDC-Pins werden alle miteinander verbunden. Laut Datenblatt sollen die RDC-Pins mit Bypass-Kondensatoren verbunden werden, die insgesamt eine minimale Kapazität von 80 µF haben [14]. Für die fünf RDC-Pins wurde jeweils ein 22 µF-Kondensator verwendet.

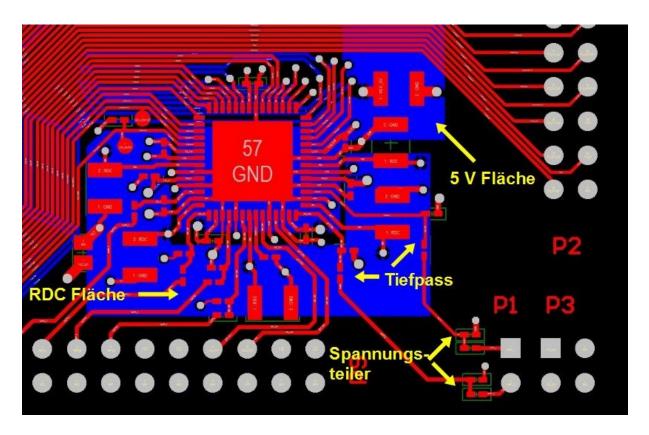

An die Spannungsversorgungseingänge wird jeweils ein 100 nF Entkoppelkondensator angebracht sowie ein Stützkondensator mit 10  $\mu$ F. Zwischen analogem und digitalem Ground wird nicht unterschieden. Die beiden Potentiale werden verbunden.

Sechs der acht Kanäle sind reserviert für analoge Leitungen der CONBOX-Platine. Zwei dieser Leitungen dienen als Referenzspannungen auf der CONBOX-Platine. Diese Signale werden direkt an den AD-Wandler angeschlossen. Die vier anderen Signale werden über einen Tiefpass an den AD-Wandler geleitet. Der Widerstand beträgt 0 Ohm. Der Kondensator hat auf Grund der minimalen Abtastrate den im Datenblatt empfohlenen Wert von 1 nF. Die beiden verbliebenen Kanäle werden zu Testzwecken mit einem Steckverbinder verbunden. Die angelegten Spannungen können nach dem Tausch der Widerstände des Spannungsteilers in den messbaren Bereich des AD-Wandlers verringert werden. Anschließend gibt es noch die Möglichkeit die Spannung über einen Tiefpass zu führen.

Der AD-Wandler wird im Rahmen der Arbeit zur Ansteuerung des Piezomotors nicht verwendet.

### b) Layout

Das RDC-Potential gilt als Referenzspannung. Das Signal muss deshalb stabil sein. Um das zu erreichen, wird für die Spannung eine eigene Fläche eingefügt, die mit den Kondensatoren verbunden ist. Abbildung 4.5 zeigt die Anordnung des AD-Wandlers, der Tiefpässe sowie der RDC-Fläche.

Die Leitungen der analogen Signale werden kurz gehalten und die Tiefpässe nah an den AD-Wandler angebracht. Damit wird eine mögliche Störung auf den Leitungen minimiert.

Abbildung 4.5: Anordnung der Komponenten für die AD-Wandlung

## 4.4 Speicher

Auf der Platine befinden sich außer dem Speicher für die Konfigurationsdaten zwei weitere Speicher, ein CMOS SRAM mit flüchtigem Speicher sowie ein persistenter Flash-Speicher.

Um die Routing-Komplexität gering zu halten, teilen sich die beiden Speicher die Adress- und Datenleitungen. Die Auswahl des aktiven Speichers erfolgt über separate Steuersignale. Für die Datenzugriffsgranularität von 8 Bit wurde der "Byte" Pin des Flash-Speichers mit dem Groundpotential verbunden [15].

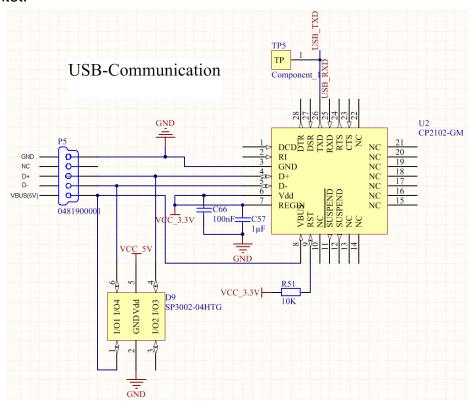

### 4.5 USB

Um eine Kommunikation zwischen FPGA und einem PC herzustellen, wird der USB zu UART Wandler CP2102 von Silicon Labs verwendet. Die Verschaltung ist Abbildung 4.6 zu entnehmen. Der Wandler wird im Self-Powered Mode betrieben. Dazu wird der Pin VBUS mit dem entsprechenden Signal des USB-Steckverbinders verbunden [16]. An die Pins Vdd und REGIN wird die Betriebsspannung 3,3 V angeschlossen. Die Datenleitungen D+ und D- sowie GND werden ebenfalls an die entsprechenden Pins des USB-Steckverbinders

angeschlossen. Der Pin RST wird über einen Pullup-Widerstand an die Betriebsspannung angeschlossen. Auf einen FPGA gesteuerten Reset wird verzichtet.

Abbildung 4.6: Verschaltung des USB zu UART Wandlers

Um den Wandler vor zu hoher Spannungen zu schützen, wird eine ESD-Schutzdiode eingesetzt. Diese Diode leitet den Strom bei einer zu hohen Spannung an die 5 V-Leitung weiter.

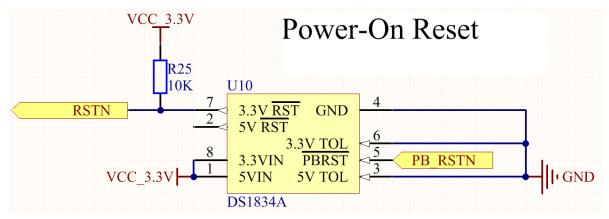

## 4.6 Voltage Monitor / Power on Reset

Der Voltage-Monitor realisiert einen Power-On-Reset. Er erzeugt folglich nach dem Anlegen der Versorgungsspannung oder dem aktivieren seines PBRST# Eingangs ein RST# Signal, das noch etwa 350ms auf 0 bleibt und danach automatisch auf 1 geht [17]. Das wird für zwei Sachen verwendet. Bei der Konfiguration nach einem Power-Cycling wird über INIT B = RST# sichergestellt, dass der Konfigurationsspeicher bereits eine stabile Versorgungsspannung hat, bevor das FPGA die Konfigurationsdaten ausliest. Während der Laufzeit (nach der Konfiguration) führt das Betätigen des RESET Tasters dazu, dass der RESET# Eingang des FPGAs für 350ms auf 0 gehalten wird. In diesem Fall wird der Voltage Monitor zum Entprellen des Tasters verwendet.

Abbildung 4.7: Verschaltung des Voltage Monitors

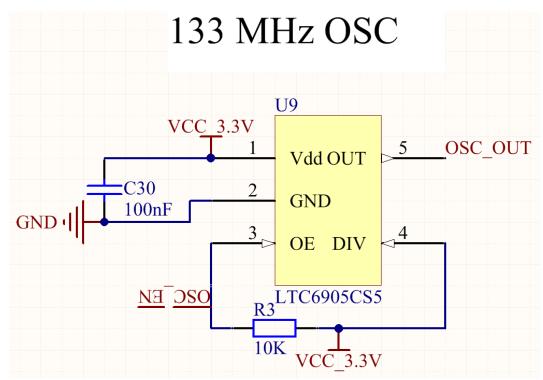

#### 4.7 Oszillator

### a) Verschaltung

Als Taktgenerator für das FPGA wird der Oszillator LTC6905CS5-133 von Linear Technology verwendet. Die Verschaltung ist Abbildung 4.8 zu entnehmen. An die Versorgungseingänge wird ein Bypass-Kondensator angebracht. Der Pin OE wird über einen Pullup-Widerstand mit der Betriebsspannung verbunden. Außerdem wird der Pin an das FPGA angeschlossen. Damit kann der Oszillator, beispielsweise in einem Ruhemodus, ausgeschaltet werden.

Um die höchstmögliche Frequenz von 133 MHz verwenden zu können, wurde der Pin "DIV" auf der HACON-Platine mit der Betriebsspannung verbunden [18]. Der Ausgang des Oszillators wird mit einem "GCLK"-Pin verbunden. Diese Eingänge sind globale Takteingänge und verteilen das Taktsignal mit möglichst geringem Aufwand an alle benötigten Stellen.

Abbildung 4.8: Verschaltung des Oszillators

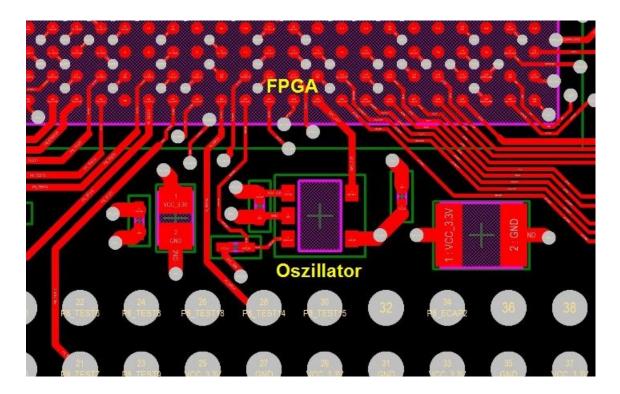

### b) Layout

In Abbildung 4.9 sind der Oszillator und das FPGA zu sehen. Die Leitung zwischen FPGA und Oszillator ist möglichst kurz zu wählen. Die Ausgänge von ICs haben sehr kurze Anstiegs- und Fallzeiten. Um Reflexionen auf den Datenleitungen zu vermeiden, darf die Leitungslänge eine kritische Länge nicht überschreiten. Für Rechteckimpulse gilt als Faustregel, dass eine Leitung als "lang" gilt, wenn die einfache Laufzeit über die Leitung größer als die Hälfte der minimalen Anstiegszeit t<sub>rise</sub> der Signale ist [19].

Die Ausbreitungsgeschwindigkeit auf den Leiterbahnen der Platine beträgt mit der Lichtgeschwindigkeit  $c_0 \approx 30$  cm/ns und der relativen Dielektrizitätskonstante des Platinensubstrats  $\epsilon_r = 5$  [19]

$$v = \frac{c_0}{\sqrt{\varepsilon_r}} = \frac{30cm/ns}{\sqrt{5}} = 13.4cm/ns. \tag{4.1}$$

Die Anstiegszeit des Oszillatorpins beträgt t<sub>rise</sub>=0,5 ns [18]. Somit ergibt sich mit obiger Faustregel eine kritische Länge von

$$l_{\text{krit}} = \frac{1}{2} \cdot t_{\text{rise}} \cdot v = \frac{1}{2} \cdot 0.5 \text{ ns} \cdot 13.4 \text{ cm/ns} = 3.35 \text{ cm}.$$

(4.2)

Die Leitung vom Oszillator zum FPGA hat eine Länge von ca. 4,5 mm. Sie liegt folglich deutlich unter der kritischen Länge.

Der Bypass-Kondensator ist ebenfalls möglichst nah an die Versorgungspins anzubringen.

**Abbildung 4.9:** Anordnung des Oszillators. Die Leiterbahn zwischen Oszillator und FPGA ist möglichst kurz zu wählen.

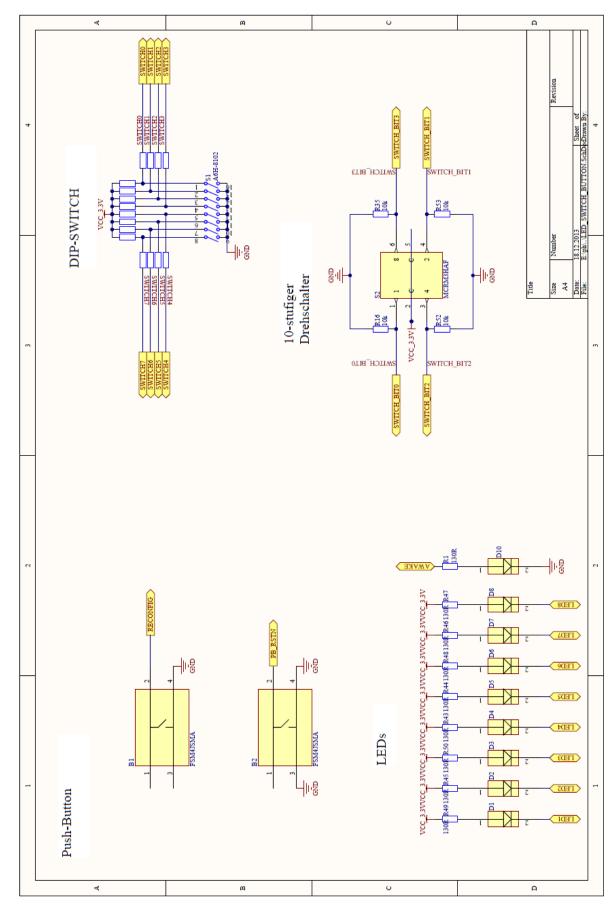

## 4.8 Steckverbinder, LEDs, Taster

#### a) Steckverbinder

Auf der Platine befinden sich Steckverbinder um verschiedene Funktionen zu erfüllen. Die Bezeichnung und die Funktion sind Tabelle 4.2 zu entnehmen. Die Pinbelegung der einzelnen Steckverbinder befindet sich im Anhang C.

Die CONBOX-Platine wird über die Steckverbinder P8, P9, P10\_1 und P10\_2 mit der HACON-Platine verbunden. Die Steckverbinder müssen sich auf beiden Platinen auf derselben Position befinden. An den Steckverbindern P8 und P10\_1 liegen digitale Signale an, die direkt mit dem FPGA verbunden werden. Der Steckverbinder P10\_2 dient als mechanische Stütze. Die Pins sind elektrisch nicht verbunden. An Steckverbinder P9 liegen analoge Signale an,

die mit dem AD-Wandler verbunden werden. Die genauen Steckverbinderpositionen befinden sich in Anhang C.

| Steckverbinder | Funktion                                   |

|----------------|--------------------------------------------|

| P1             | Analoge Eingänge für AD-Wandler            |

| P2             | Verbindung zur SiKo-Platine                |

|                | 3,3 V bzw. GND, als Referenzspannungen für |

| P3             | Potentiometer                              |

| P4             | Signalleitungen für Testzwecke mit FPGA    |

| P5             | USB Mini Buchse                            |

| P6             | Buchse für Versorgungsspannung             |

| P7             | Programmierheader                          |

| P8, P9, P10_1, | Verbindung zur CONBOX-Platine              |

| P10_2          |                                            |

Tabelle 4.2: Überblick und Funktion der Steckverbinder auf der HACON-Platine

#### b) LEDs

Zu Testzwecken wurden auf der Platine LEDs vorgesehen. Die verwendeten LEDs haben eine Durchlassspannung von 2 V. Als Vorwiderstand wird ein Widerstand mit 130  $\Omega$  gewählt. Somit ergibt sich folgender Strom:

$$I = \frac{U}{R} = \frac{3.3 \, V - 2 \, V}{130 \, \Omega} = 10 \, mA, \tag{4.3}$$

was der Hälfte des maximalen Durchlassstroms entspricht.

Die LEDs sind über die Kathode mit dem FPGA verbunden. Somit muss der Pin am FPGA einen High-Pegel haben, um die LED auszuschalten, und einen Low-Pegel, um die LED einzuschalten. Diese Konfiguration wurde gewählt, damit das FPGA nicht den gesamten Strom bereitstellen muss.

Eine Ausnahme bildet dabei LED D10. Sie ist mit dem Pin "AWAKE" verbunden. Dieser kann so eingestellt werden, dass er nach der Konfiguration einen High-Pegel hat und die LED somit einschaltet.

#### c) Schalter

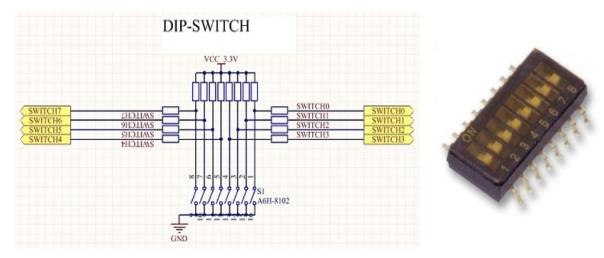

Für die Benutzerinteraktion zur Laufzeit, sind zwei Schalter auf der Platine vorgesehen. In Abbildung 4.10 ist die Verschaltung eines DIP-Schalters abgebildet. Bei offenem Schalter wird eine 1 von den FPGA Pins erkannt, bei geschlossenem eine 0. Die Längswiderstände dienen als zusätzlicher ESD-Schutz zu den Pullup-Widerständen.

Abbildung 4.10: Verschaltung und Abbildung eines DIP-Schalters [26]

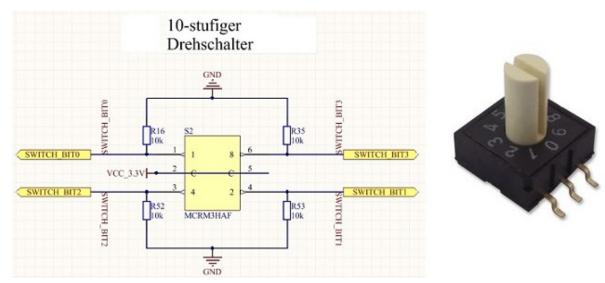

Der zweite Schalter ist ein zehnstufiger Drehschalter. In Abbildung 4.11 sind die Verschaltung sowie der Drehschalter abgebildet. An Pin zwei und fünf liegen 3,3 V an. Die restlichen vier Pins werden je nach Schalterstellung binär codiert und vom FPGA ausgewertet.

Abbildung 4.11: Verschaltung und Abbildung eines Drehschalters [27]

## 5 FPGA Hardware-Design

Die Hardware-Module wurden in der Hardwarebeschreibungssprache VHDL geschrieben. Für die Programmierung wurde die Entwicklungsumgebung Xilinx ISE V14.6 verwendet.

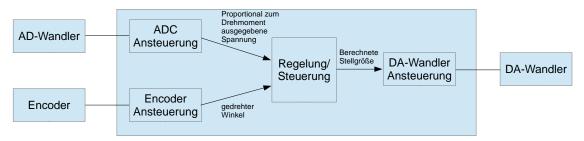

## 5.1 Haptisches Feedback

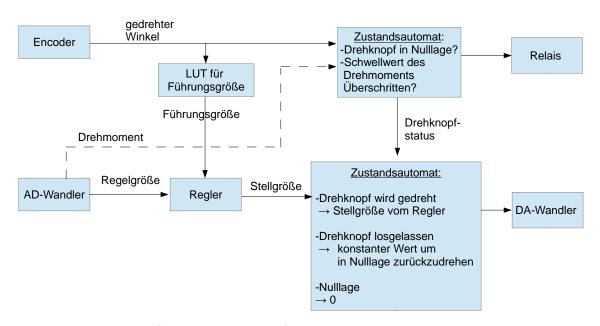

Abbildung 5.1 enthält eine Übersicht der VHDL-Module für die in den folgenden Unterkapiteln beschriebenen Steuerungen bzw. Regelungen. Der AD-Wandler misst eine proportional zum Drehmoment ausgegebene Spannung. Der Encoder ermittelt den gedrehten Winkel. Diese Informationen werden für die Regelung bzw. Steuerung benötigt. Diese berechnet die Stellgröße und übergibt diese an die Ansteuerung des DA-Wandlers.

**Abbildung 5.1:** Modulübersicht mit Schnittstellen zum AD-Wandler, Encoder und DA-Wandler

#### 5.1.1 Ansteuerung ADC

### a) Konfiguration des AD-Wandlers

Der AD-Wandler muss konfiguriert werden, da die Standardeinstellungen nicht den gewünschten Einstellungen entsprechen. Einige Einstellungen sind durch die Verschaltung des AD-Wandlers auf der SiKo-Platine vorgegeben sind. Der Ablauf der Konfiguration läuft folgendermaßen ab: Um die Konfiguration zu starten, wird das Reset Bit im Konfigurationsregister 1 gesetzt und wieder zurückgesetzt. Danach werden die Konfigurationsregister 0 und 1 beschrieben.

Der AD-Wandler wird so konfiguriert, dass die interne Referenzspannung gewählt wird und der AD-Wandler im "Continuous conversion mode" arbeitet. Ein im FPGA erzeugter Takt startet die Konvertierung. Der zu messende Kanal wird eingestellt. Zum Konfigurieren muss das Reset Bit auf "0" gesetzt werden. Das Triggerlevel wird auf "1" gesetzt. Dadurch wird ein Signal zum Auslesen der Daten sofort gesetzt, nachdem die konvertierten Daten verfügbar sind. Sobald eine Konvertierung beendet ist und die Daten ausgelesen werden können, wird

der AD-Wandler Pin DATA\_AV auf ,0' gesetzt. Der AD-Wandler Pin R/W wird zum Schreiben bzw. Lesen verwendet. Zum Schreiben wird eine ,0' angelegt, beim Lesen eine ,1'. Der AD-Wandler Pin  $\overline{\rm RD}$  wird abgeschaltet. Die Ausgabe der Daten im binären Format wird eingestellt.

Hierzu werden die beiden Konfigurationsregister mit den Werten "0000011000" und "0011000000" beschrieben.

### b) Schreibvorgang

Die Pins des FPGA, die die Daten des AD-Wandlers lesen bzw. ins Konfigurationsregister schreiben, sind als "inout" Pins deklariert. Sie können damit als Ein- und Ausgänge verwendet werden.

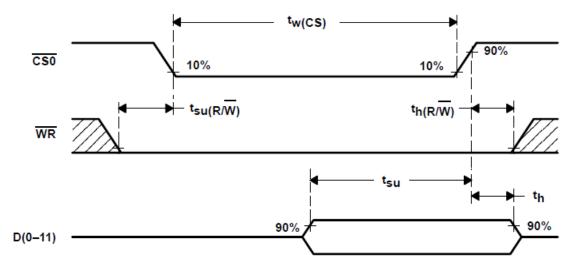

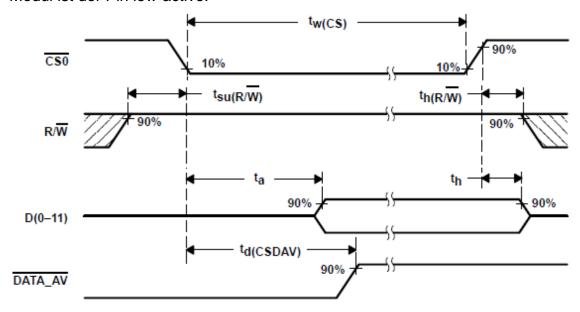

In Abbildung 5.2 ist der zeitliche Ablauf des Schreibvorgangs zum Konfigurieren des AD-Wandlers dargestellt. Der Ablauf erfolgt in einem Zustandsautomaten. Der Pin  $\overline{WR}$  ( $R/\overline{W}$ ) muss während des Schreibvorgangs auf ,0' gesetzt werden. Der Pin  $\overline{CSO}$  wird beim Start des Schreibvorgangs auf ,0' gesetzt. Danach werden die Daten an die Datenpins gelegt und im Anschluss wird der Pin  $\overline{CSO}$  wieder auf ,1' gesetzt. Diese Prozedur wird zum Konfigurieren vier Mal wiederholt. Die Wartezeiten  $t_{su(R/\overline{W})}$ ,  $t_h$ ,  $t_{su}$ ,  $t_{w(CS)}$  und  $t_{h(R/\overline{W})}$  werden realisiert, indem Wartezustände eingefügt werden. Bei Wartezeiten unter einer Taktdauer (7,519 ns) wird in den Wartezuständen lediglich der nächste Zustand aufgerufen. Bei Wartezeiten, die länger als einen Takt dauern, wird ein Zähler hochgezählt, bis die Wartezeit abgelaufen ist. Die Wartezeiten können [20] entnommen werden.

Abbildung 5.2: Ablauf des Schreibvorgangs [20]

### c) Lesevorgang

Während des Konfigurierens fungieren die Datenpins als Ausgänge. Um die Pins als Eingänge verwenden zu können, muss an die Pins der Wert ,Z' angelegt werden. Damit besitzen die Pins einen hohen Ausgangswiderstand und sind imstande die angelegte Spannung als High- oder Low-Pegel zu erfassen.

Der Lesevorgang und die Wartezeiten werden in einem Zustandsautomaten identisch zum Schreibvorgang realisiert. Beim Lesen wird lediglich der Pin  $\overline{WR}$  ( $R/\overline{W}$ ) auf ,1' gesetzt. In Abbildung 5.3 ist der zeitliche Ablauf dargestellt. Der Pin  $\overline{DATA\_AV}$  zeigt an, dass die Konvertierung fertiggestellt und die Daten bereitgestellt sind. In Abbildung 5.3 ist  $\overline{DATA\_AV}$  high-active. Im Hardware-Modul ist der Pin low-active.

Abbildung 5.3: Ablauf des Lesevorgangs [20]

Sobald am Pin DATA\_AV ein Übergang von ,1' auf ,0' festgestellt wird, wird der konvertierte Wert gespeichert.

### d) Konvertierungstakt

Der AD-Wandler wird im "Continuous conversion mode" betrieben. Ein Prozess erzeugt einen Takt, der über einen Pin des FPGA ausgegeben wird und die Konvertierung kontinuierlich startet.

Die Taktfrequenz wird erzeugt, indem ein Zähler hochgezählt wird. Ein Überlauf erfolgt bei

$$CONV\_CLK\_CNT = \frac{CLOCK\_FREQUENCY}{CONV\_CLK\_FREQUENCY*2} = \frac{133 \text{ MHz}}{6 \text{ MHz}*2} = 12.$$

(5.1)

Bei der Division entstehen nur ganzzahlige Werte. Der tatsächliche Wert beträgt 11,083. Dabei entsteht ein Fehler 7,6%. Für den Ablauf ist es unerheblich, dass die am AD-Wandler anliegende Spannung nicht mit der maximalen Frequenz abgetastet wird.

Nach dem Überlauf wird der Zähler zurückgesetzt und der Pin für den Takt umgeschaltet.

### 5.1.2 Ansteuerung des Piezomotors

### a) Drehrichtung

Das FPGA kann die Drehrichtung über ein Relais auf der SiKo-Platine verändern. Dazu muss am FPGA Pin "DIRECTION\_LR" eine ,1' oder eine ,0' angelegt werden.

### b) Motorspannung

Der Piezomotor wird mit einer Frequenz von 160 kHz angesteuert. Als Signalform für die Motorspannung wurde die Rechteckspannung gewählt, da diese mit dem geringsten Aufwand implementiert werden kann, und da die Bandbreite von 70 kHz [21] des Piezoverstärkers das Signal in allen Fällen nicht anders als verzerrten Sinus ausgeben wird. Der Maximalwert des Rechtecksignals wird in anderen Prozessen ermittelt und an den Prozess für die Ansteuerung des DA-Wandlers übergeben. Als DA-Wandler auf der Siko-Platine wird der CA3338 von intersil Corporation verwendet.

Abbildung 5.4: Zeitlicher Ablauf der Ansteuerung des DA-Wandlers [22]

In Abbildung 5.4 ist der zeitliche Ablauf der Ansteuerung des DA-Wandlers dargestellt. Um die Rechteckspannung anzulegen, wird ein Zustandsautomat mit sechs Zuständen benötigt. Folgender Code wurde implementiert:

```

1

if(piezoCnt = PIEZO_CNT_MAX - 1) then

2

piezoCnt <= 0;

3

else

4

piezoCnt <= piezoCnt+1;

5

if(piezoCnt = PIEZO_CNT_MAX * 0 / 8) then

6

P2_DAC_Data <= "00000000";

7

elsif(piezoCnt = PIEZO_CNT_MAX * 1 / 8) then

P2 DAC LE <= '0':

8

9

elsif(piezoCnt = PIEZO_CNT_MAX * 3 / 8) then

10

P2 DAC LE <= '1':

11

elsif(piezoCnt = PIEZO_CNT_MAX * 4 / 8) then

12

P2 DAC Data <= DAC Daten:

13

elsif(piezoCnt = PIEZO_CNT_MAX * 5 / 8) then

14

P2_DAC_LE <= '0';

15

elsif(piezoCnt = PIEZO_CNT_MAX * 7 / 8) then

16

P2_DAC_LE <= '1';

17

end if:

18

end if;

```

Die Konstante PIEZO\_CNT\_MAX wird folgendermaßen berechnet:

$$PIEZO\_CNT\_MAX = \frac{CLOCK\_FREQUENCY}{MOTOR\ FREQUENCY} = \frac{133\ MHz}{160\ KHz} = 832. \tag{5.2}$$

PIEZO\_CNT\_MAX Takte werden bei einer Taktfrequenz von 133 MHz benötigt für eine Periode der Frequenz 160 kHz. Die Variable piezoCNT wird in jedem Takt inkrementiert. In Abhängigkeit ihres Wertes werden die Daten angelegt und der Steuerpin P2\_DAC\_LE gesetzt bzw. zurückgesetzt. Wenn piezoCNT den Wert PIEZO\_CNT\_MAX – 1 erreicht hat, wird der Zähler wieder zurückgesetzt.

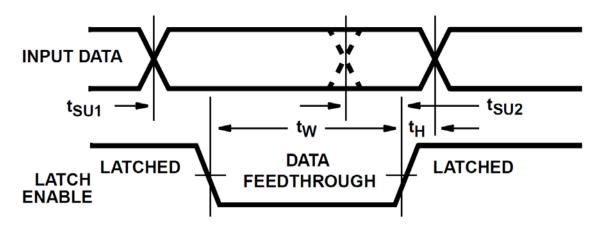

Die Wartezeiten  $t_{su1}$ ,  $t_H$ ,  $t_{su2}$  und  $t_w$  werden eingehalten, da sie deutlich kürzer sind als die Übergänge zwischen den einzelnen Zuständen.

Wenn der Piezomotor sich nicht drehen soll, wird der Wert "00000000" übergeben. Somit liegt am Piezomotor keine Spannung an.

Die Auflösung des DA-Wandlers beträgt 8 Bit [22]. Der DA-Wandler kann Spannungen zwischen 0 V und 5 V erzeugen.

### 5.1.3 Ansteuerung Encoder

An dem Piezomotor ist der Encoder HEDS-5600 angeschlossen. Encoder werden verwendet, um den gedrehten Winkel bzw. die Drehzahl von drehenden Achsen zu ermitteln.

### a) Pegelerfassung der Encodersignale

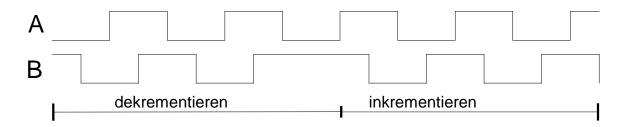

Der Encoder verwendet zwei Datenleitungen, auf denen ein Gray-Code erzeugt wird. Es ändert sich immer nur eine Spur auf einmal. In Abbildung 5.5 sind die Spuren der beiden Datenleitungen abgebildet. Im ersten Teil dreht sich die Achse in eine Richtung und ändert dann im zweiten Teil die Drehrichtung.

Abbildung 5.5: Spur A und B eines Encoders

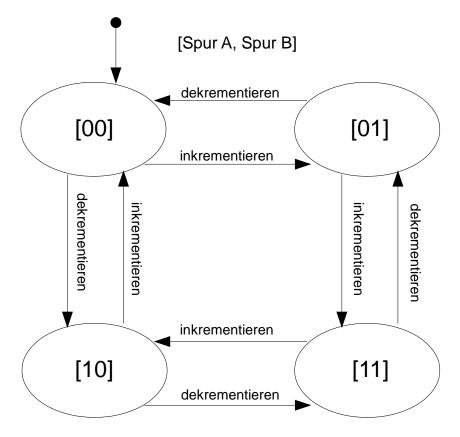

Die Signale des Encoders liegen am FPGA an. In einem Prozess werden die Pegel der beiden Spuren erfasst. Der Pegelstatus wird im nächsten Takt von einem anderen Prozess übernommen. In dem Zustandsautomaten in Abbildung 5.6 wird der Pegelstatus verarbeitet und je nach Zustandswechsel der Encodersignale wird eine Variable zum In- bzw. Dekrementieren gesetzt. In Abhängigkeit des gewählten Betriebszustands wird der Zähler verarbeitet.

Die Zustände in Abbildung 5.6 sind nach dem Zustand der beiden Spuren A und B benannt. Die Implementierung der Pegelermittlung und des Zustandsautomaten wurde [23] entnommen.

**Abbildung 5.6:** Zustandsautomat zur Bestimmung des gedrehten Winkels bzw. Drehzahl des Piezomotors

#### b) Berechnung der maximalen Drehzahl

Der Encoder hat eine Auflösung von 500 ppr [24], d. h. bei einer Drehung um 360° muss der Zustandsautomat 500 Mal durchlaufen werden. Der inkrementierte Zähler hat somit den Wert 2000.

Das FPGA kann in jedem Taktzyklus eine Zustandsänderung erkennen, somit sind das bei einer Taktfrequenz von 133 MHz 133 Millionen Zustandsänderungen. Bei 2000 Zustandsänderungen pro Umdrehung ergibt das eine maximale Drehzahl von

$$\omega = \frac{133000000}{2000} = 66500 \, s^{-1}, \tag{5.3}$$

was deutlich über der maximalen Drehzahl des Encoders liegt (30.000 rpm) [24].

### 5.1.4 Drehmoment Regelung

Der Ablauf in Abbildung 5.7 wurde bis auf den Regler komplett implementiert. Auf die einzelnen Prozesse wird nicht detailliert eingegangen. Lediglich der Ablauf wird beschrieben, da die Regelung des Drehmoments nicht in Betrieb genommen werden konnte. Das vom Piezomotor erzeugte Drehmoment ist nicht proportional zu der angelegten Spannung, folglich ist eine Regelung nicht möglich. Die genaue Begründung befindet sich in Kapitel 6.2.

proportional zum Drehmoment ausgegebene Spannung eines auf der SiKo-Platine **Drehmomentsensors** wird gemessen. liefert Informationen über die Drehrichtung sowie, ob ein Schwellwert für das Drehmoment überschritten wurde. Der Schwellwert beträgt ca. 150 mV und wurde experimentell ermittelt. Wenn der Drehknopf losgelassen wird und in den letzten Rastpunkt dreht, liegt ein Drehmoment am Piezomotor an. Dieses muss kleiner als der Schwellwert sein, sonst ermittelt der Zustandsautomat einen falschen Zustand. In Abhängigkeit der Drehrichtung wird das Relais gesteuert.

Der gedrehte Winkel wird über die Encodereingänge ermittelt. In Abhängigkeit des gedrehten Winkels wird in einer LUT die Führungsgröße ermittelt. Auf diese Weise können verschiedene Drehmomentcharakteristika erstellt werden. Durch die Führungsgröße kann bestimmt werden, ob sich der Drehknopf in der Nulllage befindet.

Abbildung 5.7: Ablauf der Drehmomentregelung

Die Informationen über Nulllage (genaue Erläuterung in 5.1.5 b) und anliegendem Drehmoment entscheiden, wie die Spannung ermittelt wird, die über den DA-Wandler und den Piezoverstärker an den Piezomotor angelegt wird. Folgende drei Zustände sind möglich:

- Nulllage: Wenn sich der Drehknopf in der Nulllage befindet, wird unabhängig vom anliegenden Drehmoment der Wert Null an den DA-Wandler übergeben. Der Piezomotor dreht sich folglich nicht.

- Drehknopf wird gedreht: Der Drehknopf wird gedreht und hat die Nulllage verlassen. In diesem Fall berechnet die Regelung in Abhängigkeit der Führungsgröße und des ermittelten Drehmoments den neuen Wert für die Spannung. Dadurch wird ein Drehmoment erzeugt, welches dem manuell eingeleiteten Drehmoment entgegen wirkt.

- Drehknopf wurde losgelassen: Der Drehknopf wurde nicht bis zur nächsten Nulllage gedreht, sondern vorher losgelassen. In diesem Fall liegt kein Drehmoment an und es wird ein konstanter Wert an den DA-Wandler übergeben, um den Drehknopf in die letzte Rasterung/Nulllage zu drehen.

Für die Messung in Kapitel 6.2 wurde keine Regelung implementiert. Stattdessen wird die an den DA-Wandler übergebene Spannung proportional zum gedrehten Winkel erhöht.

#### 5.1.5 Drehmoment Steuerung für virtuelle Rasterung

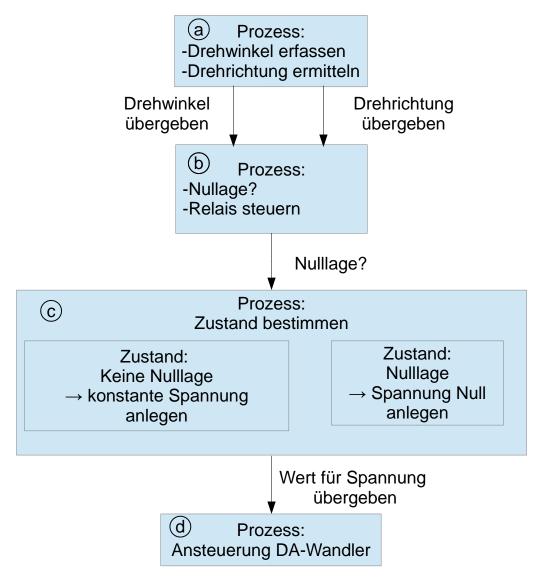

Als einfachere Alternative zur Drehmomentregelung wurde eine Drehmomentsteuerung implementiert. Der Drehmomentsensor und der AD-Wandler werden dafür nicht mehr benötigt.

Abbildung 5.8 zeigt den deutlich vereinfachten Ablauf der Drehmomentsteuerung. Die einzelnen Prozesse werden im Folgenden erläutert.

Abbildung 5.8: Ablauf der Drehmomentsteuerung

#### a) Drehwinkelermittlung mit Encoder

Bei der Drehmomentsteuerung wird mit dem Encoder der gedrehte Winkel des Piezomotors ermittelt. Der Zustandsautomat in Kapitel 5.1.3 wertet die Pegel des Encoders aus und setzt Variablen zum In- bzw. Dekrementieren eines Modulo-ANGLE-Zählers. "ANGLE" ist ein Array der zur Compile-Zeit festgelegten Grenzwerte, die die Anzahl der Rastpunkte festlegen. Diese können über den Drehschalter zur Laufzeit verändert werden.

b) Überprüfung auf Nulllage und Ansteuerung des Relais Mit Nulllage wird ein virtueller Rastpunkt bezeichnet, vergleichbar mit der stabilen Position zwischen zwei Zähnen des mechanischen Zahnrads. Die Nulllage entspricht einem Winkel von 1,8°. Dieser Wert wurde experimentell ermittelt. Wird der Wert zu klein gewählt, kann es passieren, dass die Motorspannung zu spät ausgeschaltet wird und der Drehknopf eine Rasterung überspringt.

In dem Takt, in dem die Nulllage verlassen wird, wird das Relais für die Drehrichtung des Piezomotors derart geschaltet, dass sich der Piezomotor versucht in die entgegengesetzte Richtung zu drehen. Dafür wird die Information "Drehrichtung" verwendet, die beim In- bzw. Dekrementieren gesetzt wird. Dadurch wird ein Drehmoment erzeugt, welches dem manuell eingeleiteten Drehmoment entgegen wirkt.

# c) Auswahl der zu übergebenden Spannung

Befindet sich der Drehknopf in der Nulllage, wird ein Wert übergeben, der eine Spannung von 0 V erzeugt. Der Piezomotor wird folglich abgeschaltet.

Wurde der Drehknopf manuell aus der Nulllage bewegt wird, wird der binäre Wert "1011111" an den DA-Wandler übergeben. Das entspricht einer Spannung von 3,7 V. Wenn der Drehknopf losgelassen wird, dreht er sich nicht mit maximaler Geschwindigkeit in die letzte Nulllage zurück. Es könnte sonst der Fall eintreten, dass sich der Piezomotor zu schnell zurückdreht dreht und so einen Rastpunkt überspringt.

### d) Ansteuerung DA-Wandler

Der vom Prozess in c) übergebene binäre Wert wird, wie in Kapitel 5.1.2 beschrieben, an den Prozess für die Ansteuerung des DA-Wandlers übergeben.

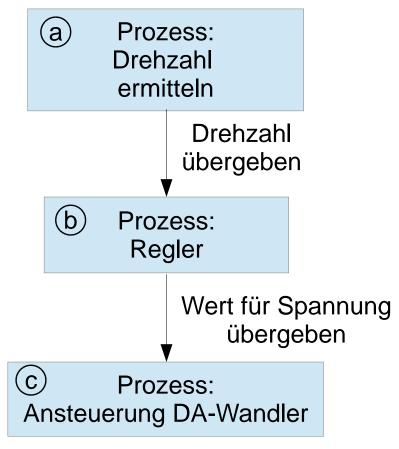

#### 5.1.6 Drehzahl Regelung

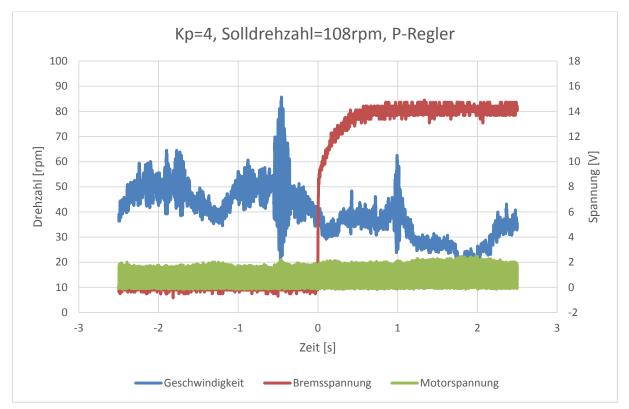

Abbildung 5.9 zeigt den Ablauf der Drehzahlregelung. Die einzelnen Prozesse werden im Folgenden erläutert. Für die Drehzahlregelung wurden ein P-Regler und ein PI-Regler implementiert. Der P-Regler wurde anschließend modifiziert, um ein besseres Regelverhalten zu erzeugen.

Abbildung 5.9: Ablauf der Drehzahlregelung

#### a) Drehzahl ermitteln

Bei der Drehzahlregelung wird über den Encoder die Drehzahl des Piezomotors ermittelt. Der Zustandsautomat in Kapitel 5.1.3 wertet die Pegel des Encoders aus und setzt Variablen zum In- bzw. Dekrementieren. Ein Zähler wird dabei 10 ms lang in- bzw. dekrementiert. Nach 10 ms wird das Signal S\_10msOver für die abgelaufene Zeit gesetzt und die Anzahl der Impulse pro 10 ms an den Regelprozess übergeben.

Das Zeitfenster von 10 ms wurde aufgrund der minimalen Drehzahl von 51 rpm gewählt, was 17 Impulsen pro 10 ms entspricht. Diese Drehzahl wurde ermittelt, indem eine Spannung angelegt wurde, bei der sich der Piezomotor dreht, ohne durch Reibung anzuhalten. Ein größeres Zeitfenster verlangsamt die Dynamik der Regelung unnötig. Bei einem kleineren Zeitfenster ist die Anzahl der Impulse zu gering.

### b) Regler

#### P- und PI-Regler:

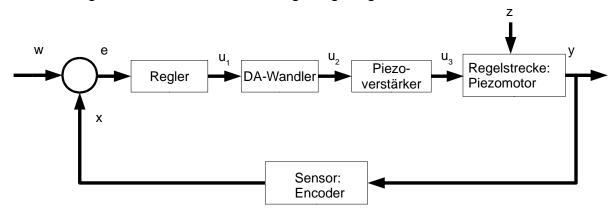

In Abbildung 5.10 ist die Struktur der Regelung dargestellt.

Abbildung 5.10: Struktur der Drehzahlregelung

Die Bezeichnungen bedeuten (Name des Signals im Programm):

w := Führungsgröße (SPEED)

e := Regelabweichung (Regelabweichung)

x := aktuelle Drehzahl (act\_speed\_in\_tp10ms)

u<sub>1</sub> := Stellgröße nach Regelung

u<sub>2</sub> := Stellgröße nach DA-Wandler

u<sub>3</sub> := Stellgröße nach Piezoverstärker

y := Regelgröße, Drehzahl des Piezomotors

z := Störgröße, z. B. Anlegen eines Bremsmoments

Der PI-Regler besteht aus einem Proportionalanteil und einem Integrationsanteil. Soll lediglich ein P-Regler verwendet werden, muss die Konstante K<sub>i</sub> Null gesetzt werden. Die Formel [24] für den PI-Regler ist folgende:

$$u_1 = K_p * e(t) + K_i * \int_0^t e(\tau) d\tau.$$

(5.4)

Regler in digitalen Systemen arbeiten zeitdiskret. Die Drehzahl wird nicht kontinuierlich ermittelt. Der Wert der neuen Drehzahl steht im Abstand von  $T_a$ =10 ms zur Verfügung. Die zeitdiskrete Formel [24] für den PI-Regler lautet:

$$u_k = K_p * e_k + K_i T_a * \sum_{i=0}^k e_i.$$

(5.5)

Die Konstanten  $K_i$  und  $T_a$  werden zusammengefasst zur Konstante  $K_{iDrehzahl}$ . Damit muss die Multiplikation dieser Konstanten nicht in jedem Zyklus neu berechnet werden.

Zusammen mit der Struktur in Abbildung 5.10 ergibt sich folgender Code:

```

1

-- Regelabweichung berechnen

2

Regelabweichung := SPEED - act_speed_in_tp10ms;

3

esum := esum + Regelabweichung:

-- Integration des I-Anteils

4

-- Begrenzung des I-Anteils, Anti Wind-Up

5

if esum <= - I_ANTEIL_BEGRENZUNG then

6

esum := -I_ANTEIL_BEGRENZUNG;

7

elsif esum >= I_ANTEIL_BEGRENZUNG then

8

esum := I_ANTEIL_BEGRENZUNG;

9

end if;

10

-- Berechnung des P-Anteils

sum1 := KpDrehzahl * Regelabweichung ;

11

12

-- Berechnung des I-Anteils

sum2 := KiDrehzahl * esum;

13

14

tmp_Stellgroesse := sum1 + sum2;

-- Summanden addieren

15

-- Stellgrößenbegrenzung

16

if tmp_Stellgroesse >= 255 then

17

tmp Stellgroesse := 255;

18

elsif(tmp_Stellgroesse <= 0) then

19

tmp_Stellgroesse:= 0;

20

end if;

```

In Zeile 2 wird die Regelabweichung (e) berechnet. Die Regelabweichung ist die Differenz der vorgegebenen Drehzahl (w) und der vom Encoder ermittelten Drehzahl (x). Diese Abweichung wird fortwährend für den I-Anteil aufsummiert (Zeile 3). In den Zeilen 5 bis 9 wird die Summe begrenzt. Hinter dieser Saturierung verbirgt sich der Anti-Windup-Algorithmus. Eine Saturierung von esum muss erfolgen, um bei blockiertem Piezomotor einen undefinierten Überlauf zu vermeiden.

In den Zeilen 11 bis 14 wird die Regelabweichung mit dem Proportionalbeiwert  $K_{pDrehzahl}$  und die Summe der Regelabweichungen mit dem Integrierbeiwert  $K_{iDrehzahl}$  multipliziert sowie die beiden Produkte addiert. Das Ergebnis ist die neue Stellgröße. Diese muss noch begrenzt werden (Zeile 16 bis 19). Der

minimale Wert ist Null. Der maximale Wert ist durch die Auflösung von 8 Bit vorgegeben und beträgt 255.

### Modifizierter P-Regler:

Der P-Regler wurde folgendermaßen modifiziert:

Zu der in Zeile 14 berechneten Stellgröße wird der Offset SPEED\_VOLTAGE addiert. SPEED\_VOLTAGE ist die von der Solldrehzahl abhängige Spannung, die in einer Voruntersuchung (s. Kapitel 6.4.1) ermittelt wurde.

Außerdem wurde die Stellgrößenbeschränkung verändert. Eine sinnvolle untere Schranke ist die minimale Spannung, bei der sich der Piezomotor dreht, ohne durch Reibung oder andere Störungen angehalten zu werden. Diese Spannung wurde experimentell ermittelt und beträgt ca.  $u_{min} = 1,6 \text{ V}$ . Der verwendete DAWandler besitzt eine Auflösung von 8 Bit [22]. Somit ergibt sich für die untere Schranke mit  $u_{max} = 5 \text{ V}$  als dezimal-Wert

$$u_{min,dez} = (2^8 - 1) * \frac{u_{min}}{u_{max}} = 255 * \frac{1.6 V}{5 V} = 81.$$

(5.6)

Die Zeilen 1 bis 14 bleiben unverändert.

```

... --Zeile 1 bis 14 unverändert

tmp_Stellgroesse := tmp_Stellgroesse + SPEED_VOLTAGE;

-- Stellgrößenbegrenzung

if tmp_Stellgroesse >= 255 then

tmp_Stellgroesse := 255;

elsif(tmp_Stellgroesse <= 81) then</li>

tmp_Stellgroesse:= 81;

end if;

```

#### c) Ansteuerung DA-Wandler

Der vom Prozess in b) übergebene binäre Wert wird, wie in Kapitel 5.1.2 beschrieben, an den DA-Wandler übergeben.

## 5.1.7 Konfiguration zur Compile-Zeit / Laufzeit (Benutzerschnittstelle)

#### a) Compile-Zeit Konfiguration

In der Datei settings.vhd sind alle Konstanten deklariert. Hier befinden sich die Parameter für die Regelung. Die Solldrehzahl und der dazugehörige Spannungswert sind in diese Datei einzutragen.

Die Systemtaktfrequenz sowie alle für die Komponenten verwendeten Frequenzen. sind in der Datei deklariert.

Die Anzahl der Rastpunkte wird hier ebenfalls eingetragen. Vor dem Synthetisieren werden die Grenzwerte in das Integerarray "RASTERSCHRITTE" in die Datei settings.vhd eingetragen. Der Grenzwert für eine gewünschte Anzahl an Rastpunkten pro Umdrehung berechnet sich folgendermaßen:

$$Grenzwert = \frac{2000}{Anzahl_{Rastpunkte}}. (5.7)$$

### b) Laufzeit Konfiguration

Zur Laufzeit wird die Auswahl der Anzahl der Rastpunkte über den Drehschalter gewählt.

Drehzahlregelung mit modifiziertem P-Regler und virtuelle Drehmomentsteuerung sind zwei Betriebsmodi, die im FPGA implementiert sind. Zwischen den beiden Betriebsmodi kann mit Schalter Null des DIP-Schalters umgeschaltet werden.

## c) LED Anzeigen

Um dem Benutzer anzuzeigen, dass die HACON-Platine betriebsbereit ist, wurde ein Prozess implementiert, der die LED PowerLED blinken lässt. Sie blinkt für die beiden Betriebsmodi mit verschiedenen Frequenzen. Wird der Betriebsmodus Rasterung gewählt, blinkt die LED mit 2 Hz, während der Drehzahlregelung mit 1 Hz.

Auf der HACON-Platine befinden sich fünf weitere LEDs. Je nach Betriebsmodus zeigen sie verschiedene Informationen an.

Im Betriebsmodus Rasterung zeigen die LEDs an, wie weit der Drehknopf noch gedreht werden muss, bis der nächste Rastpunkt erreicht ist. Eine LED entspricht etwa 20 % des Restwegs.

Während der Regelung wird die Drehzahl des Piezomotors auf die LEDs abgebildet. LED1 leuchtet ab einer Drehzahl von 51 rpm. LED5 leuchtet ab einer Drehzahl von 177 rpm. Die Drehzahlen dazwischen wurden gleichmäßig verteilt.

### 5.2 Testmodule für CONBOX

Die Implementierung der Testmodule für die CONBOX wurde aus Zeitgründen nicht durchgeführt.

# 6 Ergebnisse und Diskussion der Arbeit

# 6.1 Inbetriebnahme

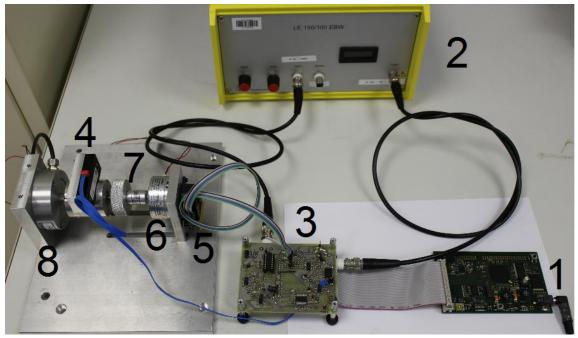

Eine Übersicht des gesamten Systems mit HACON-Platine, SiKo-Platine sowie der dazugehörigen Peripherie zur Ansteuerung des Piezomotors ist Abbildung 6.1 und Tabelle 6.1 zu entnehmen.

**Abbildung 6.1:** Gesamtübersicht über die verwendeten Platinen sowie der Peripherie zur Ansteuerung des Piezomotors

| Nr. | Bezeichnung                                                 | Funktion                                                                                                                                    |

|-----|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | HACON-Platine                                               | Reglerplattform mit FPGA                                                                                                                    |

| 2   | Piezoverstärker<br>LE 150/100 EBW von<br>Piezomechanik GmbH | Verstärkt die vom DA-Wandler erzeugte<br>Spannung                                                                                           |

| 3   | SiKo-Platine                                                | Platine um die analogen Signale der Motoransteuerung zu messen, konditionieren und für das Auslesen durch die HACON-Platine bereitzustellen |

| 4   | Piezomotor U-164.11 von Physikinstrumente GmbH & Co. KG     | 5 5,                                                                                                                                        |

| 5   | Encoder HEDS-5600 von<br>Avago Technologies                 | Erfassung des gedrehten Winkels bzw. der Drehzahl des Piezomotors                                                                           |

| 6   | Hysteresebremse HB-10M-<br>2DS von mobac                    | Erzeugt Bremsmoment                                                                                                                         |

| 7   | Drehknopf                                                   | Benutzerschnittstelle für haptisches<br>Feedback                                                                                            |

| 8   | Drehmomentsensor ATF315 von Althen                          | Messung der proportional zum Drehmoment ausgegebenen Spannung                                                                               |

**Tabelle 6.1:** Bezeichnung und Funktion der verwendeten Geräte zur Ansteuerung des Piezomotors

#### 6.1.1 HACON-Platine

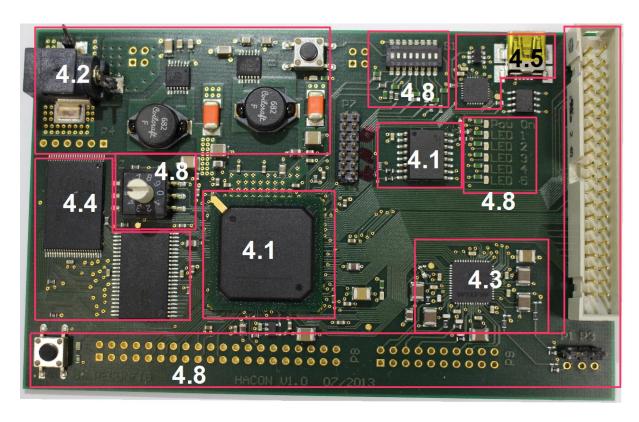

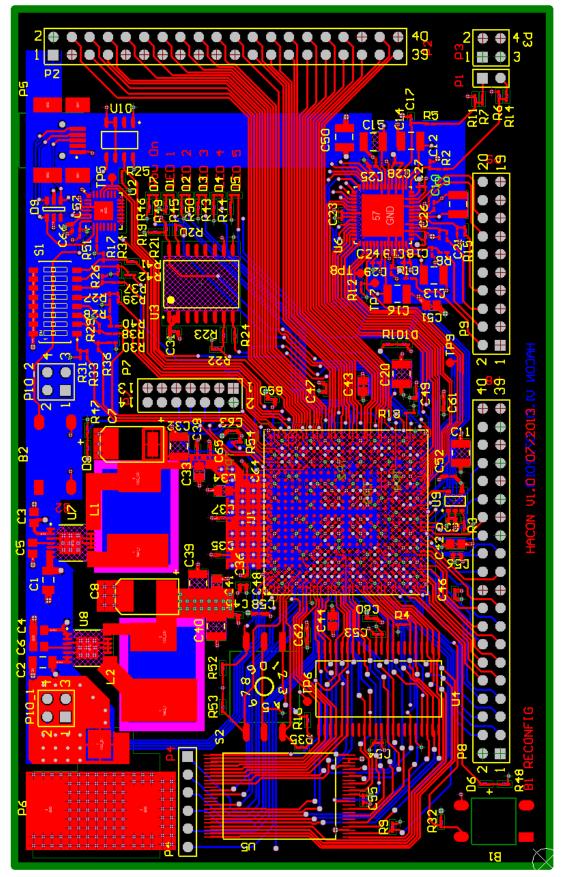

In Abbildung 6.2 ist die bestückte Platine mit den einzelnen in Kapitel 4 beschriebenen Baugruppen zu sehen. Der Voltage-Monitor und der Oszillator sind aufgrund der kleinen ICs nicht separat markiert.

**Abbildung 6.2:** Bestückte HACON-Platine. Die Nummerierung entspricht den Unterkapiteln in Abschnitt 4. Voltage-Monitor und Oszillator sind nicht nummeriert.

Nach der Verifikation der Spannungs- und Taktversorgung per Oszilloskop wurde das FPGA mit einem Testdesign zum Ansteuern der LEDs programmiert. Das Laden des Bitstreams aus dem Konfigurationsspeicher und das Zurücksetzen per Taster B1 bzw. B2 wurden ebenfalls erfolgreich getestet. AD-Wandler, USB zu UART Wandler, SRAM-Speicher und Flash-Speicher wurden nicht in Betrieb genommen, da sie in der vorliegenden Arbeit nicht verwendet wurden.

#### 6.1.2 SiKo-Platine

Die SiKo-Platine wurde im Rahmen einer vorhergehenden Arbeit [1] nicht vollständig in Betrieb genommen. Der DA-Wandler und der AD-Wandler sowie einige andere Komponenten wurden bestückt und in Betrieb genommen. Der AD-Wandler ersetzt den Spannungsteiler R33 / R35 zur Generierung der 2,5 V Referenzspannung.

Die Ansteuerung des Relais zur Änderung der Drehrichtung des Piezomotors hat nicht funktioniert. Am Steckverbinder, der die Platine mit dem Piezomotor verbindet, wurden zwei Anschlüsse vertauscht.

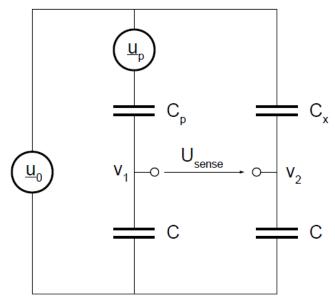

Auf der SiKo-Platine befindet sich eine kapazitive Messbrücke zur intrinsischen Messung des Drehmoments. Die Messbrücke besteht, wie in Abbildung 6.3 zu sehen, aus einer Reihenschaltung der Piezomotorkapazität  $C_p$  und einem Kondensator C=33 nF. Parallel dazu befindet sich eine weitere Reihenschaltung aus einem Kondensator  $C_x\approx C_p$  mit und einem weiteren Kondensator C.

Abbildung 6.3: Messbrücke zur intrinsischen Drehmomentmessung

Die Potentiale  $V_1$  und  $V_2$  an den Mittelabgriffen der beiden kapazitiven Spannungsteiler liegen laut [1] bei nichtanliegendem Drehmoment bei ca. 30 V. Gemessen wurde bei  $U_0 \approx 150$  V mit 155 kHz allerdings für  $V_1 \approx 60$  V und für  $V_2 \approx 1$  V.

Die erste Vermutung war eine fehlerhafte Messung der Motorkapazität. Eine erneute Messung mit einem LCR-Messgerät und einem Spektrumanalysator ergab einen Wert von  $C_P \approx 470$  pF, was identisch mit dem Ergebnis in [1] ist. Um mögliche unbekannte Fehlerquellen auf der Platine auszuschließen, wurde

der linke Zweig der Messbrücke separat auf einer Lochrasterplatine aufgebaut. Die Messungen ergaben dasselbe Verhalten wie auf der SiKo-Platine.

Anschließend wurden für den Kondensator C verschiedene Werte eingesetzt. Für 4,7 nF <= C <= 14,7  $\mu$ F schwankte V1 zwischen 55 V und 61 V. U<sub>0</sub> setzt sich zusammen aus einem Gleichspannungsanteil von U<sub>0,DC</sub>=75 V und einem Wechselspannungsanteil von U<sub>0,AC</sub>=150 V. Die Kondensatoren bilden für den

Gleichspannungsanteil einen Spannungsteiler von zwei unendlichen Widerständen. Der Gleichspannungsanteil wird folglich halbiert. Der Wechselspannungsanteil berechnet sich mit der Formel für den kapazitiven Spannungsteiler [19]:

$$V_1 = U_{0,AC} \frac{c_p}{c + c_p}. (6.1)$$

Folglich sollten für V<sub>1</sub> Spannungen zwischen 37,5 V und 51 V gemessen werden. Bis zum Abschluss der Arbeit konnte dieses Verhalten nicht geklärt werden. Eine mögliche Ursache könnte die begrenzte Bandbreite von 70 kHz [21] des Piezoverstärkers sein. Weitere Untersuchungen zum Ausschluss des Piezoverstärkers als Fehlerquelle sind zu erfolgen.

## **6.2 Messungen mit Drehmomentsensor**

### a) Durchführung

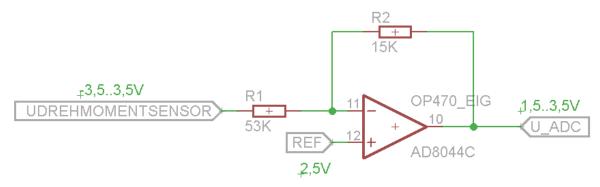

Zur Simulation der in Kapitel 2.2.2 beschriebenen Rasterung wird das am Piezomotor anliegende Drehmoment Da benötigt. die intrinsische Drehmomentmessung nicht in Betrieb genommen werden konnte, wurde der externe Drehmomentsensor ATF315 von Althen angeschlossen. Die Integration in den Messstand ist Abbildung 6.1 zu entnehmen. Die proportional zum Drehmoment ausgegebene Spannung wird mit dem Messverstärker KWS 3082 A von HBM verstärkt. Die verstärkte Spannung liegt im Bereich zwischen -3,5 V und +3,5 V. Der AD-Wandler auf der SiKo-Platine besitzt einen Spannungsmessbereich von 1,5 V bis 3.5 V. Um die verstärkte Spannung des Drehmomentsensors in den messbaren Bereich des AD-Wandlers zu konvertieren, wird ein invertierender Verstärker mit einem Verstärkungsfaktor von A=-0,283 und einem Levelshift um 2,5 V eingesetzt. Abbildung 6.4 zeigt die Verschaltung des verwendeten Operationsverstärkers AD8044 von Analog Devices. Die Versorgungsspannung beträgt 5 V. Die Verstärkerschaltung wurde auf einer Lochrasterplatine aufgebaut und mit Fädeldrähten mit der SiKo-Platine verbunden.

**Abbildung 6.4:** Verschaltung des invertierenden Operationsverstärkers, um die Spannung des Drehmomentsensors in den Messbereich des AD-Wandlers zu konvertieren

Als Vorversuch für die Drehmomentregelung soll zunächst der Einfluss der Motorspannung auf das Drehmoment untersucht werden. Der Drehknopf wird bis zum nächsten Rastpunkt gedreht. Dabei wird in Abhängigkeit des gedrehten Winkels die Motorspannung gesteigert. Die proportional zum Drehmoment ausgegebene Spannung wird aufgenommen.

### b) Ergebnisse

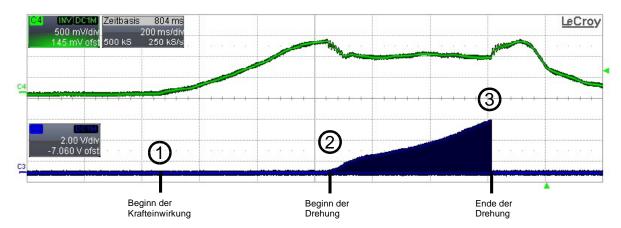

In Abbildung 6.5 ist der Einfluss der Motorspannung auf das entstehende Drehmoment zu sehen. Die blaue Linie  $C_3$  zeigt den Verlauf der vom DA-Wandler erzeugten Motorspannung, Kanal  $C_4$  (grün) zeigt den Verlauf der dem Drehmoment am Piezomotor proportionalen Spannung. Bei Punkt 1 beginnt die Krafteinwirkung auf den Drehknopf. Das Drehmoment steigt an, bis das Reibmoment in Punkt 2 überschritten ist und die Drehung beginnt. Die Motorspannung wird danach proportional zum gedrehten Winkel bis zum Maximum erhöht. In Punkt 3 ist der nächste Rastpunkt erreicht.

**Abbildung 6.5:** Einfluss der Motorspannung auf das Drehmoment. Kanal C<sub>3</sub> stellt den Verlauf der Motorspannung dar, die am DA-Wandler anliegt. Kanal C<sub>4</sub> stellt den Verlauf der zum Drehmoment proportionalen Spannung des Drehmomentsensors dar. Bei 1 beginnt die Krafteinwirkung auf den Drehknopf. Punkt 2 zeigt den Beginn der Drehung, bei 3 ist die maximale Motorspannung erreicht. Die Motorspannung wird dann abgeschaltet.

#### c) Diskussion

Der Piezomotor ist selbsthemmend. Aus diesem Grund wird ein bestimmtes Drehmoment benötigt, um den Drehknopf zu drehen. In Punkt 2 beginnt die Drehung und die Motorspannung steigt proportional zum gedrehten Winkel. Zwischen den Punkten 2 und 3 ist kein Anstieg des Drehmoments zu erkennen. Das entstehende Drehmoment ist folglich nicht proportional zur angelegten Motorspannung. Aus diesem Grund ist eine Regelung des Drehmoments nicht möglich.

# 6.3 Steuerung für virtuelle Rasterung

Statt einer Drehmomentregelung mit virtueller Rasterung wurde eine Steuerung erfolgreich implementiert. Diese Steuerung simuliert die in Kapitel 2.2.2 beschriebene Rasterung. Die Rasterung, welche in beide Richtungen funktioniert, ist beim Drehen des Drehknopfs deutlich spürbar. Wenn der Drehknopf losgelassen wird, bevor der nächste Rastpunkt erreicht ist, dreht sich der Drehknopf in die Position des letzten Rastpunkts zurück. Beim Zurückdrehen wird nicht die maximale Spannung an den Piezomotor angelegt, weil der Piezomotor nicht rechtzeitig abbremsen und einen Rastpunkt überspringen könnte. Die Anzahl der Rastpunkte ist zur Laufzeit veränderbar. In Abhängigkeit der Schalterstellung können 4, 5, 8, 16, 20 oder 40 Rastpunkte pro Umdrehung gewählt werden. Die Konfigurationsmöglichkeiten können zur Compile-Zeit frei definiert werden.

## 6.4 Messungen mit Drehzahlregelung

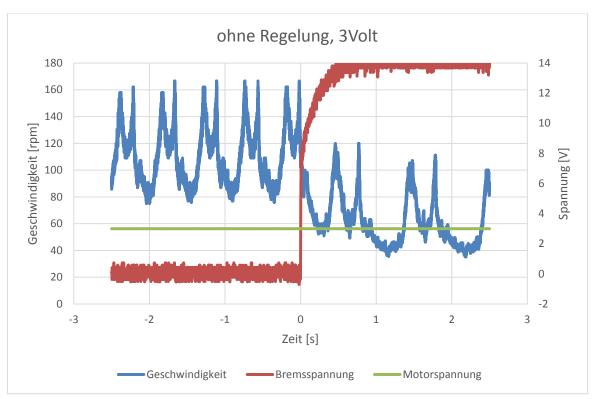

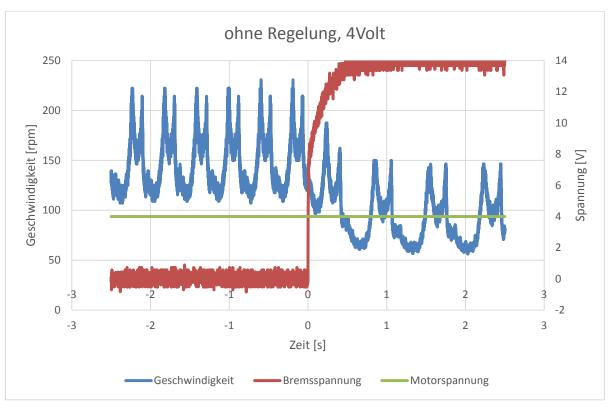

Für die Drehzahlregelung wurde zuerst eine Voruntersuchung durchgeführt, bei der geklärt werden soll, ob die Drehzahl abhängig von der angelegten Spannung ist. Anschließend wurde ein reiner P-Regler implementiert und Messungen durchgeführt. Die Messungen sollen den Drehzahlverlauf bei einer konstanten Spannung und die Reaktion auf ein angelegtes Bremsmoment zeigen. Der Einfluss der Regelung auf den zeitlichen Verlauf der Motordrehzahl wird untersucht. Anschließend wurde der P-Regler modifiziert. und die Messung des Drehzahlverlaufs erneut aufgenommen. Die Erläuterung zur genauen Implementierung befindet sich in Kapitel 5.1.6.

### 6.4.1 Voruntersuchung

### a) Durchführung

Für die Voruntersuchung wurde die Drehzahl bei den vier Motorspannungen 2 V, 3 V, 4 V und 4,5 V ermittelt. Diese Motorspannung wird vom DA-Wandler erzeugt, vom Piezoverstärker mit dem Faktor 30 verstärkt und an den Piezomotor angelegt. Die Anzahl der Umdrehungen nach 20 s wurde gezählt und mit drei multipliziert. Der Drehzahlverlauf wurde aufgezeichnet.

### b) Ergebnisse

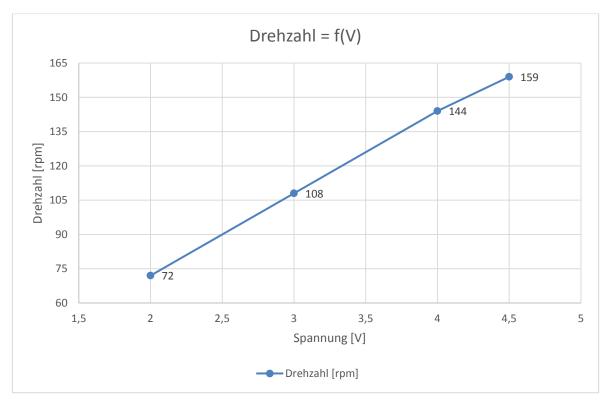

Abbildung 6.6 zeigt die gemessenen Drehzahlen sowie die Abhängigkeit der Drehzahl von der angelegten Spannung.

Abbildung 6.6: Abhängigkeit der Drehzahl von der angelegten Spannung

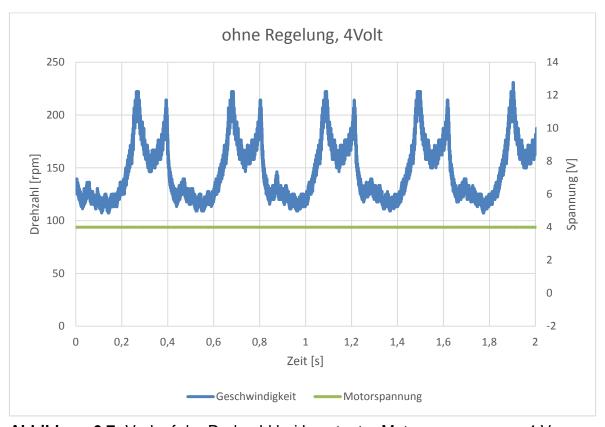

Abbildung 6.7: Verlauf der Drehzahl bei konstanter Motorspannung von 4 V

Der Drehzahlverlauf bei 4 V ist in Abbildung 6.7 zu sehen. Der Piezomotor besitzt einen unrunden Verlauf. Die Drehzahl schwankt bei der Messung mit 4 V im Verlauf einer Drehung zwischen 107 rpm und 222 rpm.

Die Diagramme der weiteren Messungen befinden sich in Anhang D.

### c) Diskussion

Die Drehzahl ist abhängig von der angelegten Motorspannung. Ein linearer Zusammenhang ist hierbei zu erkennen. Somit kann eine Drehzahlregelung implementiert werden.

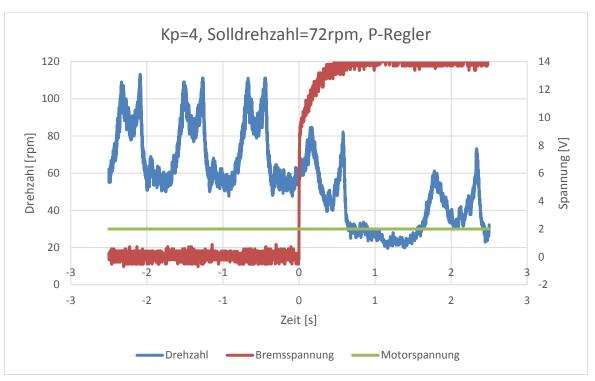

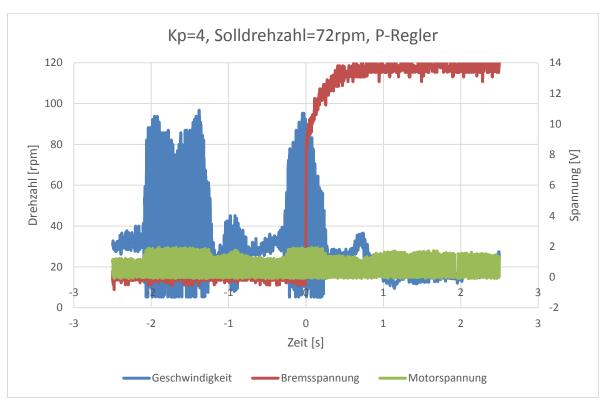

### 6.4.2 Messungen mit P-Regler

### a) Durchführung