News Archive

-

Two ESA presentations on ASPLOS 2026

At this year’s ASPLOS, ESA will be represented with two papers accepted for presentation.

The first paper Co-Exploration of RISC-V Processor Microarchitectures and FreeRTOS Extensions for Lower Context-Switch Latency by Markus Scheck, Tammo Mürmann, and Andreas Koch will be presented on the main conference. In this work, we are aiming at improving the hard real-time applicability of embedded RTOS systems using deferred interrupt handling. We aim at reducing context-switch latency through configurable, fine-granular hardware support and explore the up- and downsides of different hw/sw splits.

Our second presentation will be virtually held on the LATTE workshop. In the position paper TaPaSCo: Towards a Plug-and-Play FPGA Experience by Torben Kalkhof, David Volz, and Andreas Koch, we highlight the current state of our TaPaSCo framework and provide an outlook on future developments.

We are looking forward to insightful discussions at ASPLOS.

By Torben Kalkhof, 23.03.2026

-

ESA has three papers accepted at SC25-colocated workshops

We’re pleased to share that our research group will be strongly represented at Supercomputing 2025 (SC25) in St. Louis, USA, with three papers accepted across two co-located workshops. These contributions highlight our ongoing efforts in heterogeneous acceleration, compute-graph frameworks, and network-to-storage acceleration.

Our first accepted paper, Architecting Tensor Core-Based Reductions for Irregular Molecular Docking Kernels (DOI: 10.1145/3731599.3767437), by Leonardo Solis-Vasquez, Andreas F. Tillack, Diogo Santos-Martins, Andreas Koch, and Stefano Forli, explores how NVIDIA Tensor Cores can be adapted to accelerate irregular reduction patterns found in molecular docking, while maintaining accuracy through targeted error-correction strategies.

The second paper, A Compute Graph Simulation and Implementation Framework Targeting AMD Versal AI Engines (DOI: 10.1145/3731599.3767411), authored by Jonathan Strobl, Leonardo Solis-Vasquez, Yannick Lavan, and Andreas Koch, introduces a framework that enables embedding compute graphs directly into C++ applications and deploying them onto AMD Versal AI Engines (AIEs). This work connects high-level graph representations with spatial computing on modern heterogeneous devices.

Our third accepted submission, SNAcc: An Open-Source Framework for Streaming-based Network-to-Storage Accelerators (DOI: 10.1145/3731599.3767412), by David Volz, Torben Kalkhof, and Andreas Koch, presents an open-source FPGA-based framework for designing streaming network-to-storage acceleration pipelines—an increasingly important topic as data-movement costs dominate modern HPC systems.

Together, these three papers underscore the continued technical depth and diversity of our group’s research activities. We extend our thanks to all co-authors, collaborators, and supporting institutions for making this possible. We look forward to presenting at SC25, engaging with the community, and sharing insights on these topics.

By Dr.-Ing. Leonardo Solis-Vasquez, 17.11.2025

-

ESA paper presented at IPDPS 2025

We are proud to announce that our paper “Accelerating Sparse Linear Solvers on Intelligence Processing Units” by Tim Noack, Louis Krüger, and Andreas Koch has been presented at IPDPS 2025 in Milano, Italy.

In this work, we present Graphene, an open-source framework for efficiently solving large sparse linear systems on Intelligence Processing Units (IPUs). Graphene uses a custom Domain-Specific Language (DSL) that enables expressing complex algebraic algorithms close to their mathematical notation. To the best of our knowledge, we are the first to combine the Mixed-Precision Iterative Refinement method (MPIR) with Double-Word Arithmetics to achieve high precision solutions on an architecture lacking native double-precision support. Graphene is available on GitHub.

By Tim Noack, 10.06.2025

-

AMD HACC Tech Talk and TaPaSCo Example Repository

In October, we had been invited to present our TaPaSCo framework in the AMD HACC Tech Talk series. The talk, given by Torben Kalkhof, is now freely available on YouTube! In this talk, we explore how TaPaSCo leverages key features of the AMD Versal architecture, including AI Engines (AIE) for high-performance compute, Queue Direct Memory Access (QDMA) for efficient data streaming, and Multi-rate MAC (MRMAC) for high-speed networking.

Also, check out our new TaPaSCo Examples Github repository. Here, the source code of both presented examples is available. We plan to continuously add further examples to demonstrate the usage of different TaPaSCo features in the future.

By Torben Kalkhof, 4.11.2024

-

ESA papers at workshops of SC 2024

We can proudly announce that two ESA papers have been accepted for presentation at the workshops of SC 2024.

The first paper, titled Speeding-Up LULESH on HPX: Useful Tricks and Lessons Learned using a Many-Task-Based Approach by Torben Kalkhof and Andreas Koch will be presented at PAW-ATM 2024. In this work, we port the OpenMP-based reference implementation of the LULESH proxy application to the HPX programming framework, achieving speedups from 1.33x to 2.25x. Furthermore, we present our optimization techniques used for switching from a fork-join to a many-task-based programming paradigm.

The second paper, titled DeLiBA-K: Speeding-up Hardware-Accelerated Distributed Storage Access by Tighter Linux Kernel Integration and Use of a Modern API by Babar Khan and Andreas Koch, is based on our FPGA-based storage framework, DeLiBA-K, at the Linux kernel level (io_uring being a significant part). This work is a result of a joint collaboration with our industrial partner where we further developed and tested our improved Ceph storage FPGA accelerator in DeLiBA-K also on industrial benchmarks. This paper will be presented at the H2RC workshop, and the final open-source version of DeLiBA-K will be released ahead of the SC 2024 in Nov 2024.

Congratulations to everyone involved!

By Torben Kalkhof, 14.10.2024

-

ESA paper wins Best Paper Award at RAW 2024 and new TaPaSCo release

We are proud to announce that our paper entitled TaPaSCo-AIE: An Open-Source Framework for Streaming-based Heterogeneous Acceleration using AMD AI Engines - by Carsten Heinz, Torben Kalkhof, Yannick Lavan, and Andreas Koch - has won the Best Paper Award at RAW 2024, co-hosted with IPDPS in San Francisco, CA.

In this work, we propose a framework for streaming-based computation in heterogeneous systems. TaPaSCo-AIE focuses on AMD Versal devices and incorporates AI Engines, DMA streaming and 100G network. In our real-world evaluation based on a neural network, we achieve significant speed up over memory-mapped solutions, and exceed the performance of CPUs and even an A100 GPU.

All proposed extensions are included in our newest TaPaSCo 2024.1 release along with further improvements of our framework. Check out our Github repository and release notes for more details.

Congratulations and keep up the good work everyone!

By Torben Kalkhof, 29.05.2024

-

Two ESA papers get accepted at ARC 2024

We are very happy to announce that two submitted papers by our group have been accepted at ARC 2024 and will be presented in Aveiro, Portugal.

The first paper entitled Graphtoy: Fast Software Simulation of Applications for AMD’s AI Engines – by Jonathan Strobl, Leonardo Solis-Vasquez, Yannick Lavan, and Andreas Koch – proposes a graph simulator which can be embedded into an existing application to prototype acceleration compute kernels for data flow accelerator architectures, such as the AMD AI Engines. By leveraging cooperative multi-tasking, Graphtoy outperforms the AMD AI Engine x86 simulator while providing better debugging possibilities.

The second paper entitled Enabling FPGA and AI Engine Tasks in the HPX Programming Framework for Heterogeneous High-Performance Computing – by Torben Kalkhof, Carsten Heinz, and Andreas Koch – proposes the transparent usage of TaPaSCo FPGA and AI Engine tasks in HPX by adopting the lightweight threading model of HPX for TaPaSCo tasks. As proof-of-concept speedups are shown in a 1D-stencil benchmark and a port of the LULESH proxy application by leveraging cooperative computing on CPU and FPGA or AI engines, respectively.

Congratulations and keep up the good work everyone!

By Torben Kalkhof, 12.03.2024

-

ESA’s work on oneAPI and AutoDock-GPU is featured on Intel Community Blog

A recent post at https://community.intel.com features an article about our latest work levering oneAPI for achieving a SYCL-enabled version of the AutoDock-GPU molecular docking application.

The post describes our collaboration with Intel for migrating AutoDock-GPU from CUDA to SYCL, and thus, freeing this code-base from lock to a specific GPU vendor. Moreover, it highlights that our work 1) provides a detailed process reference for CUDA-to-SYCL migration and 2) evaluates the SYCL code-base of AutoDock-GPU on Intel Data Center Max 1550 GPU (code-named Ponte Vecchio), 4th Gen Intel Xeon Scalable Processor, as well as NVIDIA GPU.

Enjoy reading the full post AutoDock-GPU: SYCL Enabled Molecular Screening for Science and Medicine!

By Dr.-Ing. Leonardo Solis-Vasquez, 21.08.2023

-

ESA Team achieved 10th place at Meet And Move Ultra Marathon

After winning the first place in the TU Darmstadt Meet And Move Ultra Marathon lottery back in 2022, the ESA team proudly reached the 10th place in this year’s competitive run. Our team was supported by multiple ESA-external runners. Torben Kalkhof was our fastest runner with 18.33 minutes.

By Christoph Spang, 23.05.2023

-

Best Paper Award at DASIP 2023

Our work TaPaFuzz - An FPGA-Accelerated Framework for RISC-V IoT Graybox Fuzzing has won the Best Paper Award at DASIP 2023. We are extremely happy. Thanks to the committee for selecting our work!

By Florian Meisel, 20.01.2023

-

Invited Talk at Global RISC-V Summit 2022

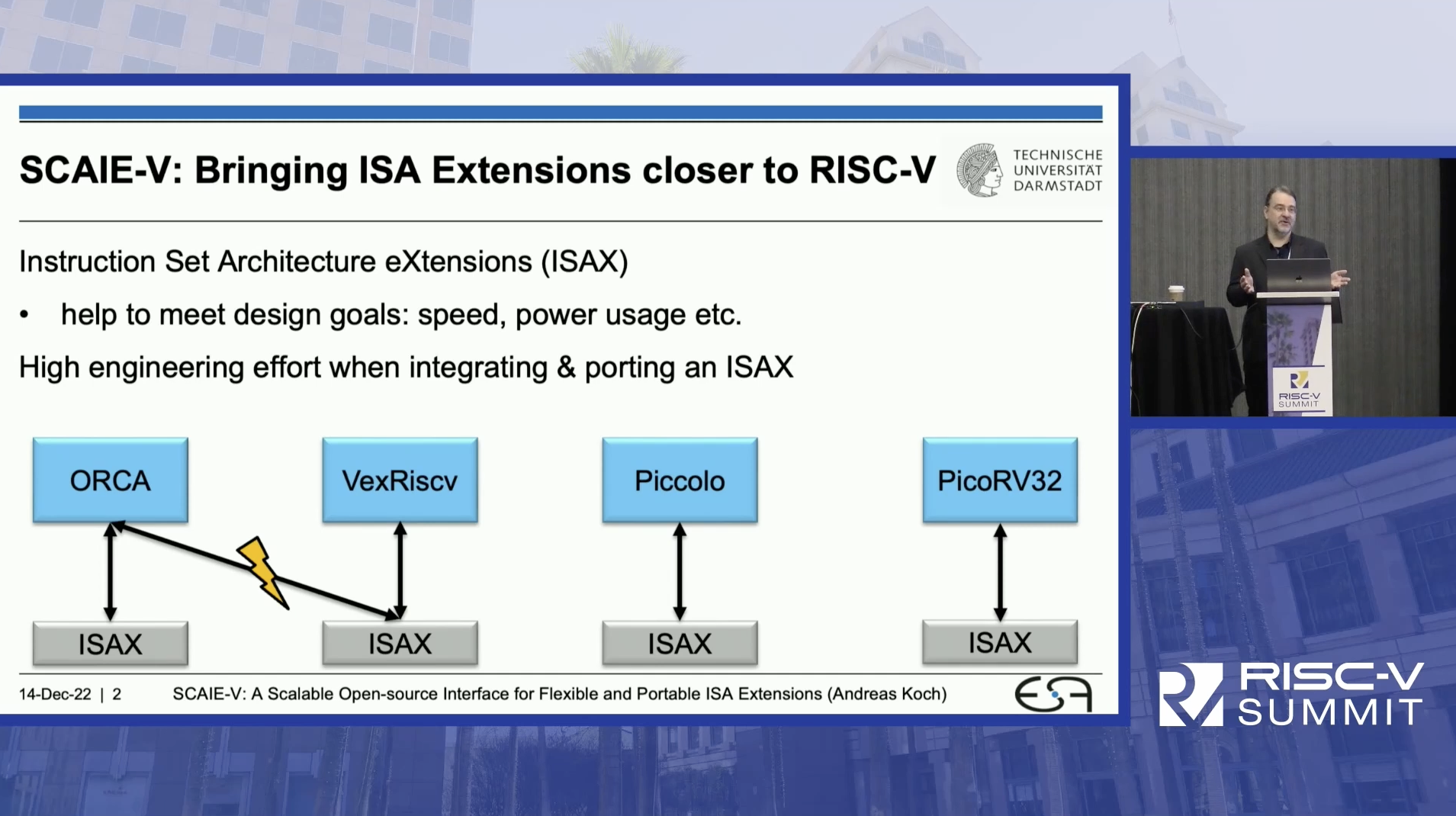

After a highly competitive selection process (13% acceptance rate), ESA researchers Mihaela Damian, Julian Oppermann, Christoph Spang and Andreas Koch were chosen for presenting their SCAIE-V scalable and portable interface for adding custom instructions to RISC-V processors at the 2022 Global RISC-V Summit.

The RISC-V Summit is the key global event for presenting advances around the open RISC-V processor instruction set architecture (ISA), which is shaping up to be a viable alternative to the existing proprietary solutions in a number of application domains.

The SCAIE-V interface developed by the ESA Group provides a standardized way to extend the base RISC-V instruction set with specialized instructions, for example, for application domains such as machine learning, IT security, or digital signal processing. This specialization can be used to improve the performance and/or energy efficiency of the customized processors. Using SCAIE-V, these specialized instructions can easily be attached to different base processor cores, with the interface automatically scaling to the needs of the actual custom instructions used.

A video of the presentation is available, which is based on an earlier research paper presented at the DAC 2022 conference.

By Prof. Dr-Ing. Andreas Koch, 4.01.2023

-

Best Paper Award at ICACGA 2022 in Denver

Our work GAAlign: Robust Sampling-based Point Cloud Registration using Geometric Algebra has won a Best Paper Award (GA Applied to Computational Performance) at ICACGA 2022. We are extremely happy. Thanks to the committee for selecting our work!

By Dr.-Ing. Florian Stock, 5.10.2022

-

ESA wins Best Paper Award at FPL 2022

We are glad that our paper “DeLiBA: An Open-Source Hardware/Software Framework for the Development of Linux Block I/O Accelerators” wins the best paper award at FPL 2022 conference. The award was presented during the banquet on Tuesday 30th August by the Chair of the Best Paper Award Committee at Belfast, UK. Congratulations to the other nominees for their excellent research work.

By Babar Khan, 8.09.2022

-

Two ESA papers get accepted at FPL 2022

We are very happy to announce that two submitted papers of our group have been accepted for presentation at FPL 2022

The first paper entitled DeLiBA: An Open-Source Hardware/Software Framework for the Development of Linux Block I/O Accelerators – by Babar Khan, Carsten Heinz, and Andreas Koch – is a result of the SODDAS project. DeLiBA aims to address Linux block I/O acceleration by allowing development of software components of the I/O stack in the user space instead of the kernel space, and leverages a proven FPGA SoC framework to quickly compose and deploy the actual FPGA-based I/O accelerators. The framework uses a software-defined distributed storage protocol, namely Ceph, for the proof-of-concept implementation.

The second paper entitled Direct Device-to-Device Physical Page Migrations in Multi-FPGA Shared Virtual Memory Systems – by Torben Kalkhof and Andreas Koch – extends the TaPaSCo SVM feature by introducing Shared Virtual Memory (SVM) with physical page migrations to multi-FPGA architectures. Three different data transfer mechanisms for the additional direct device-to-device page migrations are examined in this work: a two-step copy approach via PCIe and a bounce buffer in host memory, direct PCIe endpoint-to-endpoint transfers, and data transfers over a 100G Ethernet connection.

Congratulations and keep up the good work everyone!

By Torben Kalkhof, 20.07.2022

-

ESA paper gets accepted at DAC 2022

We are very happy to announce that our submitted paper has been accepted for presentation at DAC 2022.

This paper entitled SCAIE-V: An Open-Source SCAlable Interface for ISA Extensions for RISC-V Processors –- by Mihaela Damian, Julian Oppermann, Christoph Spang and Andreas Koch -– is a result of the Scale4Edge project. The paper presents a new scalable interface named SCAIE-V, which integrates custom instructions into RISC-V cores. Currently, the project supports 4 cores (Piccolo, PicoRV32, VexRiscv and ORCA) for which the custom instructions can be integrated automatically. The interface can interact with the core’s register file, program counter as well as memory bus. The corresponding logic is added only if it is required by the custom instruction. Moreover, SCAIE-V supports decoupled instructions, which run in parallel to the main pipeline. All these features facilitate a faster integration of ISA extensions while reaching for a low hardware penalty.

By Brindusa Mihaela Damian, 24.03.2022

-

Two ESA papers get accepted at FPT 2021

We are very happy to announce that two submitted papers by our group have been accepted for presentation at FPT 2021.

The first paper entitled Efficient Physical Page Migrations in Shared Virtual Memory Reconfigurable Computing Systems – by Torben Kalkhof and Andreas Koch – proposes an open-source development framework that provides Shared Virtual Memory with physical page migration capabilities to PCIe-attached FPGA-based cards. Based on the experiments, the performance of page migrations may even exceed that of conventional DMA copy-based accelerator operations by overlapping computations and migrations.

The second paper entitled Scalable and Flexible High-Performance In-Network Processing of Hash Joins in Distributed Databases – by Johannes Wirth, Jaco A. Hofmann, Lasse Thostrup, Carsten Binnig, Andreas Koch – combines the usage of DDR-DRAM and HBM memories to implement an FPGA-based In-Network Hash Join accelerator. By doing so, larger joins are supported, as well as the far-faster and more-parallel HBM accesses can be leveraged. As a result, the accelerator achieves 3x higher performance compared to previous work, which was based on HBM only.

Good work everyone!

By Dr.-Ing. Leonardo Solis-Vasquez, 5.11.2021

-

Lukas Sommer defends his Ph.D.-thesis

On 18th October 2021, Lukas Sommer successfully defended his Ph.D.-thesis entitled Programming Heterogeneous Systems with General and Domain-Specific Frameworks. In his work, Lukas investigated general and domain-specific solutions to the challenges of heterogeneous systems programming.

Lukas’ contributions comprise the identification of key factors to assess the suitability of general programming frameworks for applications and target platforms. Furthermore, he developed a domain-specific compiler for Sum-Product Networks (SPNs) that can target CPUs, GPUs, and FPGAs. The SPN programs produced by Lukas’ compiler can reach inference throughput of multiple orders of magnitude higher compared to existing Python-based libraries.

Congratulations to Dr.-Ing. Lukas Sommer!

By Dr.-Ing. Leonardo Solis-Vasquez, 20.10.2021

-

ESA contributes with article on AutoDock-GPU to HiPEAC info 64

The latest issue of the HiPEAC Info magazine is out now! And it features an article about the latest developments of AutoDock-GPU, the GPU-accelerated molecular docking application we developed in collaboration with the ForliLab at Scripps Research.

This article describes how AutoDock-GPU helps improving the processing speed of drug discovery simulations, as well as how the AutoDock-GPU’s code has been set to work on computers all over the globe, ranging from Rasberry Pis to servers equipped with high-end GPUs. This is thanks to the recent efforts by Scripps Research and the World Community Grid, which have enabled the use of AutoDock-GPU in the OpenPandemics: COVID-19 project.

Enjoy reading the full HiPEAC info 64 magazine!

By Dr.-Ing. Leonardo Solis-Vasquez, 18.10.2021

-

Two ESA papers get accepted at H2RC 2021

We are very happy to announce that two submitted papers by our group have been accepted for presentation at H2RC 2021.

The first paper entitled Near Data FPGA-Accelerated Processing of Collective and Inference Operations in Disaggregated Memory Systems – by Carsten Heinz and Andreas Koch – realizes an FPGA-based disaggregated system that extends distributed memory controllers with hardware-accelerated compute capabilities. This work provides a system capable of performing Near-Data Processing (NDP) operations, as well as an automated tool flow aimed for high usability of the proposed technology, even to users unfamiliar with hardware design.

The second paper entitled Optimizing a Hardware Network Stack to Realize an In-Network ML Inference Application – by Marco Hartmann, Lukas Weber, Johannes Wirth, Lukas Sommer, and Andreas Koch — integrates into the open-source TaPaSCo framework, a high-throughput hardware network stack, which can operate at or close to theoretical performance in a network-attached machine learning inference appliance. Furthermore, this work provides a library of easy-to-use design primitives for network functionality, and thus, aims to facilitate the development of network-attached FPGA-based accelerators.

Good work everyone!

By Dr.-Ing. Leonardo Solis-Vasquez, 1.10.2021

-

ESA paper gets accepted at IA^3 2021

We are very happy to announce that our submitted paper has been accepted for presentation at IA^3 2021.

This paper entitled Mapping Irregular Computations for Molecular Docking to the SX-Aurora TSUBASA Vector Engine – by Leonardo Solis-Vasquez, Erich Focht, and Andreas Koch – is a result of the collaboration with NEC Deutschland GmbH.

This work leverages the vector processing capabilities of the SX-Aurora TSUBASA to efficiently perform molecular docking computations. As a result, docking executions on the Vector Engine (VE) are around 3x faster than a CPU server equipped with 128 cores. Furthermore, in certain cases, the VE achieves comparable performance to a V100 GPU, even though the latter device uses newer chip fabrication technology compared to the VE.

Good work everyone!

By Dr.-Ing. Leonardo Solis-Vasquez, 27.09.2021

-

Open position "LLVM / MLIR dialect development" (student assistant, all genders)

We have an open position for a student assistant (all genders) to help us with the design and implementation of an MLIR dialect to represent a domain-specific language. If you are interested in gaining practical experience with the state-of-the-art compiler framework, and passionate about compiler hacking in general, this is the job for you.

For more details, have a look at the job offer, and send your applications (or questions!) to Julian Oppermann.

By Dr.-Ing. Julian Oppermann, 7.07.2021

-

ESA wins Best Paper Award at DASIP 2021

Our work DExIE - An IoT-Class Hardware Monitor for Real-Time Fine-Grained Control-Flow Integrity has won a Best Paper Award at DASIP2021. We are extremely happy. Thanks to the committee for selecting our work!

Congratulations also to the other nominees on their excellent work!

By Christoph Spang, 2.02.2021

-

ESA wins Best Paper Award at FCCM 2020

We are extremely happy that our work Comparison of Arithmetic Number Formats for Inference in Sum-Product Networks on FPGAs together with our colleague Martin Kumm has won the Best Paper Award at this year’s FCCM2020. Thanks to the committee for selecting our work!

Congratulations also to the other nominees on their excellent work!

Unfortunately, the Corona pandemic did not allow us to present our paper in person, but a video of the talk is available for free at the FCCM virtual conference, where you can also find talks and forums for all other papers accepted at FCCM.

By Dr.-Ing. Lukas Sommer, 5.05.2020

-

First public release of lectureStudio available!

We have been developing and using our tool lectureStudio for lecture recordings for many years now. After a phase of intensive beta-testing, we are releasing the first public version today! We hope that the tool will help many people to set up alternative e-learning formats in these challenging times, where the Corona-pandemic does not allow us to come together in person to give lectures.

lectureStudio does not only provide an easy-to-use interface for lecture recordings, but also allows to augment slides during the lecture with free-hand drawings and highlighting. Next to that, lectureStudio comes with a number of interesting features for interactive lectures, such as messaging or quizzes.

lectureStudio is free to use and we will open-source its source-code in the near future. You can find installers and documentation on the software page.

By Dr.-Ing. Lukas Sommer, 23.04.2020

-

Paper accepted for FCCM 2020

Our work titled Comparison of Arithmetic Number Formats for Inference in Sum-Product Networks on FPGAs has been accepted for publication at FCCM2020. The paper investigates the suitability of three different hardware arithmetic formats for the implementation of FPGA-based hardware accelerators for inference in Sum-Product Networks. This work integrates with our previous work on hardware accelerators presented at TPM2018, ICCD2018, FPT2019 and H2RC2019.

Next to researchers from ESA, our former colleague and now professor at HS Fulda, Martin Kumm, contributed to this work. We would also like to thank our colleagues Alejandro Molina and Kristian Kersting from the Machine Learning Lab at TU Darmstadt.

As FCCM will be held as virtual event this year, we will provide a recording of the paper talk in May.

By Dr.-Ing. Lukas Sommer, 27.03.2020

-

Open PhD Positions

We are currently actively looking to hire a Ph.D. student (Wissenschaftliche/r Mitarbeiter/in) of any gender to do research on extending RISC-V processors. More information is available here

By Prof. Dr-Ing. Andreas Koch, 18.12.2019

-

Open position for a student assistant (all genders)

The Embedded Systems and Applications Group (ESA) at TU Darmstadt currently has an open position for a student assistant (all genders). ESA is looking for a student who will support the team in a new project by developing Machine Learning (ML) solutions for practically relevant applications as benchmarks for acceleration toolflows on multiple platforms (CPU, GPU, FPGA).

For more details, have a look at the job offer and contact Lukas Sommer in case of any questions.

By Dr.-Ing. Lukas Sommer, 17.12.2019

-

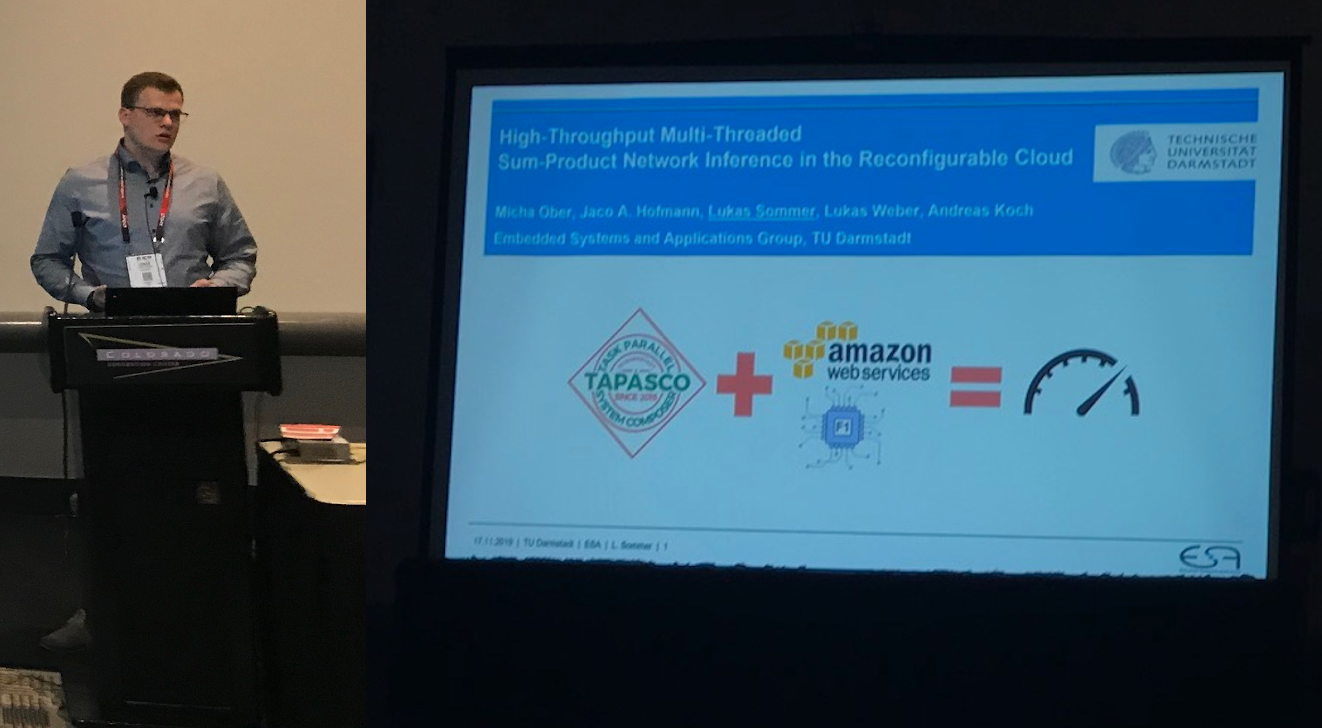

Presentation at H2RC 2019

At the Heterogeneous High-performance Reconfigurable Computing workshop (H2RC 2019), Lukas Sommer presented our paper High-Throughput Multi-Threaded Sum-Product Network Inference in the Reconfigurable Cloud, authored by Micha Ober, Jaco Hofmann, Lukas Sommer, Lukas Weber and Andreas Koch.

In this work, we presented an extension of our TaPaSCo open-source framework to F1 instances available in Amazon’s AWS EC2 cloud. To demonstrate the potential of this platform, we ported our Sum-Product Accelerator to the reconfigurable cloud.

Users interested in using TaPaSCo for AWS EC2 F1 instances can track the status of the integration into mainline TaPaSCo in the TaPaSCo wiki.

By Dr.-Ing. Lukas Sommer, 17.11.2019

-

Julian Oppermann defends his Ph.D.-thesis

On October 30th, 2019 Julian Oppermann successfully defended his Ph.D.-thesis Advances in ILP-based Modulo Scheduling for High-Level Synthesis. In his work, Julian was able to significantly advance the state-of-the-art in modulo scheduling for High-Level Synthesis.

Congratulations to Dr.-Ing. Julian Oppermann!

By Dr.-Ing. Lukas Sommer, 30.10.2019

-

Leonardo Solis-Vasquez defends his Ph.D.-thesis

On October 14th, 2019 Leonardo Solis-Vasquez successfully defended his Ph.D.-thesis entitled Accelerating Molecular Docking by Parallelized Heterogeneous Computing - a Case Study of Performance, Quality of Results, and Energy-Efficiency using CPUs, GPUs and FPGAs. In his work, Leonardo contributed accelerated implementations for GPUs and FPGAs to AutoDock, a framework for molecular docking in drug design.

Congratulations to Dr.-Ing. Leonardo Solis-Vasquez!

By Dr.-Ing. Lukas Sommer, 14.10.2019

-

Two papers accepted for FPT 2019

Two submissions by ESA have been accepted for publication at FPT 2019.

The first paper by Julian Oppermann, Lukas Sommer, Lukas Weber, Melanie Reuter-Oppermann, Andreas Koch and Oliver Sinnen is titled SkyCastle: A Resource-Aware Multi-Loop Scheduler for High-Level Synthesis. In this paper, we developed a resource-aware approach to modulo-scheduling, that integrates allocation and scheduling into a single formulation. This allows to optimize performance by pipelining multiple loops in a kernel while maintaining a given resource allocation.

The second paper by Lukas Weber, Lukas Sommer, Julian Oppermann, Alejandro Molina, Kristian Kersting and Andreas Koch is titled Resource-Efficient Logarithmic Number Scale Arithmetic for SPN Inference on FPGAs. As part of this work, we developed hardware arithmetic operators using the so-called Logarithmic Number System (LNS) for Sum-Product Network inference on FPGAs. In this use-case, the use of LNS allows to save a significant amount of hardware resources while maintaining sufficient accuracy.

By Dr.-Ing. Lukas Sommer, 8.10.2019

-

Paper accepted for ReConFig 2019

The paper titled A Catalog and In-Hardware Evaluation of Open-Source Drop-In Compatible RISC-V Softcore Processors by Carsten Heinz, Yannick Lavan, Jaco Hofmann and Andreas Koch has been accepted for presentation at ReConFig 2019.

Carsten and his team developed a catalog of open-source RISC-V cores for use with our TaPaSCo framework and conducted an extensive evaluation of these cores on different platforms.

The catalog of RISC-V cores and the wrappers for TaPaSCo are publicly available on Github.

By Dr.-Ing. Lukas Sommer, 30.09.2019

-

Termin und Raum AER Klausur 2019

Die Klausur findet dieses Mal in Raum S202/C205 statt. Beginn ist am 23.07.2019 um 12 Uhr.

By Dr.-Ing. Jaco Hofmann, 14.07.2019

-

Paper accepted for EMSoft

As part of the EPHoS-project together with FAT, we have created a collection of benchmark kernels, which allow to assess the performance of different parallel programming models on embedded platforms, such as Nvidia Jetson.

A paper about this benchmark suite has now been accepted for presentation at EMSoft as part of ESWeek 2019 in New York. Together with the paper, we will release our benchmark suite as open-source software on our Github page, so stay tuned!

By Dr.-Ing. Lukas Sommer, 10.07.2019

-

Report of the EPHoS project available

Throughout the last year, we have been collaborating with the Forschungsvereinigung Automobiltechnik(FAT) to investigate how established parallel programming models from the HPC-domain such as OpenMP, CUDA and OpenCL can be used to parallelize critical workloads in tomorrow’s automotive vehicles.

The report of the project is now available for download as volume 317 of the FAT Schriftenreihe.

By Dr.-Ing. Lukas Sommer, 1.07.2019

-

TaPaSCo at ISC 2019

Upon invitation by the HiPEAC network, we presented our open-source framework TaPaSCo at ISC-HPC 2019.

Thanks to everyone who stopped by at the booth to learn about how TaPaSCo can help them to build a heterogeneous accelerator SoC for datacenter workloads!

By Dr.-Ing. Lukas Sommer, 17.06.2019

-

Release of TaPaSCo version 2019.6

In time for ISC-HCP 2019 we have completed the release of TaPaSCo version 2019.6 today!

The release contains a whole lot of new features for the TaPaSCo toolflow and improvements to make bitstream generation faster and more configurable.

Check out the release notes on Github for the full list of new features and improvements.

Also, don’t forget to visit us at booth A-1414 on ISC-HPC on Monday afternoon!

By Dr.-Ing. Lukas Sommer, 14.06.2019

-

Release of TaPaSCo version 2018.2

We have just completed the release of TaPaSCo version 2018.2! The new release bundles the work of almost one year and contains numerous new features, platforms (Virtex Ultrascale+, Alveo, …) and stability improvements.

Check out the release on Github to find more information about the new features and download TaPaSCo.

By Dr.-Ing. Lukas Sommer, 14.05.2019

-

Paper accepted for Euro-Par 2019

Our paper titled “Design-Space Exploration with Multi-Objective Resource-Aware Modulo Scheduling” was accepted for publication at Euro-Par.

The paper proposes a new approach for design-space exploration of custom hardware implementations by combining resource allocation and modulo scheduling. Using problem-specific rules, we were able to exclude obviously dominated solutions from the design space before scheduling and synthesis. The evaluation shows the benefits of our approach regarding runtime at the design level when compared to a standard, multi-criteria optimisation method.

By Dr.-Ing. Julian Oppermann, 10.05.2019

-

PANDAS project kickoff

Today marks the start of the new PANDAS project as part of ESA’s research. The goal of PANDAS (Programmable Appliance for Near-Data processing Accelerated Storage) is to develop a new, smart mass storage card. By combining large numbers of flash memories and programmable logic (FPGAs), critical applications can be accelerated using near-data processing. The resulting PANDAS card is mainly intended for usage with database (e.g. RocksDB) systems, but should be usable with a large variety of applications.

As part of PANDAS, we also welcome Lukas Weber as the newest member of the ESA team. Lukas has previously been with ESA as a student research assistant and during his master thesis.

By Dr.-Ing. Lukas Sommer, 1.05.2019

-

TaPaSCo article in HiPEAC info 57

HiPEAC info 57 is out and it features an article about our open-source framework TaPaSCo. Check out the article to learn how TaPaSCo can support you when you need to build an FPGA-based heterogeneous system from your accelerator and want to interface it from software.

You can find even more information about TaPaSCo in the recent paper and on Github.

By Dr.-Ing. Lukas Sommer, 15.04.2019

-

TaPaSCo tutorial @ ARC 2019

Part of the ARC2019 symposium hosted by ESA was a tutorial about our open-source framework TaPaSCo.

In a combination of short presentations and hands-on sessions, the tutorial covered all necessary steps of the design process for a heterogeneous SoC with TaPaSCo. More than 25 participants of ARC took the opportunity to learn about how the TaPaSCo framework can help them in their every-day research.

The whole tutorial was recorded and we will make a complete video available soon, together with the materials from the tutorial.

If you want to learn more about TaPaSCo, check out the paper or TaPaSCo on Github.

By Dr.-Ing. Lukas Sommer, 11.04.2019

-

ARC 2019 hosted by ESA

From April 9th to April 11th 21019, ESA was host to the 25th edition of the International Symposium on Applied Reconfigurable Computing (ARC).

More than 50 researchers from all over the world gathered in Darmstadt to discuss new architectures and innovative applications for reconfigurable computing. Also part of the conference were two socials events, a guided tour through GSI Helmhotz Zentrum and an interesting visit to ESOC, followed by the conference dinner.

A big thank you to all participants, who made this an interesting conference, and all people involved in the organization of the event!

By Dr.-Ing. Lukas Sommer, 10.04.2019

-

ESA @ EuroLLVM 2019

The 2019 European LLVM developer’s meeting saw two contributions by students from ESA.

Michael Halkenhäuser successfully participated in the student research competition. As part of the competition, he presented the results of his bachelor thesis, supervised by Lukas Sommer. In this thesis, Michael has developed an alternative OpenMP backend for the polyhedral compilation infrastructure polly, which can act as an drop-in replacement for the existing OpenMP backend. Michael’s new backend was able to achieve significant speedups over the old backend and is now part of the polly project. Take a look at the recording of his talk, to find out more about his work.

Robin Kruppe gave a talk together with Roger Espasa from Esperanto Technologies, presenting details on the RISC-V vector extensions and the current status of support in LLVM. In his job as student assistant at ESA, Robin is doing important work to support code-generation for the RISC-V vector extension as part of the LLVM project. A recording of this talk is also available on YouTube.

By Dr.-Ing. Lukas Sommer, 9.04.2019

-

Robin Kruppe wins CGO 2019 Student Research Competition

ESA is proud to announce that our student Robin Kruppe has won the gold medal (graduate category) in this year’s CGO student research competition.

In his work titled “Extending LLVM for Lightweight SPMD Vectorization: Using SIMD and Vector Instructions Easily From Any Language”, Robin presented the results of his bachelor thesis, which was supervised by Julian Oppermann. In his thesis, Robin extended the auto-vectorization of LLVM for architectures supporting masked SIMD-instructions (e.g. Nyuzi) and exposed the vectorization interface via LLVM intrinsics.

Congratulations to Robin on this great achievement!

By Dr.-Ing. Lukas Sommer, 20.02.2019